# X-RAY DIFFRACTION TECHNIQUES FOR FUTURE ADVANCED CMOS METROLOGY CHALLENGES

by

Chiu Soon Wong, M.Sc.

A thesis submitted to the School of Electronic Engineering

In conformity with the requirements for

the degree of Doctor of Philosophy (Ph.D.)

**Dublin City University**

Dublin, Ireland.

(July, 2013)

Supervised by

Prof. Patrick J. McNally

**Declaration**

I hereby certify that this material, which I now submit for assessment on the programme of

study leading to the award of Ph.D. is entirely my own work, that I have exercised reasonable

care to ensure that the work is original, and does not to the best of my knowledge breach any

law of copyright, and has not been taken from the work of others save and to the extent that

such work has been cited and acknowledged within the text of my work.

| Signad: | <br>(Candidata) |

|---------|-----------------|

| Signea: | <br>Candidate   |

ID No.: 59102268

Date:

ii

#### **Abstract**

Traditional Si CMOS scaling following Moore's Law is becoming increasingly difficult as physical limits are approached at sub-20 nm nodes and beyond. A significant issue is the limited charge carrier mobility in Si, and so new channel materials that carry relatively higher mobility carriers have been used, such as strained Si. Other materials such as III-V and germanium (Ge) are currently under consideration for replacing the conventional Si channel for future generations of low power and high speed electronics. However, challenges still remain with the realisation of high quality III-V material on Si for CMOS devices fabrication because the tolerance to dislocations is very low (<10<sup>5</sup> cm<sup>-2</sup>). In order to overcome this problem, a non-destructive X-ray characterisation routine which can be used to effectively help III-V growers identify various issues associated with heteroepitaxial growth of III-V materials and which delivers useful experimental feedback to growers for material quality optimisation has been designed. The feasibility of this routine has been demonstrated through the characterisation of a series of deliberately fabricated "problematic" heteroepitaxial GaAs materials.

According to industry experts, the future of modern nanoelectronics may well also depend on a second trend, which is the implementation of diverse functionality within modern ICs. This "More than Moore" (MtM) approach will be realised through the manufacture of complex Systems on Chip (SoC) and Systems in Package (SiP), evolving towards fully three-dimensional ICs (3-D ICs). However, progress in this direction is hampered by the lack of a compelling metrology in order to measure non-destructively and *in situ* the process induced warpage, strain and other defects inside silicon die, a problem which has been highlighted by the International Technology Roadmap for Semiconductors (ITRS). Therefore, the second aim of this thesis has been the development of a novel laboratory-based technique called X-ray diffraction 3-dimensional surface modelling (XRD/3DSM) in order to address this major stumbling block in the development of MtM integrated circuit technology.

#### Acknowledgements

I would like to express my deepest thanks to my supervisor, Prof. Patrick J. McNally for his sincere guidance and supervision throughout this work. He has afforded me the opportunity for my academic advancement.

My sincere thanks to Dr. Nick Bennett - as the post doctoral researcher on the project.

He was the person who has provided valuable advice and guidance throughout this research work. This project would not have been carried out smoothly without his assistance.

I wish to thank to Dr. Ken Horan and Dr. Lisa O'Reilly for the HR-XRD difftractometry training. Many thanks to Dr. Jennifer Stopford who has trained me on the micro-Raman instrument and provided valuable guidance on the evaluation of SXRT images. Special thanks to Dave Allen, Dr. Nick Bennett, Dr. Aidan Cowley and Dr. Andreas Danilewsky for their tutoring and valuable guidance during the SXRT measurements performed at ANKA and Hasylab beamlines.

Thanks to Dr. Paloma Tejedor, Dr. Marcos Benedicto, and Dr. Beatriz Galiana for providing GaAs samples and performing AFM measurements for me. Also, special thanks to Dr. Jon Molina who has performed TEM measurements on GaAs samples for this work. I would like to thank Dr. Dionysios Manessis, IZM Fraunhofer, Berlin, for providing the QFN packages used in the development of XRD/3DSM technique.

Apart from that, I would like to thank Rajani, Jithin, Dave, Tomonori, Declan, Kalid, Evgueni, and Yang for their encouragement during the course of this work.

Lastly, I would like to thank my family for their unconditional love, encouragements and support.

### **Table of Contents**

| Declaration                                                                      | ii  |

|----------------------------------------------------------------------------------|-----|

| Abstract                                                                         | iii |

| Acknowledgements                                                                 | iv  |

| Chapter 1 Introduction                                                           | 1   |

| 1.1 Complementary metal-oxide-semiconductor (CMOS) field-effect transistor (FET) |     |

| scaling                                                                          | 1   |

| 1.1.1 Moving towards "More Moore" and "More than Moore" technologies             | 3   |

| 1.2 Scope of this thesis                                                         | 10  |

| 1.3 Characterisation methodology                                                 | 11  |

| i) Characterisation of heteroepitaxial growth of III-V materials                 | 11  |

| ii) Lab-based X-ray diffraction 3-dimensional surface modelling (XRD/3DSM)       | 12  |

| 1.4 Project Layout                                                               | 14  |

| Chapter 2 Characterisation Methodology and Instrumental Setup                    | 16  |

| 2.1 Introduction                                                                 | 16  |

| 2.2 X-Ray diffraction (XRD)                                                      | 16  |

| 2.2.1 Fundamentals of X-ray diffraction                                          | 16  |

| 2.2.2 Diffraction in reciprocal space                                            | 17  |

| 2.3 Powder X-ray diffraction (XRD)                                               | 20  |

| 2.3.1 Crystallographic texture mapping                                           | 21  |

| 2.4 High-resolution X-ray diffraction (HR-XRD)                                   | 25  |

| 2.4.1 HR-XRD experimental geometry                                               | 26  |

| 2.4.2 High-resolution XRD rocking curves and $\omega$ -2 $\theta$ scans          | 26  |

| 2.4.3 HR-XRD analysis by RADs simulations                                        | 28  |

| 2.4.4 Reciprocal space mapping                                                   | 31  |

| 2.4.5 X-ray diffraction instrument set-up.                                       | 32  |

| 2.5 White Beam Synchrotron X-ray Topography (SXRT)                               | 39  |

| 2.5.1 Synchrotron Radiation X-ray Source                                         | 40  |

| 2.5.2 Experimental geometry                                                      | 42  |

| 2.5.3 The resolution of SXRT                                                     | 44  |

| 2.5.4 Penetration depth calculation                                              | 45  |

| 2.5.5 Dislocation density estimation                                             | 47  |

| 2.6 Micro-Raman Spectroscopy                                                     | 47  |

| 2.6.1 The mechanism of light scattering                                          | 47  |

| 2.6.2 Raman selection rules in backscattering geometry                           | 50  |

| 2.6.3 Raman spectrum                                                             | 52  |

| 2.6.4 Frequencies of Raman peaks                                                     | 53    |

|--------------------------------------------------------------------------------------|-------|

| 2.6.5 Probe depth of the laser light                                                 | 54    |

| 2.6.6 Spatial resolution of a Raman microscope                                       | 54    |

| 2.6.7 Micro-Raman spectroscopy experimental setup                                    | 55    |

| 2.7 Photoluminescence                                                                | 57    |

| 2.7.1 Photoluminescence spectroscopy experimental setup                              | 59    |

| 2.8 Transmission Electron Microscopy (TEM)                                           | 59    |

| 2.8.1 Experimental geometry of TEM                                                   | 60    |

| 2.9 Atomic force microscopy (AFM)                                                    | 61    |

| Chapter 3 The challenges facing high quality GaAs heteroepitaxy on Si substrates     | 63    |

| 3.1 Introduction                                                                     | 63    |

| 3.2 Difficulties for heteroepitaxial growth of GaAs on Si substrates                 | 63    |

| 3.2.1 Incompatibility of the polar/non-polar substrate                               | 64    |

| 3.2.2 The discrepancy of the thermal expansion coefficients                          | 66    |

| 3.2.3 Lattice mismatch                                                               | 68    |

| 3.3 Defect density reduction via epitaxial lateral overgrowth (ELO)                  | 71    |

| 3.3.1 Further defect density reduction by nanoscale ELO structures                   | 73    |

| Chapter 4 Characterisation of MOVPE-Grown GaAs on Ge or Si substrates                | 76    |

| 4.1 Introduction                                                                     | 76    |

| 4.2 Growth of GaAs heteroepitaxial layers                                            | 77    |

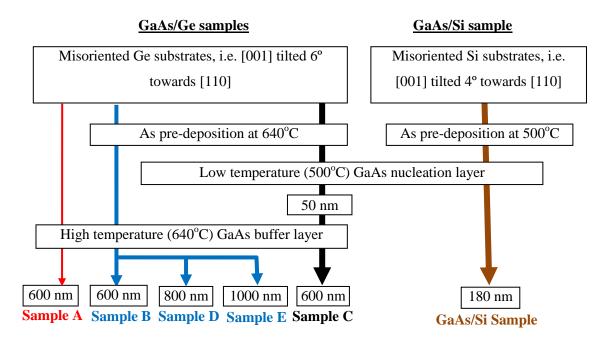

| 4.2.1 Growth of GaAs/Ge samples                                                      | 77    |

| 4.2.2 Growth of a GaAs/Si sample                                                     | 80    |

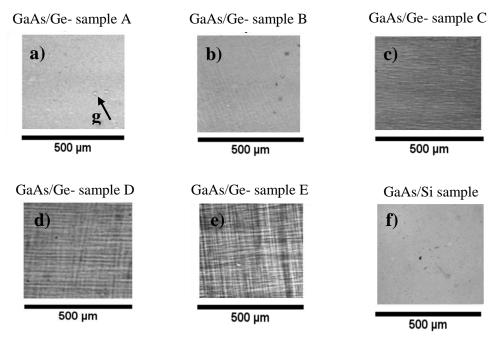

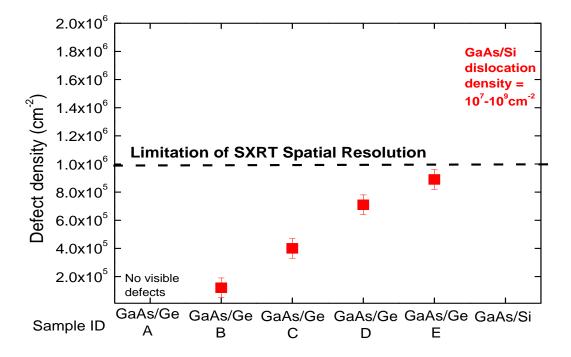

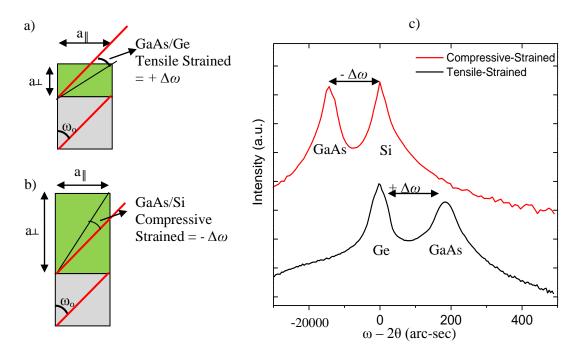

| 4.3 Evaluation of the dislocation density by SXRT                                    | 82    |

| 4.4 Evaluation of the strain relaxation process by high-resolution X-ray diffraction |       |

| (HRXRD)                                                                              | 85    |

| 4.4.1 Preliminary investigation using 004 $\omega$ -2 $\theta$ scan                  | 85    |

| 4.4.2 Evaluation of degree of relaxation using reciprocal space mapping (RSM)        | 88    |

| 4.4.3 Strain/relaxation and crystallinity evaluation of the defective GaAs/Si sample | le 92 |

| 4.5 X-ray diffraction investigation of antiphase domains                             | 99    |

| 4.5.1 The influence of various growth routines on APD self-annihilation in GaAs,     | /Ge   |

| crystals                                                                             | 102   |

| 4.5.2 Interaction between misfit dislocations and antiphase boundaries               | 108   |

| 4.6 Investigation of crystallographic tilt in GaAs heteroeptiaxy layers              | 109   |

| 4.7 Surface quality investigation by μ-Raman spectroscopy and photoluminescence      | 114   |

| 4.7.1 Comparison between MOVPE grown GaAs on Ge and Si substrates                    | 117   |

| 1.8 Summery                                                                          | 110   |

| Chapter 5 Overview of Integrated Circuit (IC) Packaging Technology and Development of | of    |

|---------------------------------------------------------------------------------------|-------|

| Lab-Based X-ray Diffraction 3-Dimensional Surface Modelling (XRD/3DSM)                | 121   |

| 5.1 Introduction                                                                      | 121   |

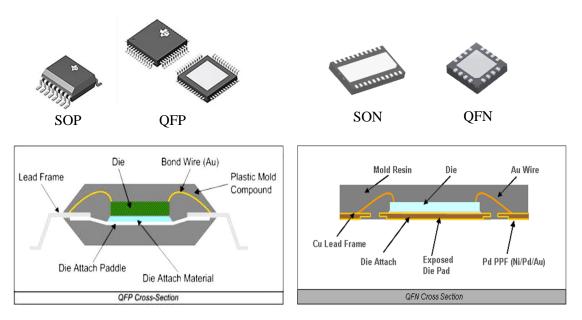

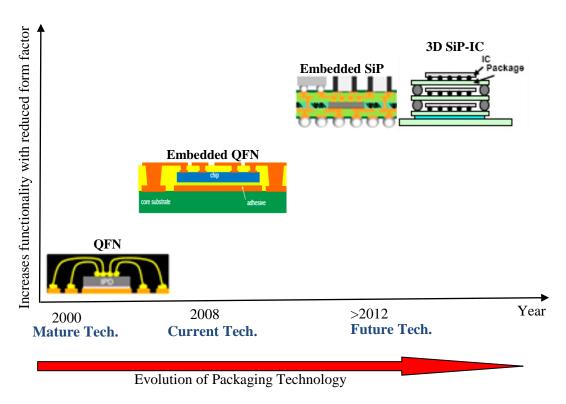

| 5.2 Overview of IC packaging technology                                               | 121   |

| 5.3 Development of a lab-based XRD/3DSM technique                                     | 127   |

| 5.3.1 004 Rocking curves                                                              | 129   |

| 5.3.2 Obtaining a series of spatially resolved FWHM line scans                        | 130   |

| 5.3.3 Importing data into Solidworks <sup>TM</sup>                                    | 131   |

| 5.3.4 Data reconstruction by Solidworks <sup>TM</sup>                                 | 133   |

| 5.4 In Situ XRD Annealing Experiments                                                 | 134   |

| 5.5 Summary                                                                           | 136   |

| Chapter 6 Characterisation of Die Stress and Warpage Inside Commercially Available    |       |

| Ultrathin-QFN Packages                                                                | 137   |

| 6.1 Introduction                                                                      | 137   |

| 6.2 UQFN packages                                                                     | 137   |

| 6.3 Characterisation of die stress inside UQFN packages                               | 138   |

| 6.3.1 Lab-based XRD/3DSM                                                              | 138   |

| 6.3.2 Synchrotron X-ray topography (SXRT)                                             | 141   |

| 6.3.3 In Situ XRD annealing experiments                                               | 145   |

| 6.3.4 Stress estimation                                                               | 147   |

| 6.3.5 Finite element analysis (FEA)                                                   | 149   |

| 6.4 Summary                                                                           | 157   |

| Chapter 7 Characterisation of Die Stress and Warpage in Embedded Quad-Flat No-Lead    |       |

| (QFN) Packages                                                                        | 158   |

| 7.1 Introduction                                                                      | 158   |

| 7.2 Embedded QFN packages                                                             | 158   |

| 7.3 Characterisation of die stress and warpage inside embedded QFN packages for sele  | ected |

| chip manufacturing process steps                                                      | 160   |

| 7.3.1 Copper metallisation                                                            | 161   |

| 7.3.2 Structuring of conductor lines                                                  | 167   |

| 7.4 Summary                                                                           | 170   |

| Chapter 8.                                                                            | 172   |

| 8.1 Conclusions                                                                       | 172   |

| 8.2 Future Work                                                                       | 179   |

#### **List of Abbreviations**

AFM Atomic force microscopy

APB Anitphase boundary

APD Antiphase domain

CMOS Complementary metal-oxide-semiconductor

CTE Coefficient of thermal expansion

ELO Epitaxial lateral overgrowth

FET Field-effect transistor

FWHM Full-widths-at-half-maximum

FCC Face-centred-cubic

FEA Finite element analysis

GaAs Gallium arsenide

GaSb Gallium antimonide

Ge Germanium

GOF Goodness-of-fit

HR-XRD High-resolution X-ray diffraction

IC Integrated circuit

ITRS International technology roadmap for semiconductors

InSb Indium antimonide

InAs Indium arsenide

IP Intellectual property

LABR Large area back reflection topograph

LAT Large area transmission topograph

LPE Liquid phase epitaxy

MBE Molecular beam epitaxy

MCE Microchannel epitaxy

MM More Moore

MOVPE Metalorganic vapour phase epitaxy

MtM More than Moore

PCB Printed circuit board

PL Photoluminescence

QFN Quad flat no-lead package

QFP Quad flat package

QW Quantum-well

RADs Rocking-curve analysis software

RC Rocking curve

RF Radio frequency

RSM Reciprocal space mapping

Si Silicon

SiP System in package

SoC System on chip

SXRT Synchrotron X-ray topography

TEM Transmission electron microscopy

UQFN Ultra-thin quad flat no-lead package

μ-Raman Micro-Raman

XRD X-ray diffraction

XRD/3DSM X-ray diffraction 3-dimensional surface modeling

2D 2-Dimensional

3D 3-Dimensional

#### Chapter 1

#### Introduction

## 1.1 Complementary metal-oxide-semiconductor (CMOS) field-effect transistor (FET) scaling

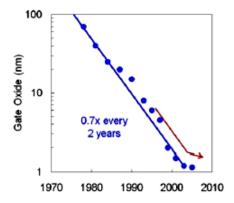

Since the early 1970s, the dimensions of CMOS transistors have been aggressively downscaled, successfully enhancing the performance of transistors by about 30-35% for each new generation of CMOS technology. This Si CMOS scaling is described by Moore's law [1-5], where transistor size shrunk at the rate of ~0.7x for each generation, down to the technology node of 130 nm. The traditional scaling process has apparently slowed down as it reached the 90 nm CMOS generation node [1-5], largely due to issues with the gate dielectric (silicon dioxide, SiO<sub>2</sub>) becoming physically too thin. The restriction on the SiO<sub>2</sub> thickness approached the 1.2 nm limit as illustrated in Fig. 1.1. Reducing the oxide thickness more would mean a prohibitively large gate leakage current arises as a consequence of the direct tunnelling across the relatively thin gate oxide [4, 6].

#### Gate Oxide Thickness

Figure 1.1 Gate oxide thickness scaling. Traditional scaling slackened at the 90 nm technology node [4].

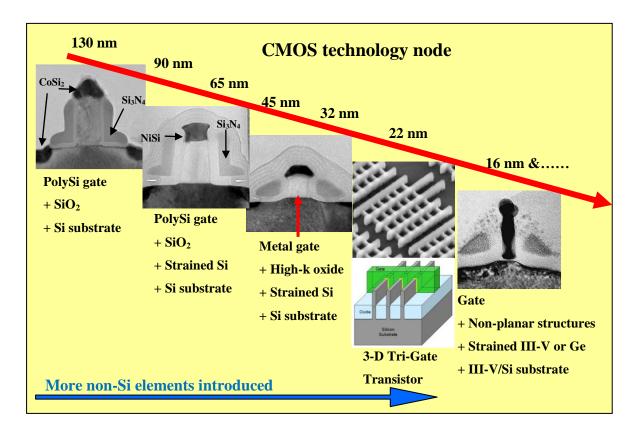

In 2007, Intel announced the first 45nm generation of transistor technology by introducing a revolutionary high-k metal-gate transistor in cooperation with strained Si technology. This new technology improved the performance of the device by approximately 23 % compared to the 65 nm node [2, 4]. The significant improvement is due to the use of a high-k gate that enabled a >25x gate leakage reduction, in addition to mobility advantages offered by strained Si [4]. If Moore's law continues, it will need further new materials as substitutes for the existing solutions. Overall, the CMOS technology has been through a revolutionary change after the 130 nm node as more chemical elements have been introduced in order to drive the CMOS roadmap forward (see Fig. 1.2), and this is likely to continue in future CMOS technologies [7].

Figure 1.2 The evolution of CMOS technology after the 130 nm technology node [4, 7] (the options for future technologies are subject to change).

#### 1.1.1 Moving towards "More Moore" and "More than Moore" technologies

#### "More Moore"

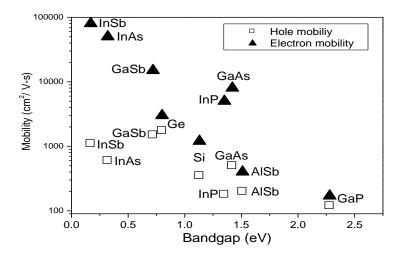

Looking towards future CMOS technology nodes such as the 16 nm node and beyond, the existing technology is insufficient to drive the CMOS roadmap due again to the limited channel mobility in Si MOS devices [8, 9] (see Fig. 1.2). One of the obvious remedies that has been consistently pointed out by the International Technology Roadmap for Semiconductors (ITRS) 2009-2011[8, 9], is to replace the conventional Si or strained Si CMOS channel with alternative materials offering a higher mobility than Si. Channel materials being proposed are Ge and III-V materials [8-11]. Considering the high electron mobility exhibited by III-V materials compared to Si, these materials are amongst the best alternative channel materials to bring about the mobility improvement for n-MOSFETs. In addition, III-V materials have remarkable optical properties: the III-V direct band gap allows a more efficient photon creation/conversion than in Si. Therefore, more functionality (optoelectronic devices) can be added to conventional logic functions on the same Si platform. Fig. 1.3 shows a plot of carrier mobility as a function of energy band gap for numerous semiconductor materials [8]. III-V compound semiconductors such as indium antimonide (InSb), indium arsenide (InAs), gallium antimonide (GaSb) and gallium arsenide (GaAs) possess comparatively higher electron mobility than that of Si. Although InSb and InAs possess the highest electron mobility, they are not the ideal choice of n-channel materials because of their narrow energy band gaps, as they are more susceptible to thermal generation of excess carriers, thus resulting in current leakage [8]. By forming the III-V ternary semiconductors (i.e. InGaAs, InAsSb and InGaSb), one can avail of a wide selection of composition and energy band gap for n-channel FET applications while simultaneously maintaining their superior electron mobility. In particular, a very high-speed InGaAs quantum-well (QW) transistor has been demonstrated at an operating voltage of only 0.5 V

[12, 13]. These have made III-V materials a promising material choice for future high-speed logic applications as they give rise to high transistor drive current in addition to ensuring low gate delay.

Figure 1.3 Carrier mobility as a function of minimum energy band gap for elemental and III-V compound semiconductors [8].

Considering the materials for the p-type channel, both III-Vs (such as InGaAs, InSb, InGaSb, GaAs) and Ge are the primary candidates as they offer significantly higher hole mobility than that of Si [8]. Although, most III-V materials are superior in electron mobility, they are not significantly better in terms of hole mobility. This has been one of the crucial obstacles to be encountered, when identifying a suitable high mobility III-V p-FET candidate in order to balance the mobility between p-and n-channel FETs [14]. Nevertheless, recent works have demonstrated one solution by incorporating strain as a mobility enhancer for both the Ge [15] and III-V materials such as InGaAs and GaSb [16, 17] for p-channel FET applications. That suggests it is possible to further improve the hole mobility of Ge and III-V materials by straining them, but it is yet to be thoroughly investigated.

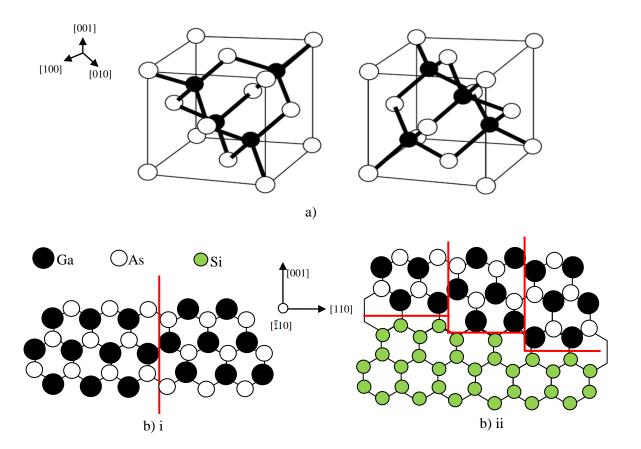

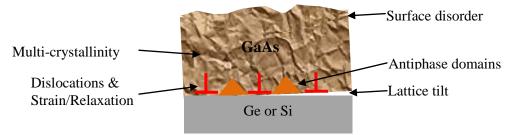

A fundamental requirement for integrating the III-V materials into the channel of a silicon based MOSFET (i.e. onto a silicon substrate), is to produce a suitable platform. Hetero-integration of III-V materials presents several very difficult technological challenges. The key challenge lies in the significant lattice mismatch between the Si substrate and the III-V over-layers, since there is a 4.1% mismatch between Si and GaAs. Large numbers of defects (misfit and threading dislocations) are generated in the epitaxial layers due to the large lattice mismatch [18, 19].

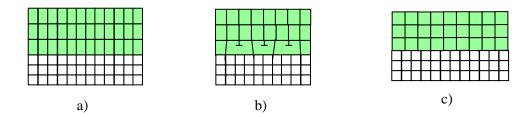

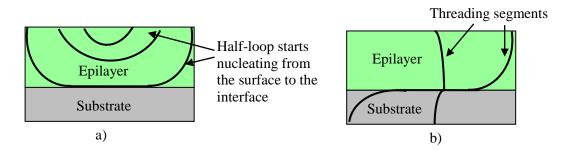

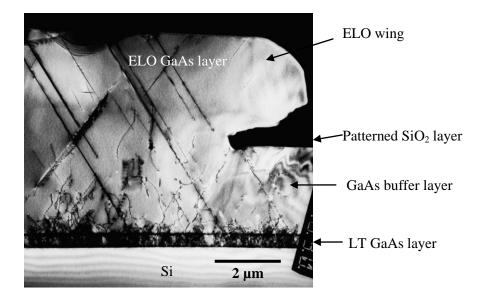

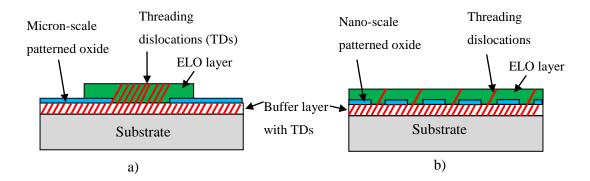

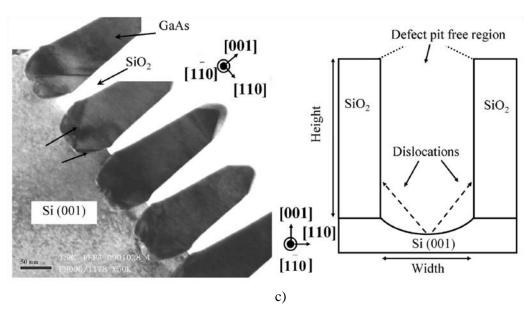

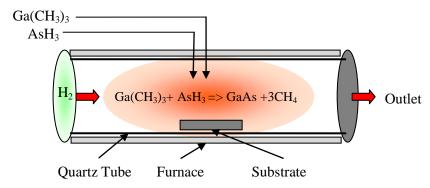

Different growth strategies have been explored to overcome the materials issues associated with GaAs heteroepitaxy on Si. The use of strained or composition-graded buffer layers in combination with thermal annealing have been thoroughly investigated, but the high cost associated with the growth of thick GaAs epilayers and the propagation of dislocations into the active areas of the devices during annealing have hindered its implementation in production [20-22]. Low-temperature growth of GaAs on Si using atomic hydrogen as a surfactant has been shown to reduce significantly the average defect density (10<sup>4</sup> cm<sup>-2</sup>) and enhance the electrical properties of the as-grown film by bending and pinning threading dislocations via modification of the surface energy and growth dynamics. While the relaxation of the lattice mismatch in the early stages of growth is very efficient using this method, it has as the main drawback of poor thermal stability of the resulting GaAs epilayers [23, 24]. One of the most promising alternatives is selective growth of GaAs on patterned Si substrates, also called epitaxial lateral overgrowth (ELO) or microchannel epitaxy (MCE) [25-28]. In this case the silicon substrate is masked with a thin dielectric film and subsequently patterned using lithographic techniques with micron or nanomet scale resolution. Selective nucleation of GaAs in the mask-free Si areas enables lattice mismatch dislocations to be trapped by the mask vertical sidewalls provided the aspect ratio of the opening is sufficiently large. Improvements in defectivity are required as there is an immense

challenge in using III-V material on Si to fabricate CMOS devices because the tolerance to dislocations is very low ( $<10^5$  cm<sup>-2</sup>).

The new materials and device architectures in development, such as hetero-integration of III-V on Si will ultimately provide a route that push CMOS technology scaling forward [4, 9-11]. The extension of CMOS scaling using non-Si materials channels for future high speed and low power logic transistor is labelled by the ITRS as the "More Moore" (MM) approach. However, the most critical issue still remains, i.e. the realisation of high quality III-V materials on Si substrates.

#### "More than Moore"

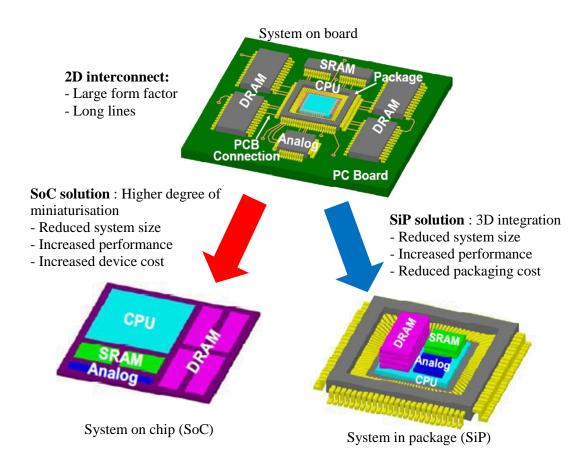

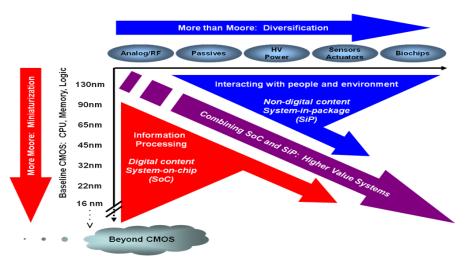

Recently, a second trend called "More than Moore" (MtM) is defined by industry experts, where added value to devices is provided by incorporating functionalities that do not necessarily scale according to Moore's Law [29, 30]. One MtM approach enables the migration of the non-digital components from the printed circuit board (PCB) into a single package containing the integrated circuit (IC). System on chip (SoC), System in Package (SiP) and 3-dimensional (3D) IC technologies provide such a route for the continued improvement in chip performance, with reduced power, cost and size at the system level while the new materials and architectures that can support Moore's Law scaling, are not yet ready [4, 30].

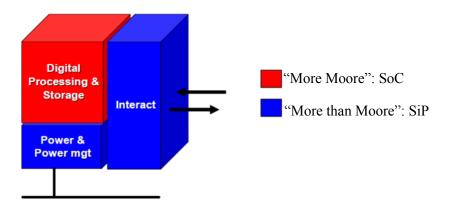

SoC refers to integrating all components of a computer or other electronic system on one silicon platform horizontally (chip), as shown in Fig. 1.4. It may consist of analogue, radio frequency (RF), power sensors as well as passives components to expand the functions/value of the semiconductor chips [29, 31]. This technology not only helps to satisfy the ever-increasing demands for high processing performance, but at the same time ensures a

slim form factor and lower overall power consumption. Nonetheless, the implementation of SoC technology is hampered by the long design times due to integration complexities, high wafer fabrication costs, test costs, and mixed-signal processing complexities requiring dozens of mask steps and intellectual property (IP) issues [31, 32].

Figure 1.4 The concept of SoC and SiP: migration from the system board level onto the chip (SoC) or into the package (SiP) [9, 33].

Therefore, a new paradigm called system-in-package (SiP) is being innovated to overcome the shortcoming of the SoC approach. This is due mainly to the capabilities of SiP to integrate several either already existing, and/or dedicated dies, together to create a new function without having to pay for long product development times and very expensive mask

sets [31, 32]. These materials, technologies and functional components on different dies can be connected in 3-dimensions by vertically stacking each layer one on top of another in the same package (see Fig. 1.4), enabling the continued increase in functional density and decrease in cost per function required to maintain the progress in cost and performance for electronics, such as for mobile communications markets [9, 32].

The core innovation of SiP technology is not for the replacement of SoC technology, but it is in fact the heterogeneous integration of digital and non-digital functionalities into compact systems as illustrated in Fig. 1.5 [29]. This is particularly important for future multifunctional systems as they will require not only more signal and data processing power, but also require the interaction with the outside world via an appropriate transducer, such as sensors and actuators. This implies that future highly integrated systems (advanced SoC/SiP systems) will comprise of both SoC ("More Moore") and SiP ("More than Moore") components in which SoC components may be viewed as the brain of an intelligent compact system, whereas SiP components will be responsible for interaction with the outside world and users (see Fig. 1.6) [9, 29].

Figure 1.5 The combined need for digital and non-digital functionalities in an integrated system is translated as a dual trend in the ITRS: miniaturisation of the digital functions ("More Moore") and functional diversification ("More than Moore") [29].

Figure 1.6 "More than Moore" technologies complement the digital processing and storage elements of an integrated system in allowing the interaction with the outside world and in powering the system [9, 29].

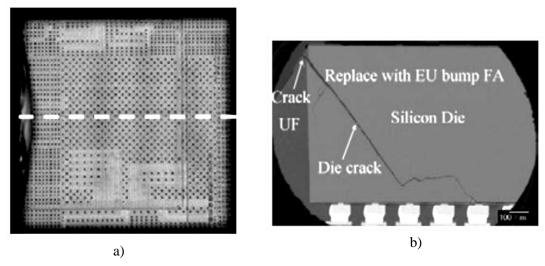

The existing SoC/SiP systems are however plagued by reliability problems as they are not as reliable as traditionally packaged integrated circuit systems. Issues such as electrical, thermal and mechanical stress management are the primary concerns in order to meet the future integration requirements of advanced SoC/SiP systems[32, 34]. Manufacturing-induced thermal stress, created during the fabrication of packaged integrated circuits, can be large enough to induce cracking or interfacial delamination in the package, which could potentially degrade the performance and reliability of the packaged chip, ultimately leading to device failure. However, there are no available laboratory based metrologies that can non-destructively measure or image stress/strain, warpage inside packaged chips or SoC/SiP packages. Therefore, the need to develop non-destructive metrologies that can be used to effectively measure stress/strain in packaged chips or SoC/SiP systems is identified by the ITRS, in both the 2011 and 2009 editions [35, 36]. These non-destructive measurement methodologies will be used to gain a better understanding of the sources and distribution of strain inside the packaged chips or SoC/SiP systems, created

during different packaging or manufacturing processes, and thereby helping to improve the manufacturing efficiency, performance and reliability of advanced packaging products.

#### 1.2 Scope of this thesis

Concerning further miniaturisation by "MM" solutions, one of the obvious tasks is the replacement of the Si channel by III-V materials, where the most critical issue is the realisation of high quality hetero-integration of III-V materials lattice matched to Si substrates.

In order to circumvent these problems, it is important to understand and identify the sources of defect/strain generation. Through the selection of appropriate characterisation methodologies, I aim to achieve the following technological objective:

1) Design a non-destructive X-ray characterisation routine that can be used to effectively identify various issues associated with heteroepitaxial growth of III-V materials, and delivers useful experimental feedback to growers for material quality optimisation.

Although "MtM" technology provides an alternative route, which enables continued rapid progress in functional density during a period where traditional CMOS scaling cannot keep pace and new architectures are not ready, it is still plagued by reliability issues that need to be addressed in order in improve the efficiency of the existing packaging products. Therefore a second aim in this thesis is as follows:

2) Development and implementation of a novel technique for non-destructive analysis of manufacturing process-induced stress/warpage inside completely encapsulated packaged chip

#### 1.3 Characterisation methodology

#### i) Characterisation of heteroepitaxial growth of III-V materials

The most common problems that have to be encountered during the hetero-integration of III-V materials lattice matched to Si substrates have been anti-phase domains, dislocations, strain and lattice tilts distributed within the III-V layers due to their crystal dissimilarities. These factors mean that abundant extended defect densities (>10<sup>8</sup> cm<sup>-2</sup>) are generated in the III-V epitaxial layers when directly grown on Si substrates. The selection of appropriate characterisation techniques is an essential first step to identify significant effects of each growth step (i.e. growth and annealing temperatures, III/V flux ratios and layer thickness), towards the production of low defect density heteroepitaxial of III-V materials.

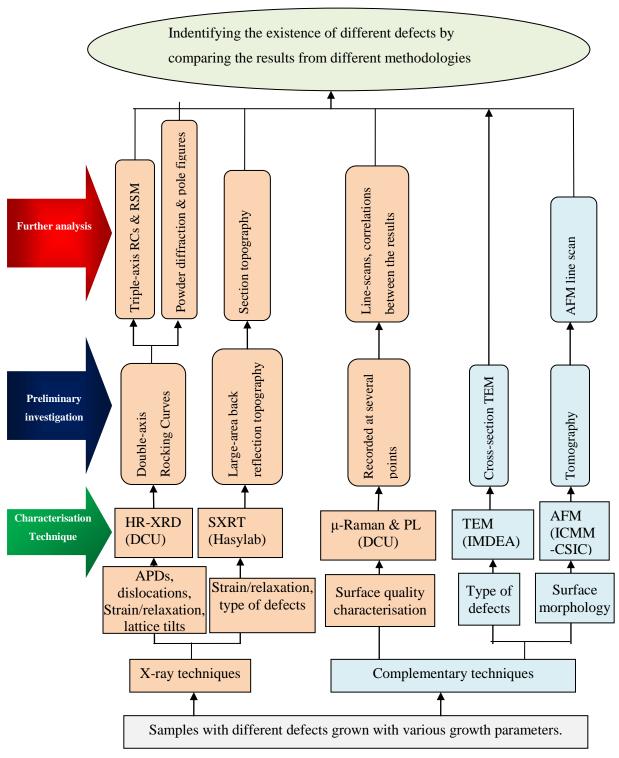

An X-ray characterisation routine that can be used to effectively help III-V growers in tackling the aforementioned problems was designed, as summarised in Fig. 1.7. This routine was planned using mainly X-ray diffraction techniques such as conventional X-ray diffraction (XRD) and high-resolution XRD (HR-XRD) performed at Dublin City University (DCU) by me and synchrotron X-ray topography (SXRT) performed at HASYLAB. It is to examine specimens using a range of essentially non-destructive methods; this is because often one characterisation technique alone cannot reveal all the desired characteristics of the specimens under test. Likewise, many preferred techniques are destructive in nature – either during the measurement itself or prior to the measurement, during sample preparation. When one uses non-destructive methods, it allows the same specimen to be measured a number of times in order to obtain comprehensive information. Apart from X-ray techniques, I have also employed optical techniques such as micro-Raman spectroscopy, and photoluminescence spectroscopy to characterise the surface quality of the specimen. Other measurements such as atomic force microscopy (AFM) and transmission electron microscopy (TEM) were provided by collaborators from Instituto de Ciencia de Materiales de Madrid (ICMM-CSIC) and

IMDEA Materials, Madrid, Spain, respectively. These measurements served the purpose of complementing the analysis of my own results.

In order to demonstrate the capability of this X-ray characterisation routine in identifying the existence/generation of different defects associated with heteroepitaxial growth as well as in identifying the significant effects of each growth process, I have implemented this routine to characterise a series of deliberately fabricated heteroepitaxial GaAs materials with different defects (antiphase domains, dislocations, strain/relation, lattice tilts). These 'problematic' GaAs materials were deposited on Ge and Si substrates by altering the growth parameters, which will be explained in more detail in Chapter 4. In this work all the materials were grown and provided by collaborators from Instituto de Ciencia de Materiales de Madrid (ICMM-CSIC), Spain.

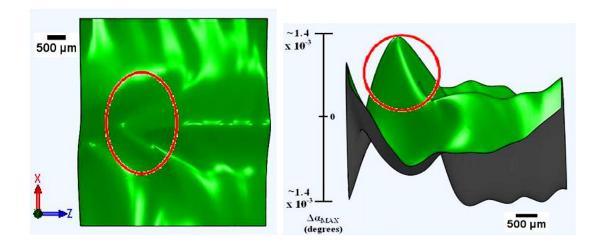

#### ii) Lab-based X-ray diffraction 3-dimensional surface modelling (XRD/3DSM)

As the reader will subsequently see, XRD-3DSM is a novel technique for non-destructive analysis of strain/warpage inside completely encapsulated packaged chips. Originally developed by DCU Researchers using synchrotron sources [37, 38]. It was developed using XRD techniques, utilising a laboratory-based a triple-axis Jordan Valley D1 X-ray diffractometer at DCU. Maps are produced of the entire Si die inside a packaged chip, which reveal warpage via mapping of rocking curve full-widths-at-half-maximum (FWHM) as a function of position across encapsulated packages. SXRT is used to validate data obtained from XRD/3DSM. More details of the technique will be explained in Chapter 5.

Figure 1.7 The work flow of the characterisation methodology used for analysing the quality of heteroepitaxially grown III-V materials. Acronyms are defined in the text.

#### 1.4 Report Layout

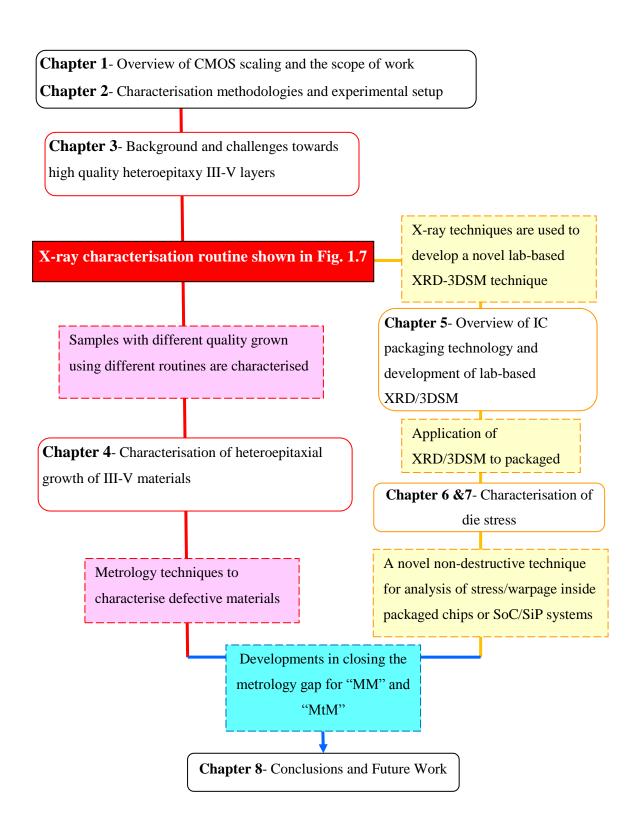

This report is structured into a number of chapters, organised as described by the chart in Fig. 1.8. Chapter 2 describes the fundamentals of the characterisation methodology and the instrumental setup. Chapter 3 discusses the major barriers that hamper the heteroepitaxy of GaAs on non-polar substrates and the challenges encountered in growing high quality GaAs layers by ELO on nanostructured-oxide substrates. Chapter 4 gives a brief discussion regarding the growth of GaAs samples and reviews the charactersation of heteroepitaxial growth of GaAs samples using the X-ray charactersation routine shown in Fig. 1.7. More specifically, the implementation of distinct approaches in identifying various issues associated with heteroepitaxial growth will be discussed. Chapter 5 reviews briefly the evolution of IC packaging technology and the development and implementation of XRD/3DSM for non-destructive analysis of die stress inside packaged chips. Chapters 6 and 7 demonstrate the feasibility of the XRD/3DSM technique for chateracterisation of die stress inside fully encapsulated packaged chips. Finally, Chapter 8 covers the conclusions from this research and outlines future work.

Figure 1.8. Chart showing the organisation of this thesis.

#### Chapter 2

#### **Characterisation Methodology and Instrumental Setup**

#### 2.1 Introduction

The selection of appropriate characterisation methodologies is vital for analysing and comprehending the source of defects and strain generation and their influence on the properties of semiconductor materials. This chapter has the preliminary aim of introducing the fundamental and instrumental setup of numerous characterisation techniques that have been selected for this work.

#### 2.2 X-Ray diffraction (XRD)

X-Ray diffraction is a non-destructive analytical methodology which can provide information about the chemical composition and crystallographic structure of natural and manufactured materials. It is used extensively for quality control of production, especially in research and development applications.

#### 2.2.1 Fundamentals of X-ray diffraction

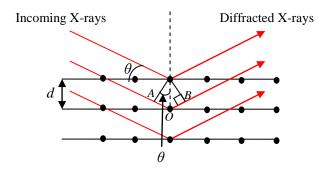

In 1911, the phenomenon of X-ray diffraction (XRD) in crystalline materials was discovered by von Laue, Friedrich and Knipping in rock salt [39]. In the following year, 1912, W. L. Bragg confirmed that crystal diffraction is associated with a set of evenly spaced sheets typically running through centres of the atoms of the crystal lattice, as depicted in Fig. 2.1. The scattered X-rays from adjacent planes will add up constructively and generate a strong diffraction. This, however, only occurs under specific circumstances, namely when [40]:

$$n\lambda = 2dsin\theta \tag{2.1}$$

where n is an integer representing the order of diffraction,  $\lambda$  is the wavelength, d is the interplanar spacing of the diffracting planes and  $\theta$  is the angle between the incident beam and the diffracted beam relative to the reflecting plane. That said, reflection occurs when the following criteria are satisfied [40]:

- i) the angle of incidence is equivalent to the diffracted angle,

- ii) the path-length difference  $(AO+AB \text{ or } dsin\theta + dsin\theta)$  is equal to an integer multiple of the X- ray wavelength  $(n\lambda)$ .

Figure 2.1 Schematic diagram of Bragg diffraction.

#### 2.2.2 Diffraction in reciprocal space

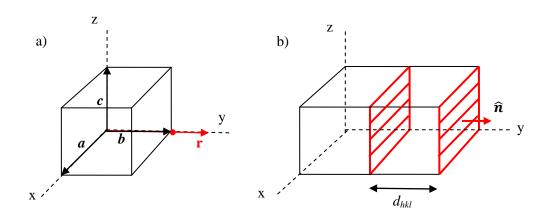

An ideal crystal is built up of molecules arranged on a regular 3-dimensional crystal lattice. A crystal lattice can be explained as a periodic arrangement of molecules in a regular pattern in the crystal. The basic building block for the crystal lattice is known as the unit cell. The length of the unit cell along the three crystallographic axes x, y and z directions are defined as a, b and c, as shown in Fig. 2.2. In real space, any direction in a crystal can be specified using a lattice vector (r) and can be written as [41]:

$$\mathbf{r} = u\mathbf{a} + v\mathbf{b} + w\mathbf{c} \tag{2.2}$$

where u, v and w are integers that specify the direction and a, b and c are the unit cell vectors describing the lattice, as shown in Fig. 2.2.

Figure 2.2 Schematic diagrams illustrating a unit cell in real space, a) a direction in a crystal represented by a vector  $(\mathbf{r})$ , and b) a direction of a set of parallel crystal planes (hkl) defined by their normal vector  $(\widehat{\mathbf{n}})$  and interplanar spacing  $(d_{hkl})$  [41, 42].

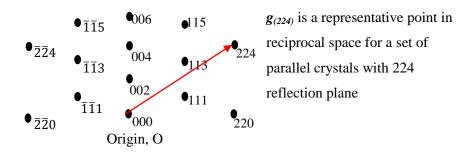

When one considers X-ray diffraction, it is always easier to describe the structure of a crystal in terms of families of planes (hkl). This is because X-ray diffraction occurs from different sets of crystals with different reflection planes (hkl) and interplanar spacings ( $d_{hkl}$ ) at different angles, as previously described using Bragg's law. A set of parallel crystal planes (hkl), can be characterised by its normal vector ( $\hat{n}$ ) and interplanar spacing ( $d_{hkl}$ ) [41], as shown in Fig. 2.2b). By using these two quantities, each set of parallel crystal planes (hkl) can be represented by a single point in reciprocal space, in which each reciprocal lattice point is defined by a reciprocal lattice vector ( $g_{hkl}$ ). The  $g_{hkl}$  is always parallel to  $\hat{n}$  of the crystal plane (hkl) in cubic crystals, and they are related by [41]

$$\boldsymbol{g}_{hkl} = \frac{1}{d_{hkl}} \hat{\boldsymbol{n}} \tag{2.3}$$

where  $|g_{hkl}| = \frac{1}{d_{hkl}}$  is the distance of the reciprocal lattice point from the lattice origin. An example of a 2-dimensional reciprocal lattice of GaAs is depicted in Fig. 2.3 [43]. By way of example, a line drawn from the origin of the reciprocal lattice (typically taken to be a reciprocal lattice point itself) to another point is a reciprocal lattice vector  $(g_{hkl})$ .

Figure 2.3 Two-dimensional reciprocal lattice for zincblende GaAs [43].

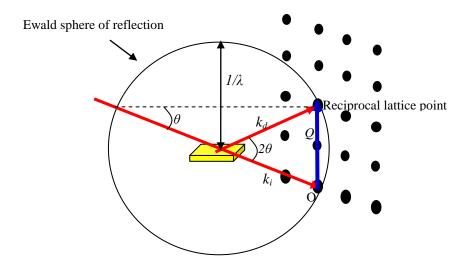

The X-ray diffraction in reciprocal space can be further explained using a geometrical construct called the Ewald sphere, as illustrated in Fig. 2.4. The Ewald sphere is centred on a line representing the X-ray beam direction, and it has a radius of  $1/\lambda$  [41]. The reciprocal lattice has its origin at the point where the X-ray beam exits the Ewald sphere. The crystal rotation around the centre of the sphere is equivalent to the rotation of the reciprocal lattice about its origin. A strong diffraction from a crystal with reflection planes (hkl) will occur when the corresponding reciprocal lattice point (hkl) lies exactly on the circumference of the Ewald sphere [41].

As shown in Fig. 2.4,  $k_i$  and  $k_d$  represent the wavevectors along the directions of the incident, and diffracted beams, respectively. The scattering vector  $\mathbf{Q}$  is equivalent to the difference between the diffracted and incident ( $\mathbf{Q} = \mathbf{k}_d - \mathbf{k}_i$ ) wavevectors. This is the condition at which it satisfies Bragg's law and diffraction occurs [41, 44]. This can be shown through the following relationship obtained from the Ewald sphere shown in Fig. 2.4,

$$\frac{|\mathbf{Q}|_{2}}{\sin\theta = \frac{1}{\lambda}}$$

(2.4)

For a crystal with reflection planes of (hkl) which satisfy Bragg's law, the reciprocal lattice vector  $(\boldsymbol{g}_{hkl})$  is identical to the scattering vector  $(\boldsymbol{Q})$  [41, 44]. Therefore, the modulus of  $\boldsymbol{Q}$ , i.e.  $|\boldsymbol{Q}|$  is equal to  $|\boldsymbol{g}_{hkl}|$  and it is simply  $^1/_{d_{hkl}}$  in real space, obtained from Eq. 2.3. Substituting  $|\boldsymbol{Q}|$  into Eq. 2.4, one can obtain a relationship which is equivalent to Bragg's law,

$$Sin\theta = \frac{\lambda}{2d_{hkl}} \tag{2.5}$$

Figure 2.4 Ewald sphere construction illustrating the diffraction X-ray occurs in reciprocal space [41].

#### 2.3 Powder X-ray diffraction (XRD)

This technique is used to characterise micro- or poly-crystalline samples in order to ascertain the crystallographic structure, average crystallite sizes, and the preferred orientation

(texture) in the polycrystalline samples. An unknown substance can be identified from its diffraction pattern, as each individual substance possesses a distinctive diffraction pattern. This can be done by comparing the experimental diffracted pattern against a Powder Diffraction File (PDF) – comprising of data on interplanar spacings (*d*) and relative intensities (*I*) complied for crystalline materials - maintained by the International Centre for Diffraction Data (ICDD) [45]. A powder XRD spectrum can be collected by setting the sample and detector angles together in a 2:1 ratio, which will be explained further in subsequent sections.

One of the most useful features of XRD is its ability to determine the crystallinity of substances. The diffraction pattern of a crystalline material comprises a series of sharp peaks, which are distinguishable from the broad and weak intensity peaks produced by amorphous material. Through the line broadening of the peak, the average crystallite size is computable via the Scherrer equation [41],

$$t \approx \frac{0.9\lambda}{\beta \cos \theta} \tag{2.6}$$

where t is the calculated average crystallite size,  $\lambda$  is the wavelength of the X-ray source used,  $\beta = \beta_{measured} - \beta_{machine}$  is the full width at half maximum (FWHM) of the diffracted peak in radians (corrected for any instrumentally induced line broadening) and  $\theta$  is the Bragg diffraction angle of the peak.

#### 2.3.1 Crystallographic texture mapping

A polycrystalline sample might typically comprise of a number of randomly distributed grain orientations and some of these grain orientations might tend to cluster about a preferred orientation. These are known as non-textured and textured materials, respectively.

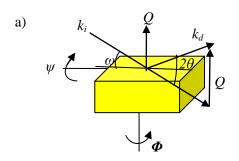

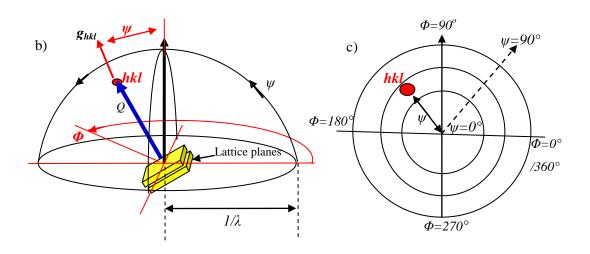

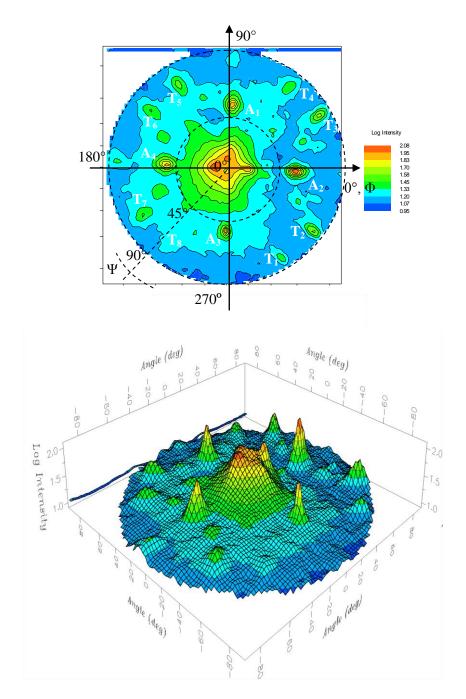

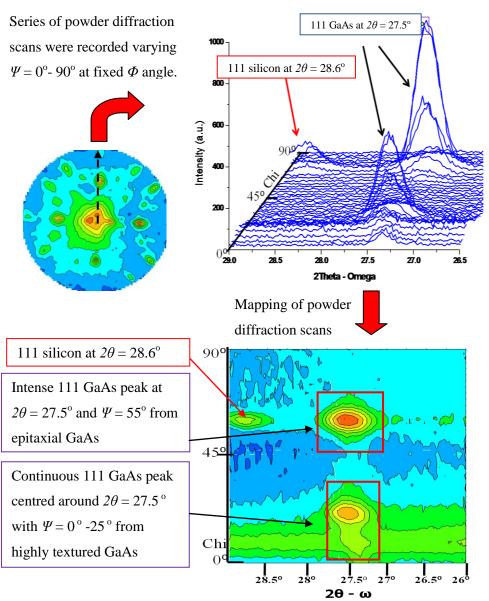

A pole figure is the stereographic projection mainly used to graphically illustrate the distribution of grain orientations of a polycrystalline material. It can be plotted by recording the conventional powder diffraction  $2\theta$ - $\omega$  scans for all rotations (phi,  $\phi = 0$  - 360) and tilts (chi,  $\psi = 0$  - 90 °) of the sample, in order to collect the intensity distribution throughout all reciprocal space [41, 44]. A single  $2\theta$ - $\omega$  scan can be recorded by setting the sample and detector angles together in a 2:1 ratio, shown in Fig. 2.5 (a). In this experimental geometry, the scan always moves along the direction normal to the sample surface, and thus, collects only the 'out-of-plane' lattice constant information for a crystalline material. In other words, a  $2\theta$ - $\omega$  scan only collects information on grains with Bragg planes parallel to the film plane [41, 44], while a pole figure is a combination of a series of  $2\theta$ - $\omega$  scans recorded for different tilts against the X-ray incident beam incidence plane and rotated around the sample normal in order to get all grains in a diffracting position. Therefore, it captures the intensity distribution throughout all of reciprocal space over the surface of a hemisphere with a radius of,  $\frac{1}{\lambda}$  (see Fig. 2.5b) [41, 44]. For a crystal with reflection planes of (hkl) which satisfy Bragg's law, the reciprocal lattice vector  $(\boldsymbol{g}_{hkl})$  is identical to the scattering vector  $(\boldsymbol{Q})$  (see Fig. 2.5 b). The resulting collected intensities are plotted onto a two-dimensional pole figure (pole plot as shown in Fig.2.5c. Strong diffractions occur only when Bragg's law is satisfied for lattice planes of the textured grains for a particular (hkl) reflection at a certain tilt,  $\psi$ , and rotation,  $\phi$ .

Figure 2.5 Schematic diagrams of a)  $2\theta$ - $\omega$  scan in reciprocal space, and scanning geometry for a pole figure, b) Hemisphere represents the stereographic projection of all reciprocal space, and c) Top view of the hemisphere (pole plot) [41, 44].

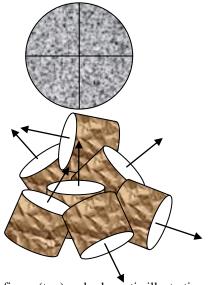

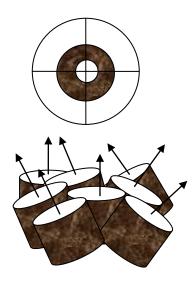

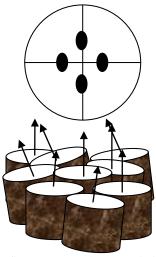

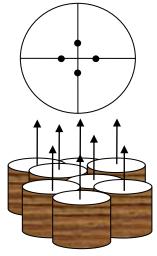

If the material has no texture, the collected signal will be uniformly distributed on the pole figure. Alternatively, poles will tend to group together at certain chi,  $\psi$ , and phi,  $\phi$ , angles in the pole figure if the material comprises of some preferential grain orientations. If the preferred orientation is very strongly preferential, the poles will tend to group together in tighter and tighter bands as the texture becomes stronger as illustrated in Fig. 2.6.

a) Pole figure (top) and schematic illustration of polycrystalline material with random orientation

b) Pole figure (top) and schematic illustration of highly textured polycrystalline material with certain preferred orientation

c) Pole figure (top) and schematic illustration of grain with preferred orientations in [001] direction, i.e. misoriented epitaxial layer

d) Pole figure (top) and schematic illustration of grain with strong orientations in [001] direction, i.e. a perfect single crystal layer

Figure 2.6 Pole figures and schematic illustrations of preferred orientation. The arrows show the direction for a chosen (hkl) direction.

#### 2.4 High-resolution X-ray diffraction (HR-XRD)

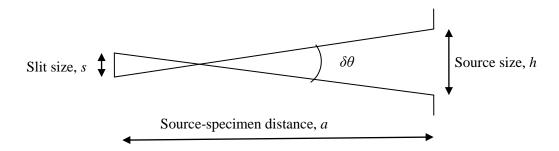

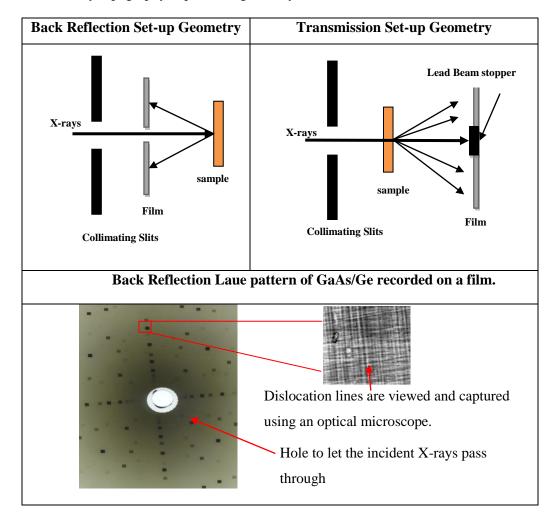

The most significant difference between high-resolution XRD and conventional XRD measurements is the use of a highly collimated incident monochromatic beam, e.g. of the order of ~12 arc-sec divergence compared to ~ 360 arc-sec for conventional XRD measurements. The divergence of the beam is closely related to the source size (h), slit size (s) and the source-specimen distance (a). As shown in Fig. 2.7, the divergence  $(\delta\theta)$  is expressed as [43]

$$\delta\theta = \frac{h+s}{a} \tag{2.7}$$

In order to reveal the finest details from the specimen, the divergence of the beam has to be smaller than the angular offset caused by defects in the specimen. For conventional XRD measurements, the divergence of the beam is ~ 360 arc-sec [46] and yields a rocking curve with a broad full-width-at-half-maximum (FWHM). This is far beyond the angular resolution that we require to reveal the details of thin epitaxial films, where typically in the order of 10 arc-sec is necessary [43]. Therefore, a highly monochromatic incident beam is essential to provide sufficient angular resolution for HR-XRD measurements in order to reveal the layer thickness, composition, strain and relaxation of thin epitaxial films at the arc-second scale.

Figure 2.7 Schematic diagram showing the divergence along a single-axis [43].

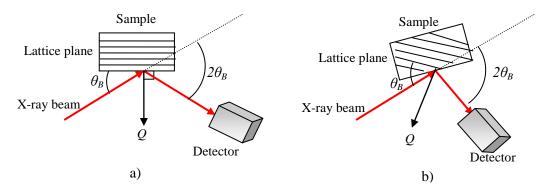

#### 2.4.1 HR-XRD experimental geometry

Symmetric and asymmetric reflection modes are the two types of experimental geometries typically used in HR-XRD experiments. A symmetric Bragg reflection geometry collects only the information from out-of-plane (direction perpendicular to the layer plane) structural parameters, while the use of asymmetric grazing incidence is exceedingly sensitive to the in-plane structural parameters (parameters of the crystal structure in the layer plane) (see Fig. 2.8) [46]. Combining the data from both geometries provides us with all the meaningful information that we require for analysis.

Figure 2.8 a) Symmetric (collects only the out-of-plane lattice parameter) and b) asymmetric (collects in-plane lattice parameter data) diffraction geometry for high-resolution X-ray diffraction.

#### 2.4.2 High-resolution XRD rocking curves and $\omega$ -2 $\theta$ scans

Two distinct types of HR-XRD scans are defined as  $\omega$  (omega) scans and  $\omega$ - $2\theta$  (omega-2theta) scans. An  $\omega$  scan is used to evaluate the mosaic tilt in a material. It can be recorded by scanning the sample angle ( $\omega$ ) for a specific angular range of arc-sec with the detector angle ( $2\theta$ ) fixed at twice the known Bragg angle. The resulting plot of angle ( $\omega$ ) versus the collected intensity is known as a rocking curve. On the other hand, the  $\omega$ - $2\theta$  scan is recorded by scanning the sample and detector angles together in a 1: 2 ( $\omega$ :  $2\theta$ ) ratio. Thus

the scan is collected by moving the  $2\theta$  detector axis at the twice the rate of the  $\omega$  axis. This geometry is particularly useful in revealing the structural parameters of the epitaxial layer, i.e. strain, composition and layer thickness [43]. For instance, for GaAs heteroepitaxially grown on Si, defects such as dislocations are typically predominant due to the large lattice mismatch between GaAs and Si. These extended linear defects generated during the growth process directly impact on the full-width-at-half-maximum (FWHM) and peak splitting of the rocking curves ( $\omega$ -scans) and  $\omega$ - $2\theta$  scans, respectively [43]. Table 2.1 summarises some of the important parameters that will impact on the characteristics of rocking curves or  $\omega$ - $2\theta$  scans.

Table 2.1 The effect of substrate and epilayer parameters upon the rocking curves and  $\omega$ -2 $\theta$  scans [43].

| Material            | Effect on rocking                     | Distinguishing features                                                                                 |

|---------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------|

| parameter           | curve                                 |                                                                                                         |

| Mismatch            | Splitting of layer and substrate peak | Invariant with sample rotation                                                                          |

| Misorientation      | Splitting of layer and substrate peak | Changes sign with sample rotation                                                                       |

| Dislocation content | Broadens peak                         | Broadening invariant with beam size. No shift of peak with beam position on sample.                     |

| Curvature           | Broadens peak                         | Broadening increases linearly with beam size.  Peak shifts systematically with beam position on sample. |

| Relaxation          | Changes splitting                     | Different effect on symmetrical and asymmetrical reflections.                                           |

High-resolution X-ray diffraction rocking curves (HR-XRD RCs) can be measured in either double-axis or triple-axis configuration based on the type of information that is required by the user. A typical double-axis RC experiment can be done in a short period of time. Conversely the time requirements are generally longer for triple-axis analysis as an additional analyser crystal is placed on the detector side for a more precise definition of the detector scattering angle,  $2\theta$ . This analyser crystal itself will quench the diffracted intensity, and thus,

longer exposure times are required to increase the signal-to-noise ratio in order to achieve a clean result. This also prevents the disappearance of some smaller peaks [43].

In the double-axis configuration, one collects the scattered intensity from all diffraction angles from the specimen and some vital parameters become indistinguishable, i.e. distinguishing between the lattice tilt and changes in interplanar (d) spacing of the crystal, and details such as interference fringes or narrow peaks can be lost or blurred [43]. This deficiency can be resolved unambiguously in triple-axis geometry by inserting the additional analyser crystal before the detector. The auxiliary crystal restricts the angular acceptance of the detector into few arc-seconds which further defines the  $2\theta$  angle [43].

# 2.4.3 HR-XRD analysis by RADs simulations

As previously mentioned parameters of the epilayer such as strain relaxation, thickness and composition can be extracted directly from the peak splitting and position of measured HR-XRD scans. These details are easily determinable by modelling  $\omega$ - $2\theta$  scans using the supplied JV-HRXRD software [46] called RADs (rocking-curve analysis software). Experimental data is compared to the simulated model using a robust goodness-of-fit (GOF) function [46]. Parameters such as background intensity, layer thickness, layer composition and strain relaxation are iteratively adjusted until best-fit-parameter values are achieved (lowest GOF values - a single number that reflects how well the best-fit simulation agrees with the experimental data) [46]. Although RADs simulations provide a lot of information regarding the epilayer it is not a sufficiently sophisticated package to extract all the required detailed information from a complex crystal structure, such as a monocrystalline layer embedded in a highly-textured polycrystalline layer. Despite these deficiencies, RADs simulation is still useful for the full analysis of epilayers, multilayer structures and alloyed semiconductors.

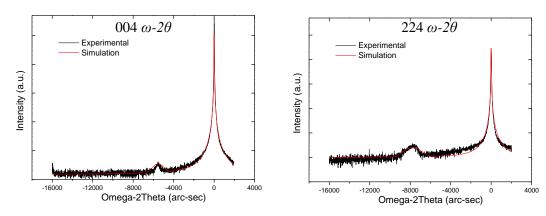

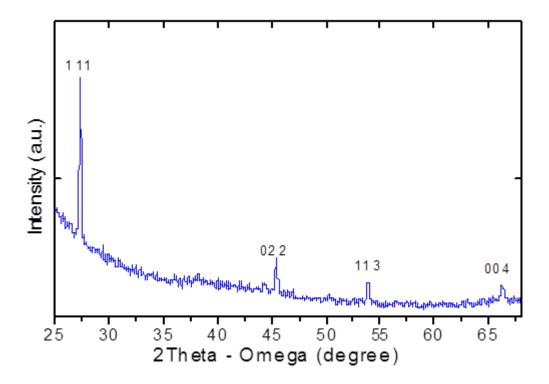

The data-fitting process of RADs simulation includes few main stages, which will be demonstrated through an analysis of the degree of relaxation using a 004  $\omega$ -2 $\theta$  HRXRD scan from a 180 nm thick- GaAs layer deposited on Si substrate:

# i) Importing the experimental data

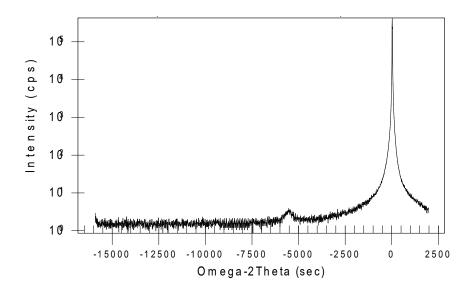

The file containing the experimental HRXRD data is imported into RADs and will be displayed in the form of an (x, y) line chart, as shown in Fig. 2.9.

Figure 2.9  $\omega$ -2 $\theta$  HR-XRD scan of GaAs/Si sample imported into Bede RADs.

# ii) Creating a simulation model

A simulation model of the sample structure is built using the Model panel. For this case, bare Si is used as the substrate for the model, and then a GaAs layer is added to form the GaAs/Si simulation model. For the initial assumption, the GaAs layer thickness of the simulation model is set to the nominal thickness of 180 nm, and the degree of relaxation is assumed to be 0% (fully matched).

# iii) Simulating the diffraction

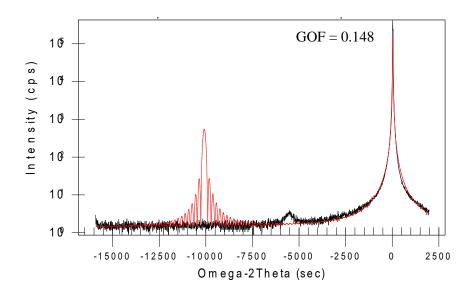

The model built in the previous step is simulated and displayed as the red (x, y) chart, as shown in Fig. 2.10. It is obvious that the initial simulated HRXRD curve does not match the experimental data. This implies that the GaAs overlayer is relaxed, therefore further data fitting is required in order to determine the actual degree of relaxation.

Figure 2.10  $\omega$ -2 $\theta$  HR-XRD scans and corresponding initial simulation of GaAs/Si sample before data fitting.

# iv) Fitting the diffraction

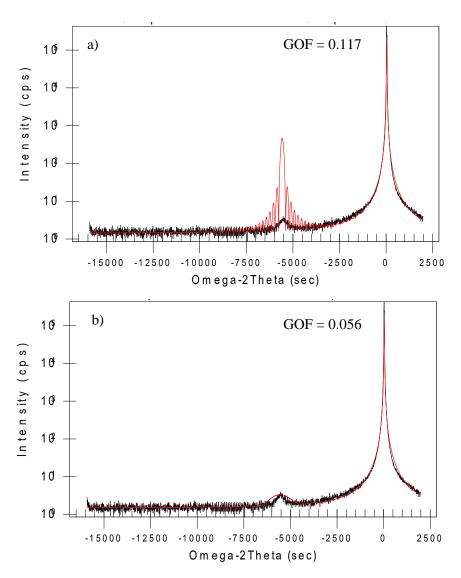

In order to obtain the best fit model, each parameter (relaxation degree and thickness) is fitted individually and iteratively by RADs simulation until a lowest GOF value is achieved. For example, Fig. 2.11a) shows the simulation model after the degree of relaxation is fitted and this reduces the GOF value to 0.117. The lowest GOF value or best fit model can be achieved when the thickness is fitted and background noise is introduced, as shown in Fig. 2.11b). From the best fit model, the GaAs/Si layer is determined to be fully relaxed (~100% relaxation) with 15 nm thickness.

Figure 2.11  $\omega$ -2 $\theta$  HR-XRD scans and corresponding simulation of GaAs/Si sample after data fitting. a) Simulation model after relaxation degree is fitted, and b) Best fit model achieved after the thickness and background noise are fitted. Note that the fit parameters can be found in Table 4.3.

# 2.4.4 Reciprocal space mapping

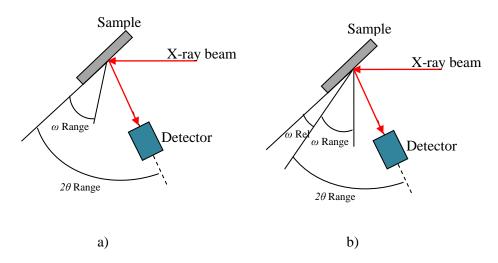

As described in the previous section, a triple-axis HR-XRD  $\omega$ - $2\theta$  scan comprises of only the data from one specific tilt. In order to gather the information for a range of tilts,

reciprocal space mapping (RSM) is needed. This can be obtained by collecting a series of  $\omega$ - $2\theta$  scans at different omega offsets (omega\_Rel), where  $2\theta = 2*\omega - offset$ , as shown in Fig. 2.12. The tilt value recorded in each  $\omega$ - $2\theta$  scan is typically different. Therefore, a RSM – a complete map of  $\omega$ - $2\theta$  versus tilt (omega\_Rel) - is obtained by mapping the intensity distributions of these scans using Contour software. In other words, it is an extension of rocking curve analysis that provides more valuable data in distinguishing the strain or mismatch from tilt or mosaic spread in a sample.

Figure 2.12 a) For omega\_Rel zero: A  $\omega$ -2 $\theta$  scan is collected, and b) A RSM can be obtained by collecting a series of  $\omega$ -2 $\theta$  scans at different omega offsets (omega\_Rel), where  $2\theta = 2*\omega - offset$  [42].

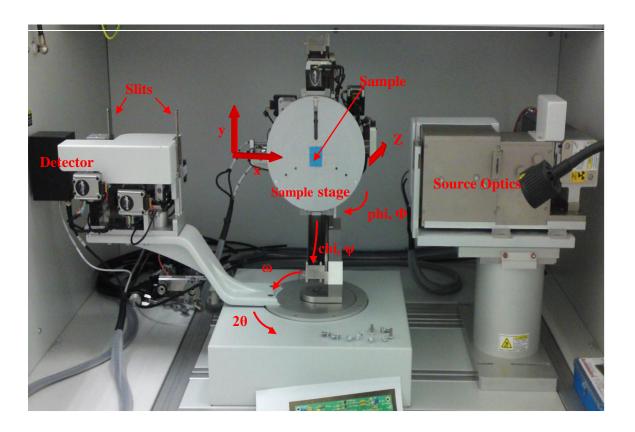

# 2.4.5 X-ray diffraction instrument set-up

All X-ray diffraction measurements were carried out using a triple axis Jordan Valley BEDE-D1 X-ray diffractometer as shown in Fig. 2.13. The incident X-ray beam was produced by a Cu rotating anode generator operated at 45 kV and 40 mA. A beam conditioner is used to condition the incident beam into a quasi-parallel beam (with a divergence of ~360 arc-second) or further conditioned into monochromatic beam mode (with a divergence of ~12

arc-second) (Cu-K<sub>a1</sub>;  $\lambda = 1.5405$  Å) for standard XRD and high-resolution XRD measurements, respectively [46]. The instrument sample stage allows the sample to move in  $x, y, z, \chi$  (chi, tilt of sample) and  $\phi$  (phi, rotation of the sample about the surface normal).  $\omega$  is the angle between sample and incident X-ray beam, whereas  $2\theta$  is the angle between incident X-ray beam and scattered X-ray beam (see Table 2.2 for the specification). All of these movements can be navigated via the Bede Control – instrument control software from Bede Scientific, and therefore allows the sample to be properly aligned prior to any of the X-ray measurements.

Figure 2.13 Photo of the Jordan Valley D1 X-ray diffractometer system.

Table 2.2 D1 system stage axes specification [46].

| Axis   | Function                                                   | Range                   | Resolution                    |  |

|--------|------------------------------------------------------------|-------------------------|-------------------------------|--|

| х      | Specimen translation, <i>x</i> direction                   | 150 mm                  | 0.5 μm                        |  |

| у      | Specimen translation, y direction                          | 150 mm                  | 0.5 μm                        |  |

| Z      | Specimen translation, z direction                          | 10 mm                   | 0.5 μm                        |  |

| X, Chi | Specimen tilt                                              | 135°<br>(-90° to + 45°) | 0.0003°                       |  |

| Φ, Phi | Specimen rotation about surface normal                     | ± 365°                  | 0.0001°                       |  |

| ω      | Angle between sample and incident X-ray beam               | 200° (~-10° to ~+ 190°) | ~0.000045°<br>(~0.16 arc-sec) |  |

| 2θ     | Angle between incident X-ray beam and scattered X-ray beam | 210° (~-70° to ~+ 140°) | ~0.000045°<br>(~0.16 arc-sec) |  |

The sample alignment process includes a number of main steps listed below:

# i) Mounting the sample onto the stage

- Sample should always be handled with clean tweezers in order to prevent contamination.

- Sample is mounted onto the central region of the stage using "blue tape", as shown in Fig. 2.13. This method of mounting has been found to introduce very little strain into the sample, which is important for high-resolution measurements [46].

- Always mount the sample in a known orientation i.e. the notch or flat or cleaved edge

of the sample always placed in the same direction with respect to the X-ray beam.

This allows the results from different samples to be easily compared and also to

ensure very high reproducibility of the measurements.

- For a miscut sample, the offcut direction should be placed perpendicular to the

incident beam, and the offcut can be compensated for by optimising the χ position of

the sample, in order to ensure a "real" symmetric experimental geometry [8].

# ii) Calibrating the $2\theta$ and $\omega$ zero positions

- It is important to remember that the lid of the system should be closed before the X-ray shutter is switched on or prior to any XRD measurement.

- Scan across the direct beam with the sample out of the incident X-ray beam (by moving the z position to 9 mm) for a  $2\theta$  range of  $0.5^{\circ}$ , and this gives us an X-ray intensity curve plotted against the  $2\theta$  scan range. The peak position of the intensity curve is the actual zero position for  $2\theta$ . The  $2\theta$  zero position can be recalibrated by moving the  $2\theta$  to the actual zero position via Bede control. The same process is repeated for  $\omega$  in order to ensure both the  $2\theta$  and  $\omega$  zero positions are recalibrated correctly to avoid any misalignment, and therefore ensures an accurate and repeatable result.

# iii) Aligning the sample in the beam by adjusting the position of sample stage

- The sample stage is moved (z) until intensity (I) =  $I_{full}/2$ , where  $I_{full}$  is the direct X-ray beam intensity. The position of  $\omega$  is adjusted slightly in steps of  $0.01^{\circ}$  to observe the maximum intensity. If the intensity is higher than  $I_{full}/2$ , the position of z has to be readjusted slightly in order to ensure that intensity is equal to  $I_{full}/2$ .

- The incident beam is now properly aligned, which means it is parallel and half-way across the sample surface. This is to ensure that the incident beam is located at the centre of rotation of  $2\theta$  and  $\omega$  or the sample surface is now over the centre of rotation.

# iv) Aligning the sample at the diffraction peak

• Move the  $\omega$  axis to the Bragg angle and the  $2\theta$  axis to the position of twice the Bragg angle of the substrate material (substrate peak is always chosen as reference for HR-XRD measurements). However, the Bragg angle is individually dependent on the type of experiments (symmetric or asymmetric) and also the orientation of the substrate material. For an offcut substrate, the incident beam is set perpendicular to the offcut

direction and the offcut can be compensated for by tilting the chi angle  $(\chi)$  of the stage.

• Optimisations are then carried up for  $\omega$ ,  $\chi$  and  $2\theta$  until the maximum intensity is acquired, this being the last step prior to measurements.

The sample alignment process can also be performed automatically by using scripts or recipes provided by this system. For certain circumstances, such as a sample with a few degrees of offcut, it is however more time efficient to manually align the sample using aforementioned steps ii)-iv).

Apart from the sample alignments, the configurations of the XRD instrument such as the source optics and slit sizes have to be appropriately adjusted for distinct measurements and these are presented in Table 2.3.

All the scattered X-ray intensity is collected using an Enhanced Dynamic Range Detector (EDRc). It is a 50 mm, scintillator detector (YAP: Ce) with a background level of ~1 to 1.5 cps and a saturation level of ~ 5 Mcps [46]. In general, the signal-to-noise ratio (S/N) of a diffraction pattern can be improved by using a longer count time (exposure time), but an increase in count time would mean an increase in the scan time. In order to avoid unnecessary long waiting times, different count times are typically selected based on the type of sample or intensities or features of interest, and this is however dependent on many factors such as crystallinity, sample thickness, type of measurement. For example, a 0.01 second count time is sufficient to collect a clean diffraction pattern from a 1000 nm thick Si sample, but a 5 second count time will be needed to collect a clean pattern from a 50 nm thick Si sample due to low diffracted intensities compared to background noise.

It is important to always mount the sample, calibrate the system and align the sample in a consistent way as previously discussed. This allows us to achieve very accurate and highly repeatable results – in the order of the sampling step size [46].

Table 2.3 Tool configuration of X-ray diffraction instruments for different applications [43, 46].

|                    | Standard X-ray diffraction – powder diffraction and crystallography texture mapping |                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|--------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Tool configuration | Schematic diagram                                                                   | Sample Soller Slit  Max-Flux  Max-Flux  Slits                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                    | Source optic                                                                        | $Max-Flux^{TM}-modulates \ the \ divergence \ of \ incoming \ X-ray \ beam \ into \ a \ quasi-parallel$ $beam \ of \ Cu \ K_{\alpha} \ X-rays \ with \ a \ divergence \ of \ \sim\!360 \ arc\text{-second}.$ $Slit-collimating \ the \ incoming \ beam \ to \ a \ width \ of \ 2 \ mm.$                                                                            |  |  |  |

|                    | Detector                                                                            | Slits – B and C are used to restrict the angular acceptance of diffracted X-rays and suppress diffuse scattering effects, respectively.  Soller slit – A set of parallel slits that used to limit the angular divergence or spread of the X-ray beam without restricting the size of the beam.                                                                     |  |  |  |

|                    | Axis                                                                                | Scan is run by setting the sample and detector angles together in a $2:1$ ratio, which is called a $2\theta$ - $\omega$ scan. Typically, it is calibrated in $2\theta$ ° for power diffraction scans. This scanning geometry allows the probing of sets of planes which lie parallel to the sample surface, especially in highly-textured polycrystalline samples. |  |  |  |

|                    | High-resolution X-ray diffraction – double-axis rocking curve and reciprocal space mapping |                                                                                                                    |  |  |  |

|--------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|

| Tool configuration | Schematic diagram                                                                          | Sample B C Detector  Channel-cut crystals  X-ray Tube                                                              |  |  |  |

|                    | Source optic                                                                               | Max-Flux <sup>TM</sup> – modulates the divergence of incoming X-ray beam into a quasi-parallel                     |  |  |  |

|                    |                                                                                            | beam of Cu $K_{\alpha}$ X-rays with a divergence of ~360 arc-second.                                               |  |  |  |

|                    |                                                                                            | Channel-cut-crystal – Two Si channel-cut crystals (CCCs) used in opposition after the Max-                         |  |  |  |

|                    |                                                                                            | Flux <sup>TM</sup> to further condition the beam into monochromatic Cu-Kα1                                         |  |  |  |

|                    |                                                                                            | with a divergence of ~12 arc-second.                                                                               |  |  |  |

|                    |                                                                                            | Slit – Slit A collimates the incoming beam to a width of 0.5 mm.                                                   |  |  |  |

|                    | Detector                                                                                   | Slits– B and C are used to restrict the angular acceptance of diffracted X-rays and                                |  |  |  |

|                    |                                                                                            | suppress diffuse scattering effects, respectively.                                                                 |  |  |  |

|                    |                                                                                            | Analyser – used only in triple-axis diffraction to precisely define the detector position.                         |  |  |  |

|                    |                                                                                            | Scan is run by setting the sample and detector angles together in a 1:2 ratio, called a $\omega$ -2 $\theta$ scan. |  |  |  |

|                    | is.                                                                                        | This scanning geometry is vital in order to probe the different interplanar spacings for the same                  |  |  |  |

|                    | Axis                                                                                       | sample tilt for high-resolution XRD. It was calibrated in arc-seconds prior to the                                 |  |  |  |

|                    |                                                                                            | measurements.                                                                                                      |  |  |  |

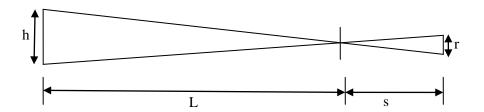

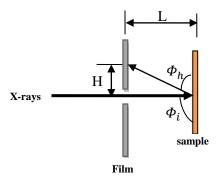

# 2.5 White Beam Synchrotron X-ray Topography (SXRT)

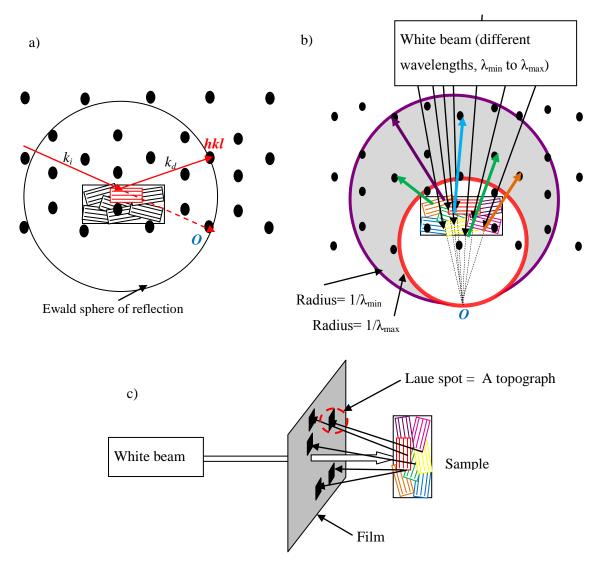

The concept of SXRT is analogous to the conventional laboratory-based XRD measurements, since both techniques are reliant on Bragg's law. Similar to XRD, the principle of SXRT can be explained using the geometrical construction of the Ewald sphere, as depicted in Fig. 2.14. For the lab-based XRD measurement, a monochromatic X-ray with a particular wavelength is used. Diffraction from a crystal plane (*hkl*) will occur only if Bragg's law is satisfied, i.e. if a reciprocal lattice point lies on the Ewald sphere. In other words, only diffraction from a specific set of lattice plane (*hkl*) of the crystal can be collected at one time. The diffraction from different crystal planes of interest can be acquired by orienting the sample to satisfy the Bragg condition for that particular plane [47].

Similar to X-ray diffraction, Synchrotron X-ray Topography (SXRT) is also a non-destructive method that is ideal for studying high quality crystalline materials, and in particular it can <u>image</u> defects and strain fields distributed within the crystals [48]. Using a white beam for SXRT brings several benefits, such as: sample orientation is not necessary, numerous reflections are recorded simultaneously with one exposure, all crystal parts are simultaneously visible, large diffracted intensity, and good geometrical resolution. One uses a continuous radiation spectrum (i.e. a "white beam") consisting of a continuum of wavelengths  $(\lambda)$  each of which can be diffracted subject to the Bragg criterion being satisfied [48], as previously discussed.

As shown in Fig. 2.14b), a white beam comprises of X-ray beams with a continuum of wavelengths, ranging from a minimum wavelength,  $\lambda_{min}$  to some maximum wavelength,  $\lambda_{max}$ . A white beam allows a range of reciprocal lattice points to lie simultaneously on Ewald spheres with different radii [49]. Therefore, multiple diffractions can be recorded simultaneously on a single film with a single white beam X-ray exposure, forming a so-called

Laue pattern (see Fig. 2.14c). Each Laue spot is an X-ray topograph corresponding to a reflection arising from a different crystal plane of distinct (*hkl*).

Figure 2.14 Ewald sphere diagrams illustrating the X-ray diffraction in reciprocal space a) using a monochromatic beam and b) using a white beam. Multiple Laue spots recorded on a single film using white beam in back reflection geometry is shown in c) [47, 48].

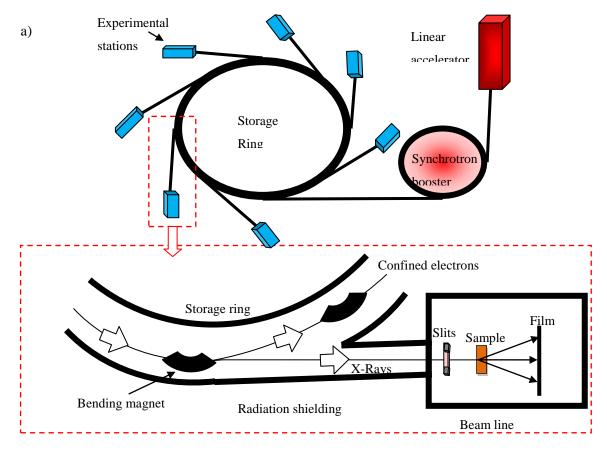

# 2.5.1 Synchrotron Radiation X-ray Source

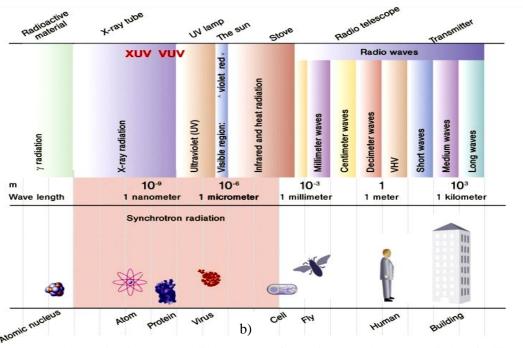

Synchrotron radiation is generated when electrons or positrons, whose velocity is close to the speed of light, are accelerated and confined to a circular orbit in a storage ring by

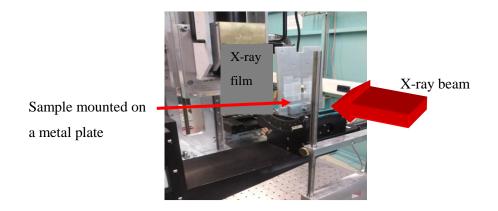

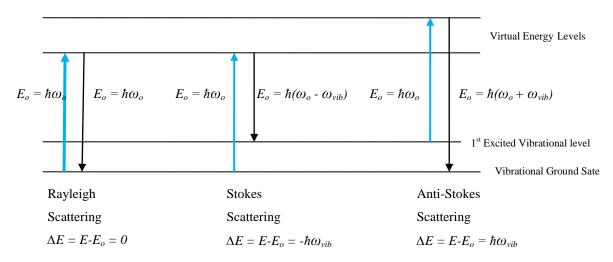

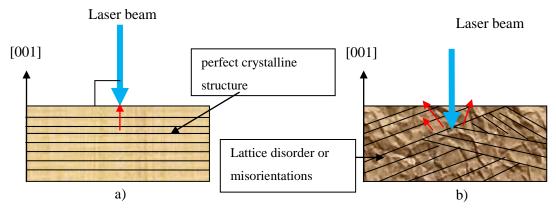

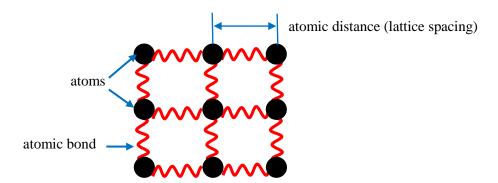

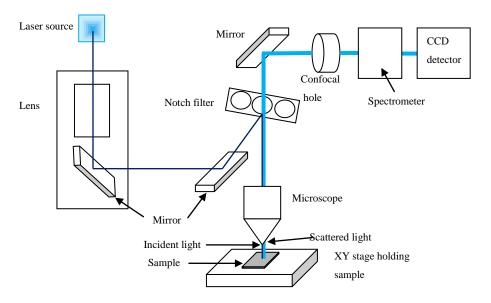

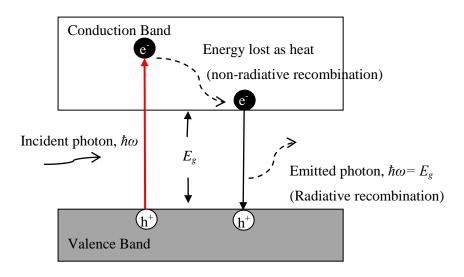

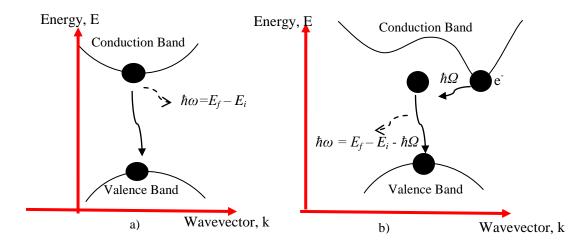

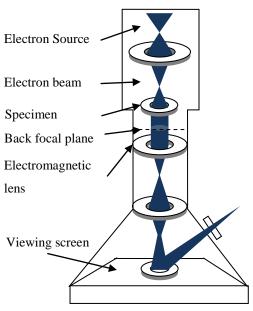

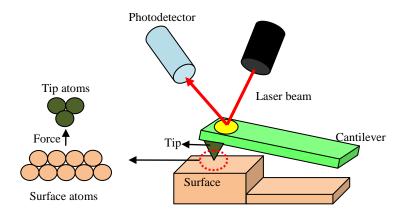

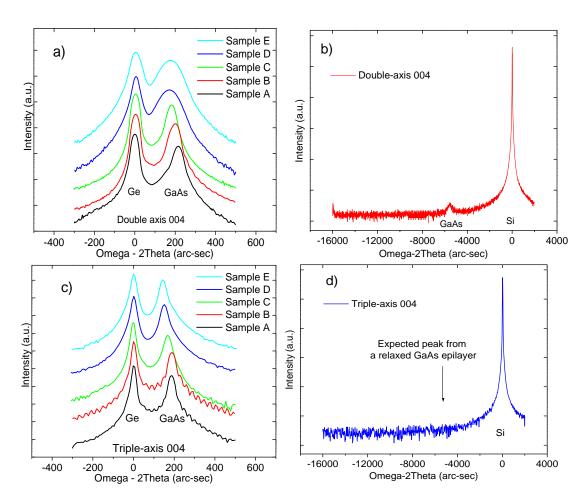

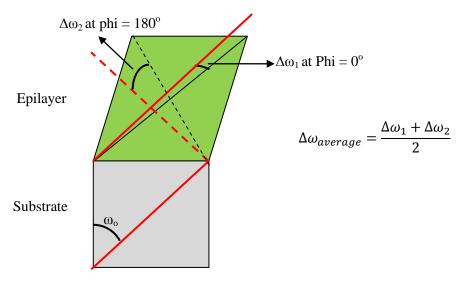

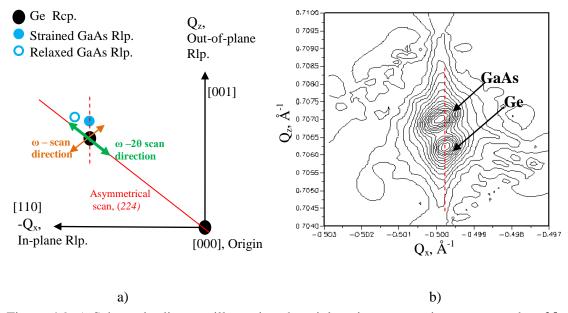

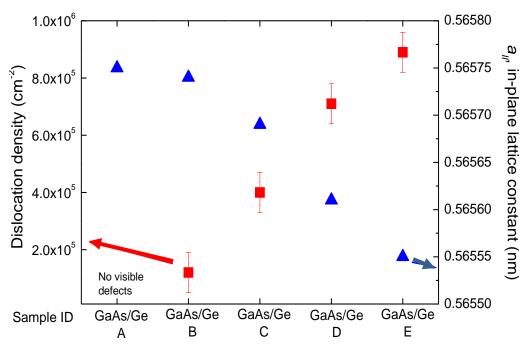

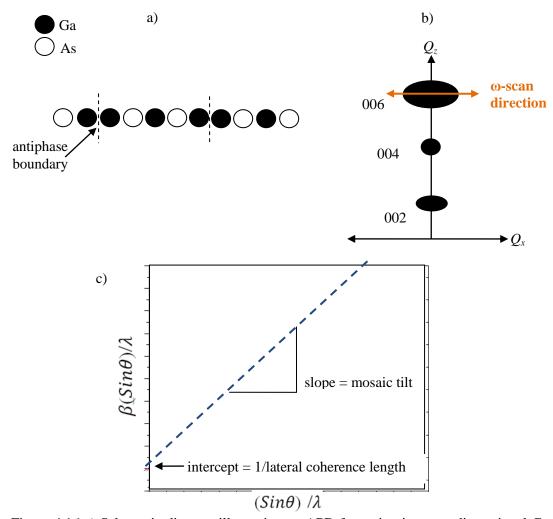

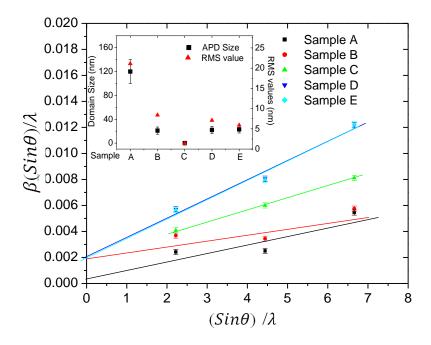

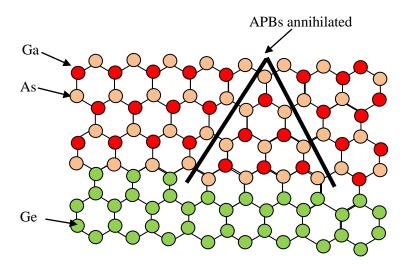

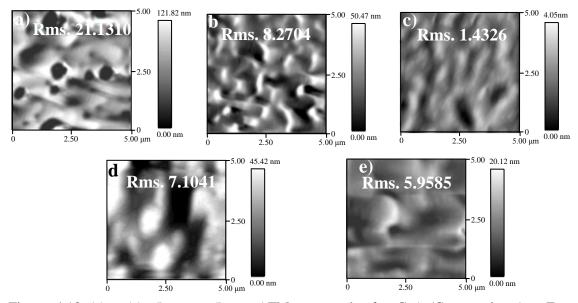

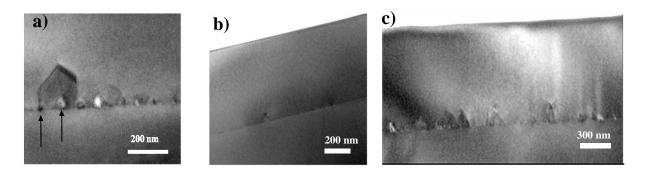

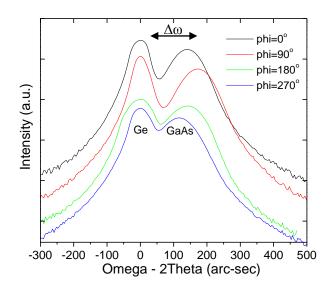

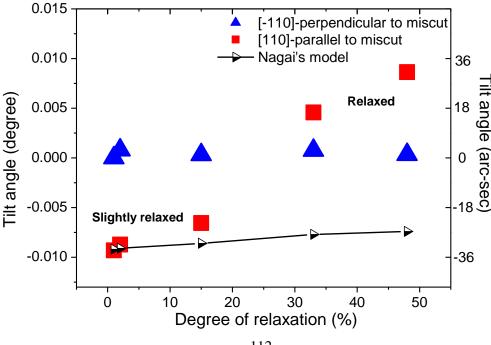

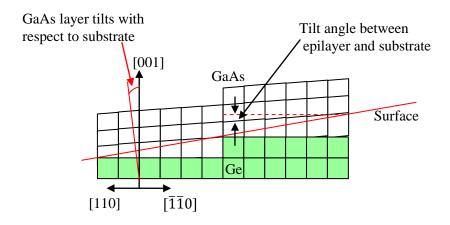

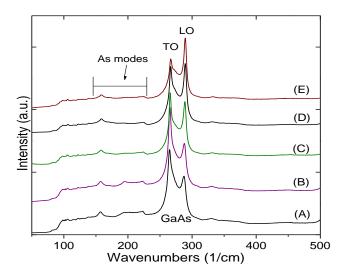

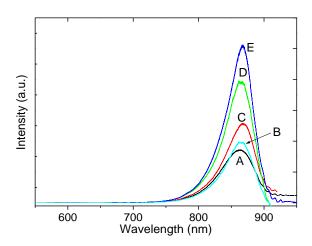

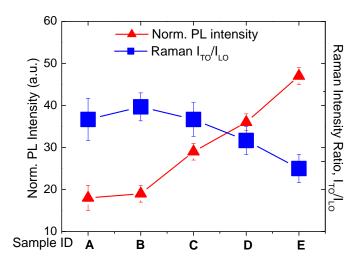

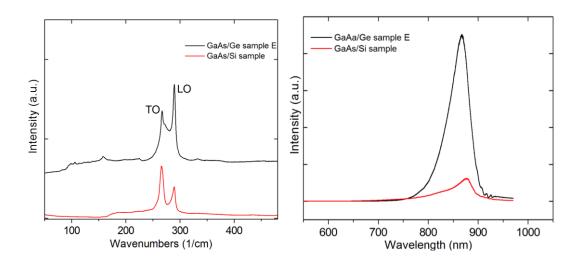

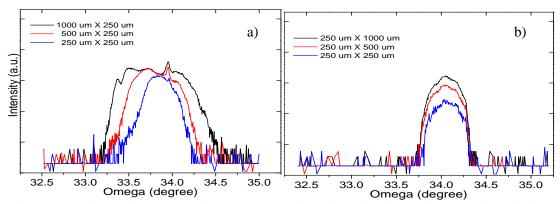

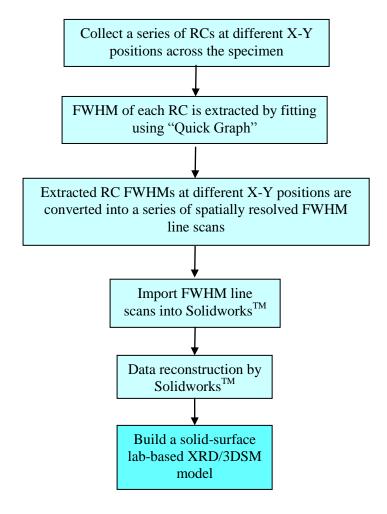

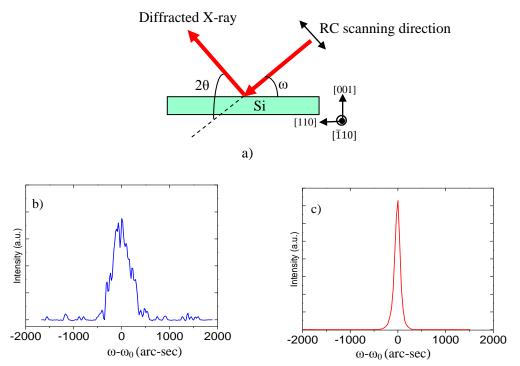

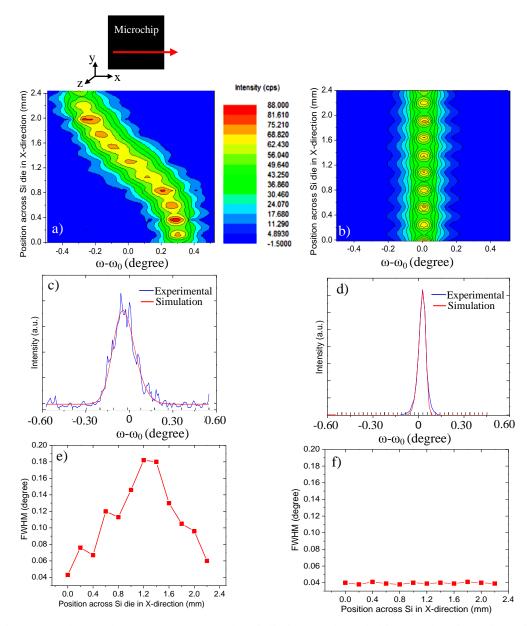

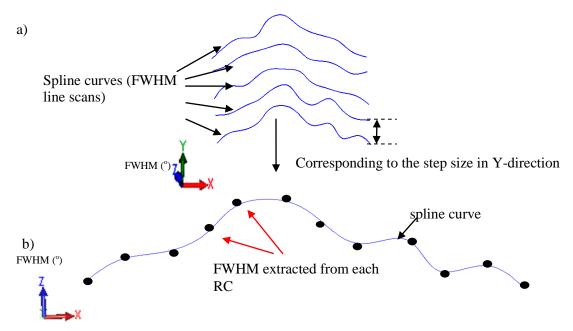

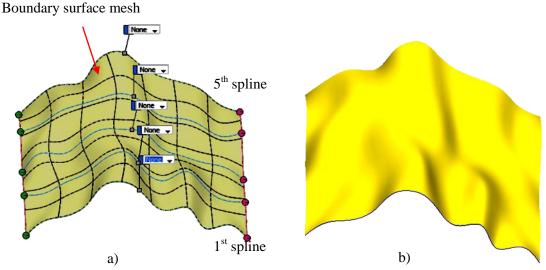

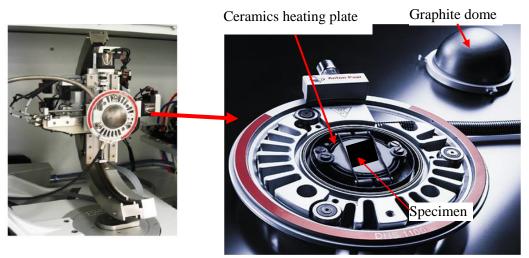

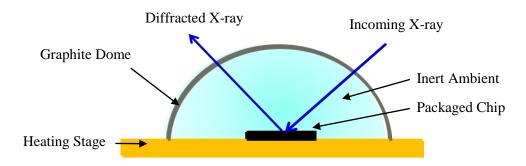

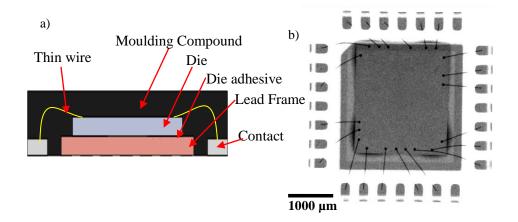

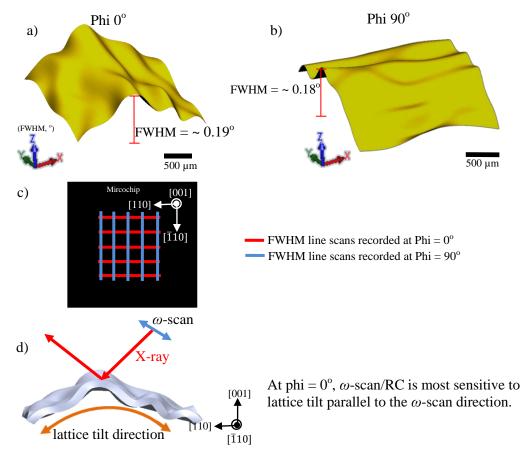

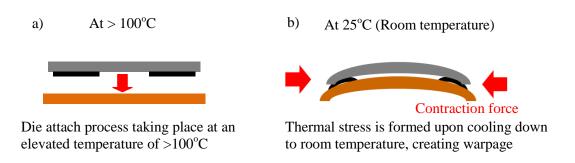

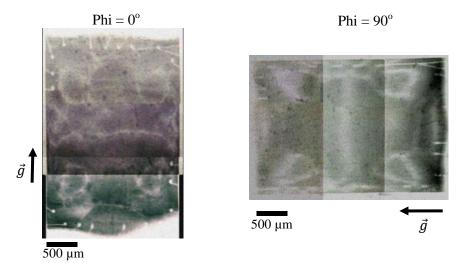

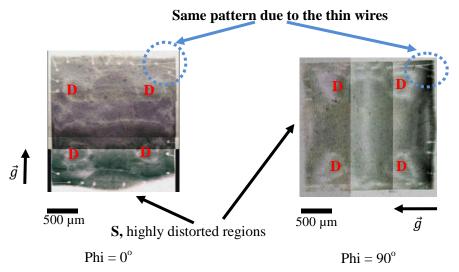

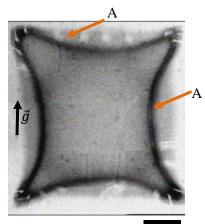

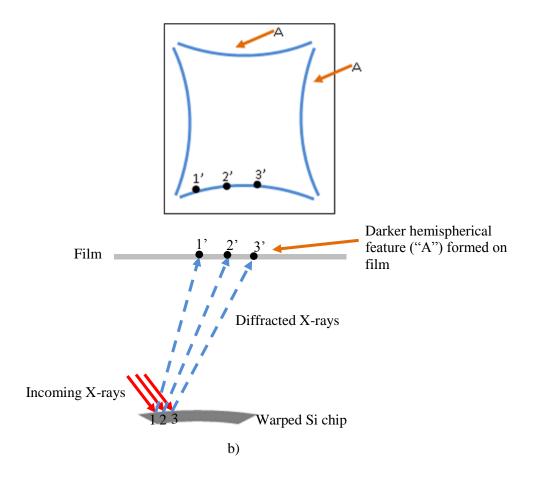

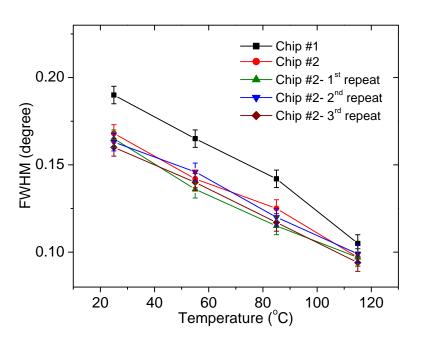

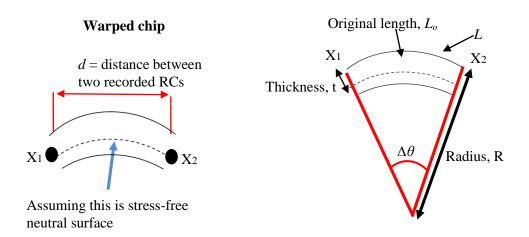

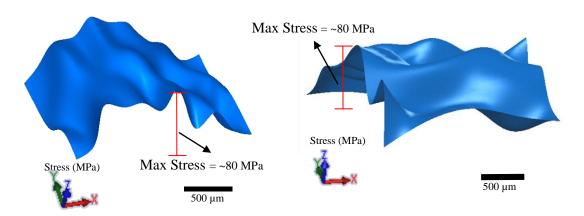

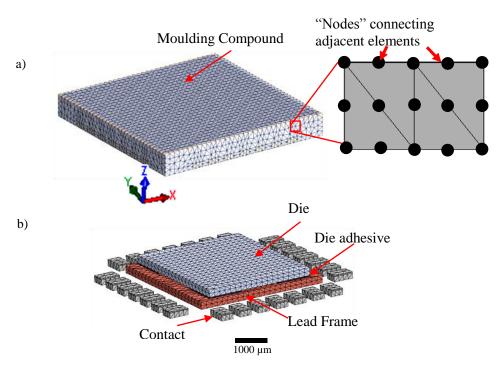

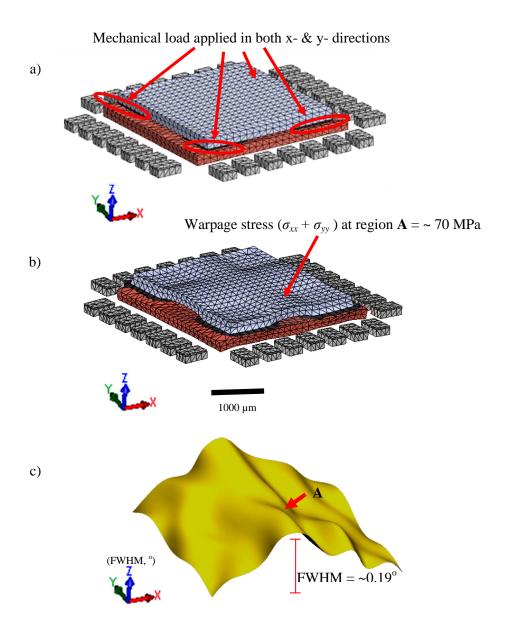

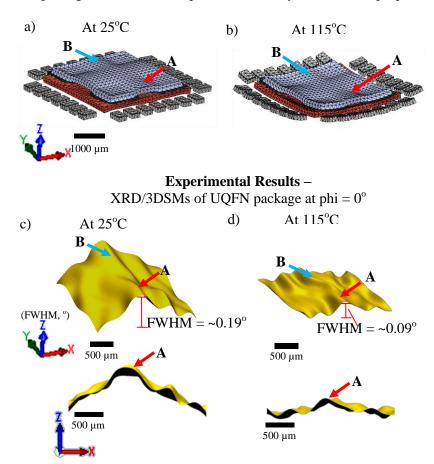

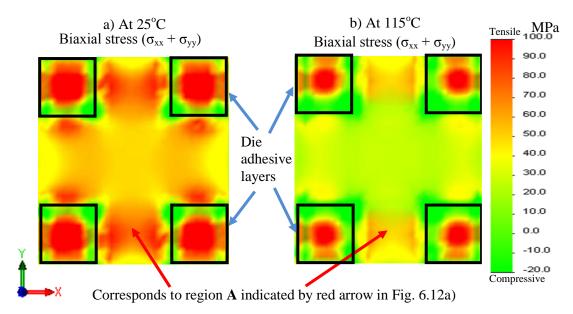

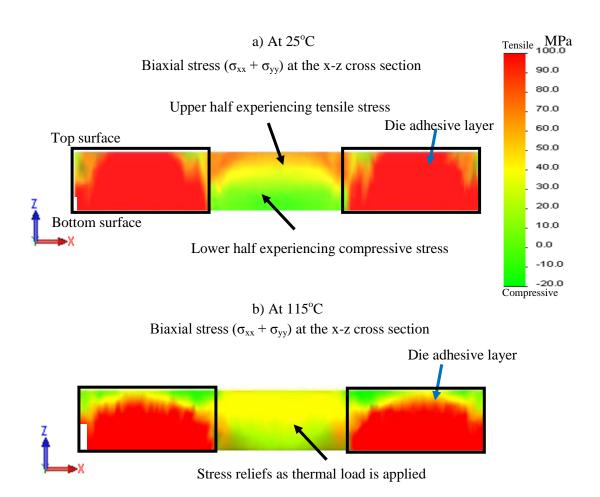

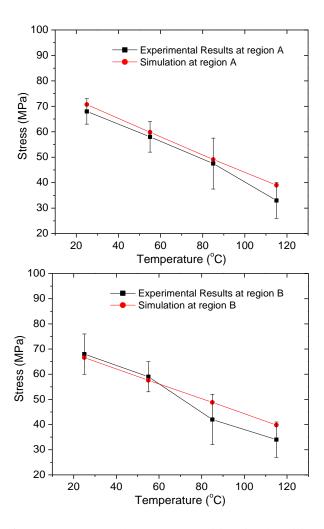

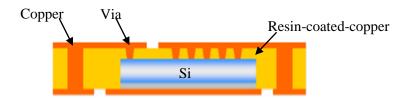

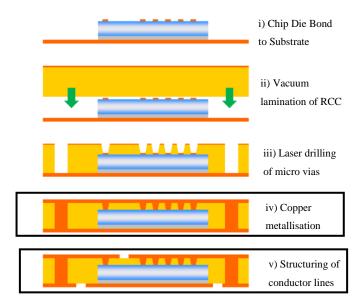

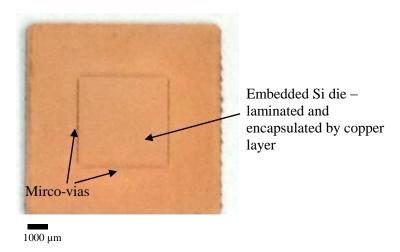

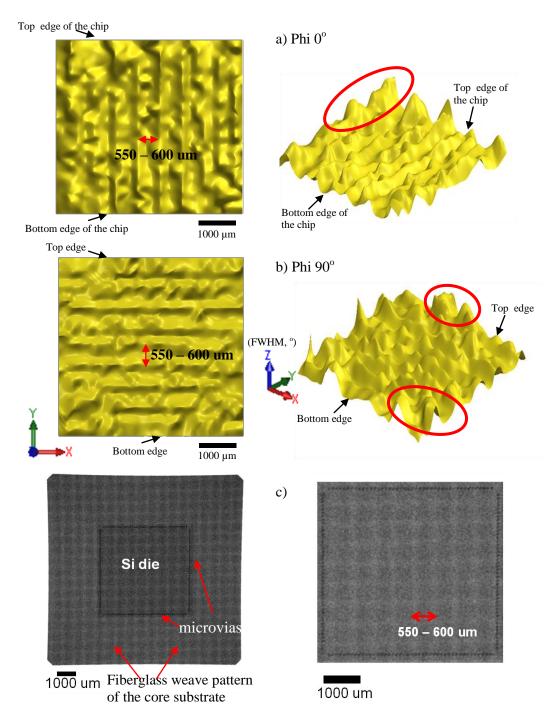

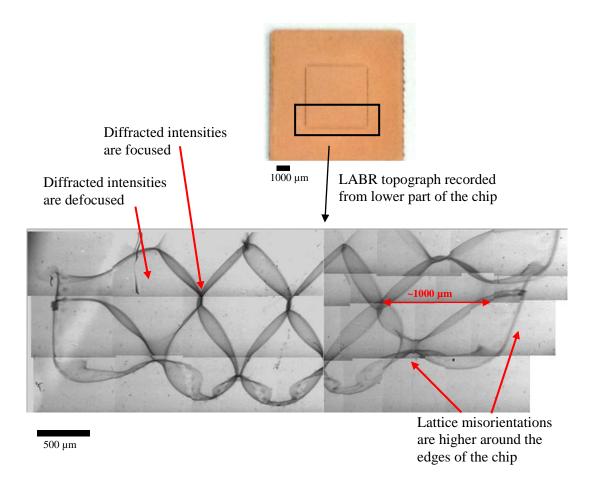

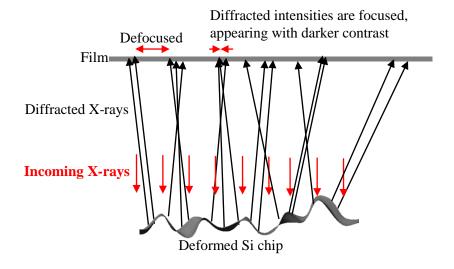

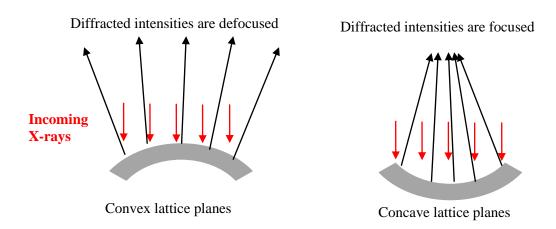

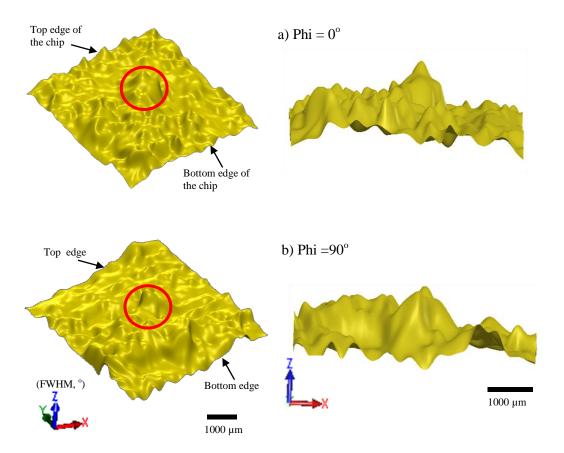

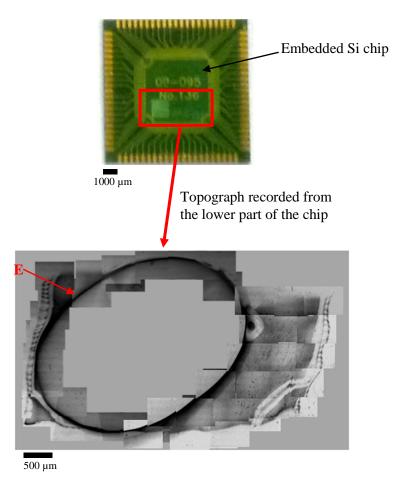

a magnetic field [49]. The radiation source of a typical synchrotron facility comprises of a linear electron accelerator, a storage ring and beam-lines as illustrated in Fig. 2.15 a). The electrons are initially accelerated by the linear accelerator to a few tens of MeV, and then fully energised by a booster to 2-10 GeV prior to electron injection into the storage ring. The injected electrons travel within the storage ring by lying on the orbit specified by the bending magnets [49]. In addition, insertion devices known as wigglers or undulators are often installed in the straight section between the bending magnets, and these act as enhancers of the radiation intensity. Light is emitted tangentially from the electron paths within the bending magnets or from insertion devices within the straight sections. The light emitted from the bending magnet components is of a continuous spectrum and is now useable at beamlines located off the central storage ring. The electromagnetic spectrum of a typical synchrotron radiation source is shown in Fig. 2.15b).