#### JOURNAL OF APPLIED PHYSICS

### Geometric linewidth and the impact of thermal processing on the stress regimes induced by electroless copper metallization for Si integrated circuit interconnect technology

P. J. McNally<sup>a)</sup> and J. Kanatharana *Microelectronics Group, Research Institute for Networks & Communications Engineering (RINCE)*, School of Electronic Engineering, Dublin City University, Dublin 9, Ireland

#### B. H. W. Toh and D. W. McNeill

School of Electronic & Electrical Engineering, Queens University of Belfast, Belfast BT9 5AH, United Kingdom

#### A. N. Danilewsky

Kristallographisches Institut, Universität Freiburg, Hebelstrasse 25, D-79104 Freiburg, Germany

#### T. Tuomi, L. Knuuttila, J. Riikonen, and J. Toivonen

Optoelectronics Laboratory, Helsinki University of Technology, PO Box 3500, 02015 TKK, Helsinki, Finland

#### R. Simon

Topo-beamline, Institut für Synchrotronstrahlung (ISS), Forschungszentrum Karlsruhe GmbH, Postfach 3640, D-76021 Karlsruhe, Germany

(Received 28 June 2004; accepted 8 September 2004)

Mechanical strains and stresses are a major concern in the development of copper-based on-chip metallization. Synchrotron x-ray topography (SXRT), micro-Raman spectroscopy, finite element modeling (FEM), and atomic force microscopy (AFM) have been used to examine the strain fields imposed by electroless Cu metallization on the underlying Si. As expected, we have observed enhanced strain regions close to the metal line edges. These strain fields tend to zero at annealing temperatures approaching 200 °C, and thereafter the magnitudes of the strain fields at 300 °C and 400 °C are much higher, implying a return to a higher strain regime. Although the strain transition point is slightly different from the SXRT result, the FEM results confirm the existence of a zero-strain transition point as a function of thermal anneal. We have also examined the generated stress in Si as a function of Cu linewidth L. We have found that the stress  $\sigma_{XX}$  due to the electroless copper metallization is empirically related to the Cu linewidth in terms of an exponential distribution. For Cu linewidths less than 20  $\mu$ m, the stress magnitudes increased with decreasing Cu linewidth due to the thermal stress in the absence of self-annealing, whereas the stress decreased with increasing linewidths in the range of  $60-100 \mu m$  due to a relief of the thermal stress possibly via the self-annealing effect. This self-annealing phenomenon was observed using AFM. It is observed that the stresses in the Si shifted to a compressive state after annealing at 400 °C. © 2004 American Institute of Physics. [DOI: 10.1063/1.1811780]

### I. INTRODUCTION

Copper is the leading on-chip interconnect metal for many integrated circuit (IC) applications due to the circuit speed advantage resulting from the higher electrical conductivity of Cu as compared to Al. The resistance-capacitance time constant associated with interconnect delays can be reduced by using a metal with a low resistivity and an interlevel dielectric (ILD) with a low dielectric constant. Copper has the second lowest resistivity of any nonsuperconductor,  $\rho = 1.69 - 1.77 \times 10^{-6} \Omega$  cm at 18 - 20 °C. However, it has been found that the appearance of stress and defects/ dislocations in copper metallization increases the resistivity.<sup>3</sup> Dislocations tend to invoke electron scattering at the surface, resulting in an increase of the metal resistivity. Stress induces

a phonon-electron scattering condition in the crystal lattice, which is different from the unstrained lattice and increases the resistivity.<sup>4</sup>

Mechanical strains and stresses are a major concern in IC processing. They have a large effect on the manufacturing reliability and the properties of devices. Besser<sup>5</sup> compared the mechanical stress obtained in Al and Cu interconnect lines of 0.18  $\mu$ m logic technology using the x-ray diffraction technique. It was found that the mechanical stresses of dual damascene patterns with ILD layers were much smaller in the Cu (286 MPa) than Al (411 MPa) because stressinduced voiding may be less prevalent in Cu lines. This result is similar to Kasthurirangan et al. Sullivan noted that the stresses in Cu metallization with a low-k dielectric ILD layer were much smaller than those with the higher-k silicon dioxide dielectric, primarily because of lower thermal conductivity and lower mechanical strength of the aforementioned low-k material.

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed; FAX: +353-1-7005508; Electronic mail: patrick.mcnally@rince.ie

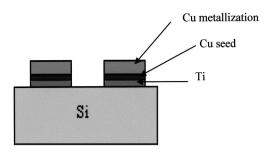

FIG. 1. A schematic outline of the electroless Cu deposition process.

The aim of this study is to ascertain the nature of Cu interconnect strains imposed on the underlying Si substrates for a typical electroless deposition technology. These strains were analyzed for varying Cu interconnect linewidths and were studied using the complementary techniques of micro-Raman spectroscopy ( $\mu$ RS), synchrotron x-ray topography (SXRT), finite element modeling (FEM), <sup>8,9</sup> and atomic force microscopy (AFM).

#### II. EXPERIMENTAL DETAILS

Electroless deposited Cu lines were patterned by a photolithographic lift-off process. The process steps are illustrated in Fig. 1. At the outset, a  $100\pm10$  nm thick Ti barrier layer was deposited using a dc magnetron sputtering method. An Argon carrier gas pressure of  $3.5\times10^{-3}$  mbar with a dc power of  $350~V\times0.8~A~(320~W)$  were used for the Ti deposition. Without breaking the vacuum, a 20 nm Cu seed layer was deposited on the samples. This seed was then used for subsequent electroless Cu deposition.

Nine Cu lines 100, 60, 40, 20, 10, 8, 6, 4, and 2  $\mu$ m geometrical width were deposited along the [110] direction of the Si (001) substrate. The spacing between these lines was typically  $150-200 \mu m$ . (001) surface orientation p-doped Si wafers were used in these experiments. The electroless Cu metallization samples were deposited based on the recipe from Shacham-Diamand. 10 Cu deposition is possible in an alkaline solution; therefore common chemicals such as sodium hydroxide NaOH and potassium cyanide are often added to increase the pH of the solution. However, sodium and potassium ions can accumulate in silicon dioxide, resulting in changes to its electrical properties. It is known that the sodium concentration must be limited to be less than 10<sup>9</sup> cm<sup>-2</sup>. Many researchers have found that tetra-methylammonium-hydroxide (TMAH) is the best alternative for Cu metallization in VLSI/ULSI technology. Following Ref. 10, TMAH was used to adjust the pH level of the solution to 12.3–12.7, and the temperature was adjusted to a range of 75-80 °C. The electroless Cu deposition solution components are shown in Table I. The deposition rate was ≈40 nm/min and the Cu electroless metal was grown to a thickness of 500 nm.

The synchrotron x-ray topography measurements were performed at ANKA, Institut für Synchrotronstrahlung (ISS), Karlsruhe, Germany, and HASYLAB-DESY, Hamburg, Germany (Hamburger Synchrotronstrahlungslabor am Deutschen Elektronen-Synchrotron) utilizing white beam synchrotron radiation. The rings operated at energies of 2.5 GeV

TABLE I. Electroless Cu deposition components and functions.

| Components                           | Function              | Quantity (in range) |

|--------------------------------------|-----------------------|---------------------|

| CuSO <sub>4</sub> ·5H <sub>2</sub> O | Provides Cu (II) ions | (0.05-0.1)M         |

| 2,2'-dipyridyl                       | Stablizer             | (0.5-1.0)M          |

| EDTA                                 | Complexing agent      | (0.1)M              |

| НСНО                                 | Reducing agent        | (0.01-0.1)M         |

| Triton® x-100 Surfactant             |                       | 0.5%-2%             |

and 4.45 GeV, respectively, and at typical beam currents of 100-200 mA. The standard Laue or Bragg pattern of topographs<sup>11</sup> was recorded on Geola/Slavich holographic high-resolution (grain size ~40 nm) VRP-M films, or lower (~1 μm grain size) Kodak SR-45 Professional x-ray film. The distance from the sample to the film was 50 mm for all samples. The samples were set parallel to the film for the large area back reflection (LA-BRT) or back reflection section (BRST) geometries and the beam was collimated by slits a size of  $\sim 20 \,\mu\text{m} \times 1.5 \,\text{mm}$  for the section arrangement. 8,9 The samples were turned 180° and tilted 18° to perform the section transmission (ST) experiments. 11 All samples were examined at room temperature. The back reflection topographs were generated by the 228 harmonic reflection with a penetration depth  $t_p$  of 65.7  $\mu$ m. The ST images were generated by the 111 reflection. Magnified images of the x-ray topographs have been captured from the original x-ray films using a system comprising of a microscope with a charge-coupled device (CCD) camera, frame grabber, and appropriate software.

Geometrical resolution is governed by the synchrotron beam divergence. It is given by  $\delta = HL/D$ , where H is the radiation source dimension, L is the source-sample distance, and D is the sample-film distance 12 and usually lies in the  $1-2 \mu m$  range at the beamlines used in this study. Since Tuomi et al. introduced synchrotron x-ray topography with high-resolution results in 1974,11 many scientists have used SXRT to investigate crystalline defect structure. Subsequently, the theoretical basis for the contrast mechanisms has been elucidated by e.g. Authier et al. 13 Blech and Meieran have explained the extinction and anomalous contrast phenomena in x-ray topography images for strained Si during device processing. 14-17 In a later work, McNally et al. 18 provided evidence that strain magnitudes as low as  $|\varepsilon|=6$  $\times 10^{-5}$  could be easily imaged using SXRT. These strain levels correspond to equivalent Si minimum observable stress magnitudes of  $|\sigma|_{\min} \sim 10$  MPa.

Micro-Raman spectroscopic analysis was performed on a Jobin-Yvon LabRam800 system, used in backscattering configuration in which only the longitudinal optical modes are activated for both the substrate and the epitaxial layers. A 488 nm Ar<sup>+</sup> laser with a spot size of 1  $\mu$ m which probes right through to the Si substrate was used and the different positions on each sample were scanned for 5 min each. Longer scans (of 15 min) were also carried out for control purposes. An automatic *X-Y* stage with a minimum movement of 0.1  $\mu$ m was used to move the sample during the measurements. A plasma line at 560 cm<sup>-1</sup> was used as an internal calibration of the measurements to eliminate envi-

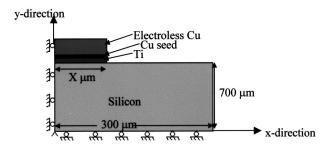

FIG. 2. Typical FEM geometry and model boundary conditions for the metallized sample.

ronmental and CCD temperature fluctuations during the experiments. The spatial strain distribution in the Si sample can be examined from the measured frequencies of Raman peaks compared with those of a strain-free reference Si sample at 521 cm<sup>-1</sup>. The relationship between Raman shift and linear strain was derived by De Wolf<sup>19</sup> and is given by

$$\sigma_{XX} \text{ (MPa)} = -434\Delta\omega \text{ (cm}^{-1}), \tag{1}$$

where  $\sigma_{XX}$ =the uniaxial stress in MPa and  $\Delta\omega$ =the Raman shift between the measured Raman peak of strained Si  $(\omega_j)$  compared with that of strain-free Si  $(\omega_0)$ ,  $\Delta\omega = \omega_j - \omega_0$ ,  $\omega_j$ =the measured frequency of the silicon Raman peak and  $\omega_0$ =the frequency of the silicon Raman in the stress-free state.

In this study, the experiments were performed by pointing the laser along the Si [001] direction with the Cu lines running along the [110] direction and measuring the strains along the  $[\bar{1}10]$  direction. Using appropriate curve-fitting software on this high-resolution  $\mu$ RS system, shifts in the Si Raman phonon peak position as low as 0.04 cm<sup>-1</sup> can be reliably detected. Using Eq. (1) above, this corresponds to an uncertainty in measured stress values of  $\sim$ 17.5 MPa. This value of 17.5 MPa is also the lowest detectable magnitude of stress.

The FEM technique is used to compare the influence of linewidths on the electroless Cu metallization and to compare with the SXRT and  $\mu$ RS results. For speed and ease of simulation, two-dimensional (2D) plane strain finite element models have been employed in these experiments. The geometry, dimensions, and boundary conditions of the metallized samples are illustrated in Fig. 2. The metallization with linewidths of 0.1, 0.5, 1.0, 2.0, 5.0, 10, 20, 40, 60, and 100  $\mu$ m were simulated using FEM; therefore the dimension X in Fig. 2 is actually the half-width of the line. This ensured a useful spread of data points across the experimental data range and in between the experimental data points as well. Approximately 100 000 nodes were used to achieve the simulation. The finite element analyses were carried out using Quickfield® Professional version 4.2.20 The materials considered in these models are the Si substrate, the Ti barrier layer, and Cu. These materials are assumed to be isotropic and linearly elastic. Their physical properties are given in Table II.

Finally, AFM analysis was performed using a Pacific

TABLE II. Materials properties for finite element analysis (Refs. 1, 5, 6, 8, 9, and 22).

| Materials | Young's modulus $(E \times 10^9) \text{ N/m}^2$ | Poisson's ratio (ν) | Coefficient of thermal expansion $(\alpha, \times 10^{-6})/{^{\circ}}\mathrm{C}$ |

|-----------|-------------------------------------------------|---------------------|----------------------------------------------------------------------------------|

| Si        | 112.4                                           | 0.28                | 2.5                                                                              |

| Ti        | 116.0                                           | 0.34                | 8.9                                                                              |

| Cu        | 123.0                                           | 0.33                | 17.0                                                                             |

Nanotechnology Series 2002 AFM system. A contact mode with a 2 Hz scan rate and 2.15  $\mu$ m  $\times$  2.15  $\mu$ m sampling area were employed in this experiment.

#### III. RESULTS AND DISCUSSION

## A. Geometric linewidth dependence of the strain in Si induced by the electroless Cu metallization process

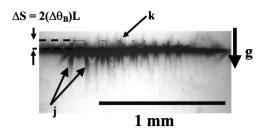

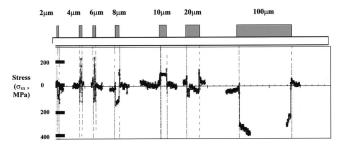

The very strong contrast near the metal line edges in the BRST of Fig. 3 confirms the dependence of the strain fields with varying electroless Cu linewidths. This topograph shows the very typical black and white contrast (extinction contrast) within the highly strained Si substrate near the edges of the metal lines, which are due to the imposed strain fields in the diffracting Si (Ref. 15)—see Arrows **j**. A rough estimation of the stress/strain imposed on Si for electroless Cu deposition is based on a calculation of the thermal stress due to the large difference in CTE (coefficient of thermal expansion) since the temperature of the deposition solution was  $\sim 80$  °C during the Cu deposition. The calculation of the maximum value of stress for a uniform film when the behavior is purely elastic is given by

$$\sigma_{\text{max}} = \Delta \alpha E \Delta T / (1 - \nu), \tag{2}$$

where  $\sigma_{\rm max}$ =the maximum generated thermal stress,  $\Delta\alpha$  = the difference of CTE between Si and Cu  $\approx$  13.6 ppm/°C,  $E={\rm Young's}$  modulus  $\approx$ 162.3 GPa, and  $\nu={\rm Poisson's}$  ratio =0.28. Using Eq. (2), the estimation of maximum stress is of the order of 100 MPa. It must be emphasized that this is only a rough qualitative estimate. A more complete analysis would have to include the crystallographic anisotropy of Si together with the interaction of the anisotropic elastic properties of Cu. To confirm this, the authors performed a number of x-ray diffraction experiments (XRD) on the electroless Cu both before and after annealing. The XRD measurements

FIG. 3.  $\overline{22}8$  BRST of wafer with 500 nm thick electroless Cu metallization, 20 nm Cu seed, 100 nm Ti on Si using lift-off pattern. The positions of the Cu lines of widths 100, 60, 40, 20, 10, 8, 6, and 4  $\mu$ m, left to right, respectively, are indicated. The projection of the diffraction vector  ${\bf g}$  on the recording film is also shown.

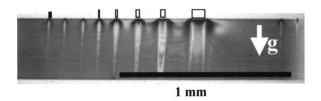

FIG. 4. 111 ST image of same sample as per Fig. 3. The position of the Cu lines of widths 100, 60, 40, 20, 10, and 4  $\mu$ m, right to left, respectively, are indicated. The projection of the diffraction vector  ${\bf g}$  on the recording film is also shown.

were performed using a Philips X'Pert PRO XRD system with a model PW3040 (mppc) x-ray generator and a model PW3050/65 goniometer. The XRD patterns were compared with standard patterns from the Powder Diffraction File Release 2000, Data Sets 1-50 plus 70-88, International Centers for Diffraction data. The data confirmed that the Cu electroless plating technique created Cu predominantly orientated along  $\langle 111 \rangle$  and  $\langle 220 \rangle$  planes in almost equal quantities. Due to this multiple texturing, it was felt that a simplistic first-order estimation of induced stresses, based on an isotropic model was justified.

In addition to the extinction contrast, the severely strained Si near the edge of Cu lines also appears via the orientational contrast mechanism in the 228 BRST of Fig. 3. The orientational contrast is observed as a lifting of the image of highly strained Si near the line edges above the image of the rest of the Si (Arrow k). The orientational contrast can be observed if this misorientation exceeds the x-ray beam divergence  $\Delta \phi$ , which is equal to 0.238 mrad for beamline F-1 in HASYLAB, and represents the worst case limit in these experiments. The height of the orientational contrast shift is  $\Delta S = 2(\Delta \theta_{\rm R})L$ , where  $\Delta \theta$  is the effective misorientation, L is the distance between sample and film (50 mm in this case). This can yield quantitative estimates for the magnitude of strain in the underlying silicon as described, in that  $\Delta \theta_{\rm B} \cong \gamma_{xy}$ . In the case of the 100  $\mu$ m wide Cu line,  $\Delta S$  $\approx 0.05$  mm, therefore,  $\Delta \theta_{\rm B} \cong \gamma_{xy} \cong 5 \times 10^{-4}$  or 0.05%. This implies that the magnitudes of shear stresses are given by  $|\tau_{xy}| = G|\gamma_{xy}|$ , where G=shear modulus=162 GPa.<sup>21</sup> Thus, the limit on the stress magnitudes is of the order of  $|\tau_{xy}|$  $\approx$  81 MPa. In the case of the 20  $\mu$ m wide Cu line,  $\Delta S$  $\approx 0.08$  mm,  $\Delta \theta_{\rm B} \cong \gamma_{xy} \cong 8 \times 10^{-4}$  or 0.08%. Thus,  $|\tau_{xy}|$  $\approx$  130 MPa. These are both of the same order of magnitude as the stresses estimated using Eq. (2).

From both the calculation and experiments, the orientational contrast shows that the stress near the Cu line edge increases with decreasing Cu linewidth. The relationship between the Cu linewidth and the stresses near the line edge can be clarified using FEM, which will be described in a later section. A ST image of the same region of the sample (Fig. 4) illustrates severe destruction of the Pendellösung fringes, which implies high strain fields in the Si crystal. Some orientational contrast is visible in this image. However, the misorientation is too difficult to measure reliably in this case. The strain fields may fall in magnitude with increasing Cu linewidth, but interestingly, the spatial extent of

FIG. 5. The normal stress (indicated by  $S_{XX}$ ) in the Si substrate just below the Si/metal interface due to the 500 nm thick electroless Cu metallization as a function of Cu linewidths, as measured using  $\mu$ RS. Pre annealed sample. The locations of the Cu lines are indicated, whose linewidths are 2, 4, 6, 8, 10, 20, and 100  $\mu$ m, respectively, left to right. Positive and negative signs represent tensile and compressive stresses, respectively.

the strain fields, as observed via the extinction contrast annihilation of the Pendellösung fringes, lies deeper into the substrate with increasing linewidth.

The micro-Raman spectroscopy ( $\mu$ RS) measurements were also carried out on these 500 nm thick electroless Cu metallization samples. In the preannealed case the normal stresses  $\sigma_{XX}$  measured using  $\mu$ RS for 2, 4, 6, 8, 10, 20, and 100  $\mu$ m Cu linewidths and are illustrated in Fig. 5. It is clear that the stresses imposed in the Si substrate due to the Cu metallization are dependent on the Cu linewidth. The μRS results indicate that the stresses build up near the edge of the metal line. For a comparative analysis, the behavior of the strains in the underlying Si were observed in a  $\sim 0.5 \mu m$ wide region just outside the edge of the metal lines. This region was selected in order to eliminate the possibility of any interaction of the probe laser with the overlying metallization (e.g., through absorption, etc.). The induced strains tend to be at their greatest magnitude at the material discontinuity represented by the metal edge. If the induced strain in the Si at the outside of the metal line is tensile, then the region just inside the metal line tends to be under compressive stress, or vice versa. This strain sign reversal was observed for all observed and simulated linewidths in this study.

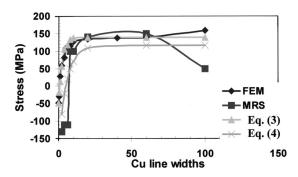

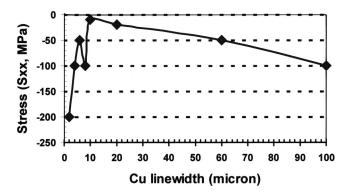

The relationship between the Cu linewidth and normal stress  $\sigma_{XX}$  in the Si 0.5  $\mu$ m away from the outer edge of the Cu line is shown in Fig. 6. The normal stresses imposed in the Si wafer due to the electroless Cu metallization are com-

FIG. 6. A comparison of the normal stress in the X direction ( $\sigma_{XX}$ ) from experimental  $\mu$ RS data, the FEM simulation, and the empirical estimations of Eqs. (3) and (4). The stress was measured 0.5  $\mu$ m away from the outer edge of the Cu line. Preannealed sample. Positive and negative signs represent tensile and compressive stresses, respectively.

pressive near the outer edge of the Cu lines when the Cu linewidth is less than  $\sim\!10~\mu\mathrm{m}$ . The normal stress in Si changes to tensile stress when the Cu linewidth is larger than  $\sim\!10~\mu\mathrm{m}$ . In addition, when the Cu linewidth is larger than  $\sim\!20~\mu\mathrm{m}$ , the magnitude of the tensile stress seems to be almost independent of the Cu linewidth up to a linewidth  $L\sim\!60~\mu\mathrm{m}$ . An empirical estimate of the imposed stress as a function of Cu linewidth indicates that the stress  $\sigma_{XX}$  due to the electroless Cu metallization is related to the Cu linewidth in terms of an exponential distribution:

$$\sigma_{XX} = 139.5 - 195.5 \exp(-\text{Cu linewidth/}2.3) \text{ MPa},$$

(3)

where Cu linewidth is given in microns. This result correlates with the FEM simulation, where  $\sigma_{XX}$  is given by the qualitatively similar

$$\sigma_{XX} = 115.6 - 281.4 \exp(-\text{Cu linewidth/5.5}) \text{ MPa.}$$

(4)

A comparison of the normal stress  $\sigma_{XX}$  from the experimental µRS data, the calculated FEM distribution and the empirical estimates of Eqs. (3) and (4) is also shown in Fig. 6. This data clearly indicate that the generated stress versus linewidth L tendency is a function of the geometrical arrangement. The  $\mu$ RS data for  $60 < L < 100 \mu$ m does clearly indicate that the stress imposed on the Si due to the Cu metallization decreases more rapidly than predicted as a function of linewidth. This phenomenon could be explained in terms of a self-annealing effect in the Cu line.<sup>22</sup> Graham *et* al. 23 found that the copper self-annealing is a function of the copper linewidths in that the smaller Cu linewidths require a higher activation energy to achieve full recrystallization than the wider ones. In addition, Lagrange et al.<sup>24</sup> investigated the Cu self-annealing phenomenon as a function of the Cu thickness, and found that the self-annealing is slowed down for a thinner Cu layer due to physical restrictions, while the thicker layer approached the grain size of recrystallized copper, forcing growth to proceed in two dimensions (2D). Therefore, the stress relief tends to be lower when the layer is thinner due to the physical limitation. Brongersma et al.<sup>25</sup> agrees with Lagrange et al. Nevertheless, Brongersma et al. also mentioned that a very rapid primary crystallization occurred from the top surface down just after deposition, which was then followed by a slower lateral recrystallization producing large secondary grains. The physical limitation of the Cu lines could explain the self-annealing phenomenon as a function of the Cu volume in that the recrystallization process could not occur when the Cu linewidth becomes very small since the density of grains per volume is not large enough for the recrystallization process to occur. Therefore, the stress in Si due to the small Cu linewidths is still frozen within, whereas the stress in the Si due to the wider Cu metallization is relieved by the self-annealing process. From the  $\mu$ RS and FEM results in Fig. 6, it can be argued that the stress generated in the Si is mainly due to the geometrical effect without self-annealing at  $L < 20 \mu m$ , whereas the selfannealing may influence the stress imposed on Si for  $60 < L < 100 \mu m$ .

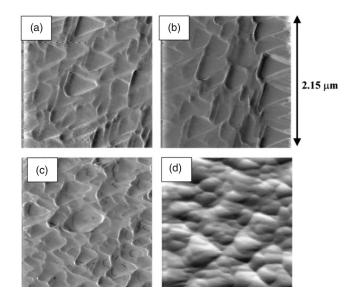

To investigate the grain size/density in the copper as a function of the Cu linewidths due to the self-annealing effect, AFM was performed. A representative selection of AFM re-

FIG. 7. AFM results for the Preannealed electroless Cu as a function of the Cu line widths of (a) 2  $\mu$ m, (b) 4  $\mu$ m, (c) 60  $\mu$ m, and (d) 100  $\mu$ m.

sults for Cu linewidths of 2, 4, 60, and 100  $\mu$ m are illustrated in Figs. 7(a)–7(d), respectively. The AFM images for the other lines with L=20  $\mu$ m are similar to Fig. 7(a) or 7(b). The AFM results show that the grains within the Cu lines exhibit (111) faceting (hence the triangular symmetry) and have sizes of about 0.3–0.5  $\mu$ m for linewidths of 2  $\mu$ m–20  $\mu$ m. Thereafter one observes the formation of copper clusters when the Cu linewidth gets bigger, i.e., L>60  $\mu$ m. This implies that the cluster formation is related to at least a partial relief of stress in the Cu lines and thus also in the underlying Si. This result correlates with the suggestion that the self-annealing phenomenon influences the stress in Si only when 60<L<100  $\mu$ m.

# B. Temperature dependence of the strain fields in Si substrate induced by the electroless Cu metallization process

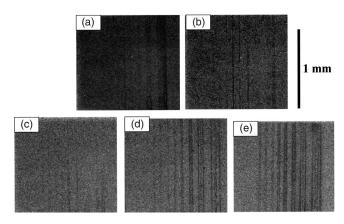

To study the temperature dependence of the stress distributions in the Si wafers induced by the Cu metallization process, the samples were mounted on a heating stage. The x-ray topographs were then recorded at room temperature 100, 200, 300, and 400 °C. The faster Kodak film used in this instance, as any imaging in the presence of small thermal variations in the heating stage, would lead to blurred topographic images on the  $\sim$ 60 times slower VRP-M film. Large area back reflection topographs are shown in Fig. 8. The strain fields imposed by the metallization in the underlying Si are observed as the parallel (mostly) black lines, corresponding to enhanced strain regions close to the metal line edges. Although initially weak at room temperatures (i.e., in the as-deposited condition), the images of the strain fields become even more difficult to discern at temperatures approaching 200 °C [Fig. 2(c)]. This is most likely due to the fact that the strains go through a minimum near this temperature. Thereafter the images of the strain fields for 300 °C and 400 °C are much stronger, implying a return to a higher strain regime. Riedel et al. 26 investigated this phenomenon in 500 nm thick Cu film deposited by chemical vapor deposi-

FIG. 8.  $\overline{22}$ 8 LA-BRT images for the electroless Cu samples, which have been taken at the following temperatures: (a) room temperature, (b) 100 °C, (c) 200 °C, (d) 300 °C, (e) 400 °C. The projection of the diffraction vector **g** on the recording film is also shown.

tion. Although the Cu was deposited by a different technique, a similar phenomenon was observed wherein the strain proceeded through a zero point as the strain due to the deposited Cu changed from tensile to compressive during heating. This annealing temperature vs stress transformation phenomenon has been simulated using FEM.

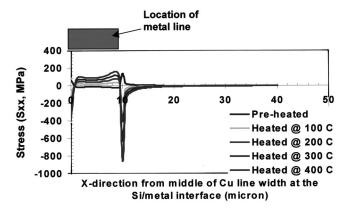

By way of example, we now illustrate the FEM carried out for the 20  $\mu$ m linewidth Cu metallization, which was annealed at 100, 200, 300 and 400  $^{\circ}\text{C}.$  A comparison of the stresses in the Si wafer for the Cu metallization before and after annealing along the Si/metal interface is shown in Fig. 9. The normal stress  $\sigma_{XX}$  is only shown here, but the FEM results indicate that the stress distributions in the Si wafer at the outer edge of the Cu line are compressive for  $\sigma_{XX}$  and  $\sigma_{YY}$ , and tensile for  $\tau_{XY}$  at room temperature. After the sample was heated at elevated temperature from 100 to 400 °C, the stress transformed into the opposite state (i.e., tensile became compressive, and compressive became tensile). This strain-reversal effect was observed in all simulated Cu linewidths. Although the strain transition point is slightly different, this FEM simulation confirms the correlation of the strain transition phenomenon with the SXRT results of Fig. 8.

FIG. 9. The FEM simulation of the induced normal strain  $S_{XX}$  for the Preannealed and Annealed 20  $\mu$ m wide copper line along the *x*-direction from the middle of the metal line (X=0  $\mu$ m) to the edge of the metal (X=10  $\mu$ m) at the Si/metal interface (X=150  $\mu$ m). Due to symmetry, only half of the linewidth is simulated.

FIG. 10. The measured normal stress  $\sigma_{XX}$  in Si imposed due to the Cu metallization near the edge of the metal line after annealing at 400 °C as a function of Cu linewidth measured 0.5  $\mu$ m outside the outer edge of each Cu line

To study the effect of annealing on electroless Cu metallization as a function of the linewidth, a set of metallized 500 nm thick electroless Cu samples were annealed at 400 °C and measured using  $\mu$ RS. The relationship between the Cu linewidth and normal stress  $\sigma_{XX}$  in the Si 0.5  $\mu$ m outside the outer edge of each Cu line is shown in Fig. 10. In this case, the normal stresses in the Si near the outer edge of the Cu lines are shifted to the compressive state for the entire range of the Cu linewidths after annealing. The only exception to this is for the  $L=8 \mu m$  line—the data as shown on Fig. 10 for that point are real and do not represent noise. However, the overall shape of the curve for the relationship of the Annealed sample stress and Cu linewidth is similar to that for the Preannealed sample (Fig. 6) in that the stresses become more compressive with decreasing Cu linewidths for linewidths below  $\sim 10 \, \mu \text{m}$ . Subsequently, the tendency changes as the normal stresses decrease with increasing Cu linewidth in the  $20-100 \mu m$  range.

Again, the AFM measurement was performed using the same system and the same settings as previously used to investigate the grain size/density of the Cu as a function of the annealed Cu linewidths after annealing at 400 °C. These AFM results show that the grain sizes of the Cu lines are of a similar tendency to the AFM results of the preannealed case [Figs. 7(a)-7(d)]. In this case, the Cu grains also show (111) faceting with grain sizes of  $0.3-0.35 \mu m$  for linewidths less than 10  $\mu$ m and thereafter start forming copper clusters with an average grain size of about 0.2  $\mu$ m when the Cu linewidth gets bigger, i.e.,  $L > 60 \mu m$ . This suggests the stress imposed on the Si substrate, as a function of the Cu linewidths, should be about the same if the stress were correlated to Cu grain size. However, this result does not appear to explain the shift of the stress in the Si due to the Cu lines to a compressive state. The shift of the stress imposed on the Si due to the annealing step is possibly due to the thermal mismatch between the Si, the metal layers, and the possibly new intermetallic compounds created in the metal layers at the interface between the barrier film and the Cu layer.

#### **IV. CONCLUSIONS**

Synchrotron x-ray topography, micro-Raman spectroscopy, finite element modeling, and atomic force microscopy have been used to examine the stress regimes imposed in the underlying Si substrate as a result of electroless Cu deposition. The SXRT technique showed that the stresses in Si induced by the electroless Cu metallization were intense at the edge of the metal lines and were of the order of 100 MPa near the outer edge of the interface between Si and the Cu metal layers. This result agrees with the FEM simulations. The SXRT topographs indicated that this stress was mostly relieved by annealing at 200 °C. Although the strain transition point is slightly different from the SXRT result the FEM results confirmed the existence of a zero-strain transition point as a function of thermal anneal.

The stress distributions in Si as a function of the Cu linewidth for  $2 \le L \le 100~\mu m$  electroless Cu lines were investigated. The FEM result is in accordance with the  $\mu RS$  results. For Cu linewidths less than  $20~\mu m$ , the stress increased with a decrease of the Cu linewidth due to the thermal stress in the absence of self-annealing, whereas the stress decreased with increasing linewidths in the range of  $60-100~\mu m$  due to a relief of the thermal stress possibly via the self-annealing effect. This self-annealing phenomenon was observed using AFM.

The effect of the annealing process on the Cu metallization was investigated using the  $\mu RS$  and AFM techniques. It was observed that the stresses in the Si shifted to a compressive state after annealing at 400  $^{\circ} C.$  In addition, the relationship between the stress and the Cu linewidth of the preannealed sample displays the same tendency as that of the annealed sample.

#### **ACKNOWLEDGMENTS**

This work was supported by the IHP Contract No. HPRI-CT-2001-00140 of the European Community. The support of T. Wroblewski and C. Paulmann at HASYLAB beamline F-1 and Christophe Frieh at the Topo-beamline, ISS (Institut für Synchrotron-Forschung, Forschungszentrum Karlsruhe) was gratefully acknowledged, and was supported by the IA SFS Contract No. RII3–CT-2004–506008 of the European Commission.

- <sup>1</sup>J. R. Lloyd, J. Clemens, and R. Snede, Microelectron. Reliab. **39**, 1595 (1999).

- <sup>2</sup>P. Singer, Semicond. Int. **1988**, 91.

- <sup>3</sup>Copper-Fundamental Mechanisms for Microelectronic Applications, edited by S. P. Murarka, I. V. Verner, and R. J. Gutmann (Wiley, New York, 2000).

- <sup>4</sup>Multilevel Interconnect Technology, edited by G. K. Rao (McGraw-Hill, New York, 1993).

- <sup>5</sup>P. R. Besser, in *Stress Induced Phenomena in Metallization*, edited by Oliver Kraft, Edward Arzt, Cynthia A. Volkent Paul S. Ho, and Hidekozu Orbay AIP Conf. Proc. No. 491, (AIP, Melville, NY, 1999), p. 229.

- <sup>6</sup>J. Kasthurirangan, Y. Du, P. Ho, C. Capasso, M. Gall, D. Jawarani, R. Hernandez, and H. Kawasaki, *Stress Induced Phenomena in Metallization*, Ref. 5, p. 304.

- <sup>7</sup>T. D. Sullivan, in Ref. 5, p. 39.

- <sup>8</sup>J. Kanatharana et al., J. Phys. D **36**, A60 (2003).

- <sup>9</sup>J. Kanatharana et al., Microelectron. Eng. 65, 209 (2003).

- <sup>10</sup>Y. Shacham-Diamand, V. Dubin, and M. Angyal, Thin Solid Films 262, 93 (1995).

- <sup>11</sup>T. Tuomi, K. Naukkarinen, and P. Rabe, Phys. Status Solidi A 25, 93 (1974).

- <sup>12</sup> High Resolution X-ray Diffractometry and Topography, edited by D. K. Bowen and B. K. Tanner (Taylor & Francis, London, 1998), pp. 189–200.

- <sup>13</sup>X-Ray and Neutron Dynamical Diffraction: Theory and Applications, edited by A. Authier, S. Lagomarsino, and B. K. Tanner (Plenum, New York, 1996).

- <sup>14</sup>E. S. Meieran and I. A. Blech, J. Appl. Phys. **36**, 3162 (1965).

- <sup>15</sup>I. A. Blech and E. S. Meieran, J. Appl. Phys. **38**, 2913 (1967).

- <sup>16</sup>E. S. Meieran and I. A. Blech, J. Appl. Phys. **43**, 265 (1972).

- <sup>17</sup>E. S. Meieran and I. A. Blech, Phys. Status Solidi **29**, 653 (1968).

- <sup>18</sup>P. J. McNally*et al.*, J. Mater. Sci.: Mater. Electron. **10**, 351 (1999).

- <sup>19</sup>I. De Wolf, J. Raman Spectrosc. **30**, 877 (1999).

- <sup>20</sup>http://www.quickfield.com

- <sup>21</sup>Handbook for Hybrid Microelectronics Materials, edited by J. A. King (Artech, Boston, 1988).

- <sup>22</sup>M. Yamada, K. Yoshie, S. Yamaguchi., H. Niwa, M. Hosaka., T. Kouno, Y. Mizushima, N. Misawa, K. Kakuta, T. Suzuki., R. Shinohara., M. Ikeda, H. Kudo, and A. Tsukune, *Advanced Metallization Conference in 1998 (AMC 1998)*, edited by G. S. Sandhu*et al.*, MRS Symposia Proceedings No. 14 (Materials Research Society, Pittsburgh, 1998), p. 19.

- <sup>23</sup>L. Graham, T. Ritzdorf, D. Clarke, and R. Thakur, Semicond. Fabtech 11, 270 (1999).

- <sup>24</sup>S. L. Lagrange, S. H. Brongersma, M. Judelewicz, A. Saerens, I. Vervoort, E. Richard, R. Palmans, and K. Maex, Microelectron. Eng. **50**, 449 (2000).

- <sup>25</sup>S. H. Brongersma, E. Richard, I. Vervoort, H. Bender, W. Vandervorst, D. Lagrange, G. Beyer, and K. Maex, J. Appl. Phys. 86, 3642 (1999).

- <sup>26</sup>S. Riedel, J. Röber, S. E. Shulz, and T. Gessner, Microelectron. Eng. 37–38, 151 (1997).