**Dublin City University**

School of Physical Sciences

# Fabrication and characterisation of copper diffusion barrier layers for future interconnect applications

Conor Byrne B.Sc.

Doctor of Philosophy

June 2015

Supervised by Professor Greg Hughes

**Declaration**

I hereby certify that this material, which I now submit for assessment on the programme

of study leading to the award of doctor of philosophy is entirely my own work, that I have

exercised reasonable care to ensure that the work is original, and does not to the best of

my knowledge breach any law of copyright, and has not been taken from the work of

others save and to the extent that such work has been cited and acknowledged within the

text of my work.

Signed: \_\_\_\_\_(Candidate)

ID No.: 58363145

Date: \_\_\_\_\_

i

#### **Dedications and Acknowledgements**

Firstly I would like to thank my supervisor Greg Hughes, for his support, insight and supervision, without which this project could not have been undertaken, let alone completed. I could not have asked for a better supervisor.

A big thanks to the Surface and Interfaces Research Group (SIRG) in DCU, Justin, Anthony, Paddy, Lee, Rob, Anita, Venkat, Conor, Kumar, Tom and Tony Cafolla, you lot really put the "fun" in fundamental research (some of you put the mental in too!) and to everyone else involved.

I would like to thank all the staff in DCU that have supported me throughout this study, Lisa Peyton, Pat Wogan, Des Lavelle, to name but a few (I wish I could mention everyone by name).

A massive thanks to my girlfriend Xaz, for putting up with me over the past seven years.

A big thanks to all my friends, Ross, Gar, Jim "sure don't worry about that" Shannon, Louis and Michael.

All the people in various other research groups and organizations connected to DCU, Ross (Bell Labs), Rajani, Jithin Stephen (DCU Eng), Barry (NPL), Paul, Karim, Scott, Michael and Alan (Tyndall).

I would also like to thank the Irish Reseach Council (IRC) and Intel Ireland for funding my research and allowing me to undertake this project.

I would also like to thank John Plombon (Intel Components Research Group) and Roger Nagle (Intel resident researcher, Tyndall) for their continued support of the barrier layer project.

Finally I would like to thank my family, my dad and my mam for allowing me to go as far with my education as I liked and for supporting me over the past 25 years. A big thanks to my two brothers Ciaran and Kevin for always having something insightful to say . . . . . just not always about anything particularly insightful.

### Publications arising from this work

Chemical and electrical characterisation of the segregation of Al from a CuAl alloy (90%:10% wt) with thermal anneal.

C. Byrne, A. Brady, L. Walsh, A.P. McCoy, J. Bogan and G. Hughes Thin Solid Films (under review)

Cu diffusion barrier effectiveness of a CuAl alloy (90%:10% wt) for interconnect applications

C. Byrne, R. Lundy, B. Brennan, A.P. McCoy, J. Bogan and G. Hughes (Complete, awaiting submission)

In-situ XPS chemical analysis of MnSiO<sub>3</sub> copper diffusion barrier layer formation and simultaneous MOS fabrication

C. Byrne, B. Brennan, J. Bogan, G. Hughes and A.P. McCoy ACS Applied Materials & Interfaces (under review)

Photoemission study of the identification of Mn silicate barrier formation on carbon containing low-k dielectrics

J. Bogan, A.P. McCoy, R. O'Connor, P. Casey, C. Byrne and G. Hughes Microelectronic Engineering 130, (2014) 46-51

# The impact of porosity on the formation of manganese based copper diffusion barrier layers on low-k dielectric materials

A.P. McCoy, J. Bogan, L. Walsh, C. Byrne, R. O'Connor, G. Hughes and J. Woicik Journal of Applied Physics (D), (accepted and awaiting publication)

### **Conference Proceedings**

#### Spin on porous low-k carbon doped oxides for future interconnect technologies

C. Byrne, R. Lundy, S. Daniels and G. Hughes

Intel Ireland Research Conference (IIRC) (2013), Clontarf Castle, Dublin  $21^{st}-22^{nd}$ November 2013

# Aluminium based self-forming copper diffusion barriers for future interconnect technologies

C. Byrne and G. Hughes

Oral presentation, Intel Ireland Research Conference (IIRC) (2014), The Science Gallery (Trinity College Dublin), 18<sup>th</sup> November 2014.

#### Characterisation of a CuAl alloy for future interconnect technologies

C. Byrne, A.P. McCoy, J. Bogan, A. Brady and G. Hughes

International Interconnect Technology Conference (IITC) and Materials for Advanced Metallization Conference (MAM), Grenoble (2015)

# Contents

| 1      | Int | Introduction |                                  |     |  |  |

|--------|-----|--------------|----------------------------------|-----|--|--|

|        | 1.1 | Bac          | ekground                         | 1   |  |  |

| 1.2 RG |     |              | time delay                       | 3   |  |  |

|        | 1.3 | Cop          | oper as an interconnect material | 6   |  |  |

|        | 1.3 | 3.1          | Ta/TaN Cu diffusion barrier      | 7   |  |  |

|        | 1.3 | 3.2          | Electromigration of Cu           | 8   |  |  |

|        | 1.4 | Lov          | v-k materials                    | 9   |  |  |

|        | 1.5 | Self         | f-forming Cu diffusion barrier   | .13 |  |  |

|        | 1.6 | The          | esis investigation               | .16 |  |  |

|        | 1.7 | Ref          | Perences                         | .19 |  |  |

| 2      | Ex  | perin        | nental Techniques                | .23 |  |  |

|        | 2.1 | Intr         | oduction                         | .23 |  |  |

|        | 2.2 | X-r          | ay photoelectron spectroscopy    | .24 |  |  |

|        | 2.2 | 2.1          | Basic Principles                 | .24 |  |  |

|        | 2.2 | 2.2          | Sampling Depth of XPS            | .28 |  |  |

|        | 2.2 | 2.3          | Spectral Features                | .33 |  |  |

|        | 2.2 | 2.4          | Additional Spectral Features     | .40 |  |  |

|        | 2.2 | 2.5          | Angularly Resolved XPS           | .42 |  |  |

|        | 23  | Ele          | ctrical Measurements             | 45  |  |  |

|   | 2.3                                | .1  | The MOS structure                            | 45 |

|---|------------------------------------|-----|----------------------------------------------|----|

|   | 2.3                                | .2  | Capacitance-voltage sweep                    | 47 |

|   | 2.3                                | .3  | The Ideal MOS Device                         | 53 |

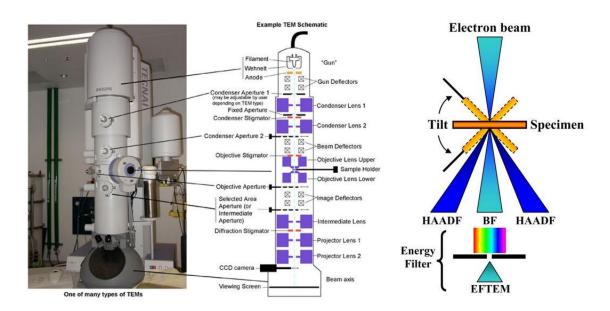

|   | 2.4                                | Tra | ansmission electron microscopy               | 59 |

|   | 2.4                                | .1  | Energy Dispersive X-ray Spectroscopy         | 62 |

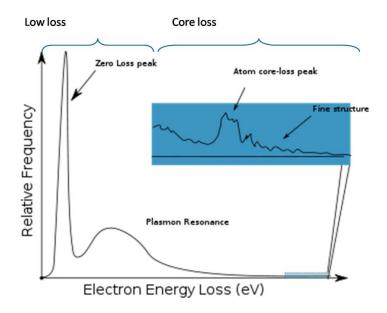

|   | 2.4                                | .2  | Electron Energy Loss Spectroscopy            | 63 |

|   | 2.5                                | Se  | condary Ion Mass Spectroscopy                | 65 |

|   | 2.6                                | X-: | ray Absorption Spectroscopy                  | 67 |

|   | 2.7                                | Re  | ferences                                     | 69 |

| 3 | 3 Experimental systems and methods |     |                                              | 72 |

|   | 3.1                                | Int | roduction                                    | 72 |

|   | 3.2 Ult                            |     | tra-high vacuum systems                      | 72 |

|   | 3.3 XP                             |     | PS                                           | 74 |

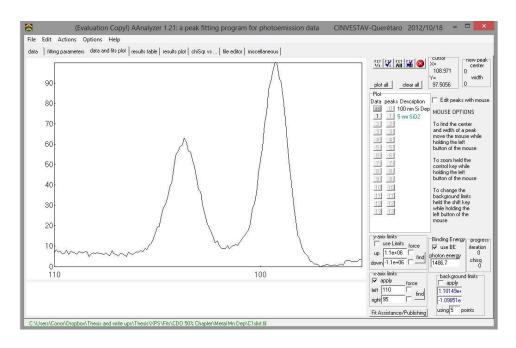

|   | 3.3                                | .1  | XPS peak fitting                             | 75 |

|   | 3.3                                | .2  | XPS layer thickness calculation              | 79 |

|   | 3.3                                | .3  | XPS elemental composition                    | 81 |

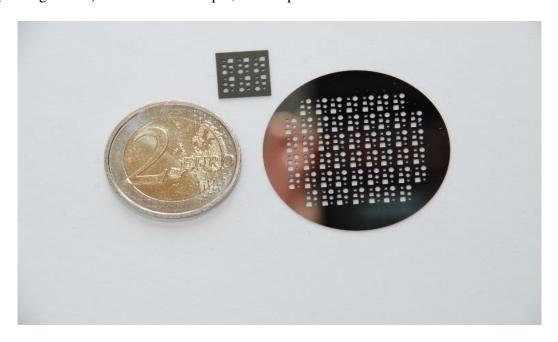

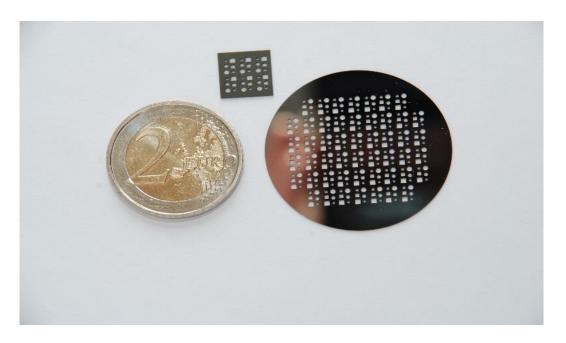

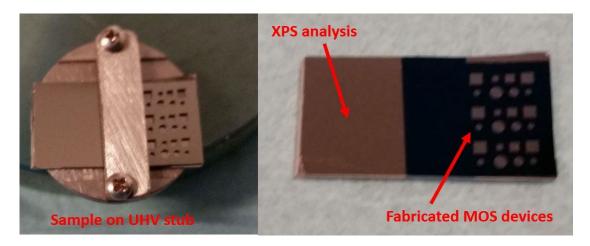

|   | 3.4                                | Me  | etal Oxide Semiconductor Fabrication         | 83 |

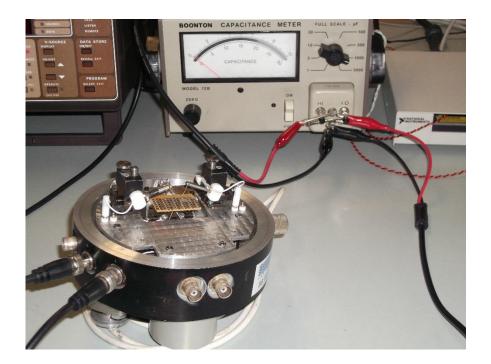

|   | 3.5                                | Ele | ectrical testing of MOS devices              | 86 |

|   | 3.5                                | .1  | Probe station and characterisation equipment | 86 |

|   | 3.5                                | .2  | Thermal stressing of MOS devices             | 87 |

|   | 3.5                                | .3  | Bias thermal stressing of MOS devices        | 88 |

|    | 3.6     | References                                                                 | 9  |

|----|---------|----------------------------------------------------------------------------|----|

| 4  | In      | situ parallel fabrication and interface characterisation of metal oxid     | le |

| se | emicon  | ductor barrier layer test structures9                                      | 1  |

|    | 4.1     | Introduction9                                                              | 1  |

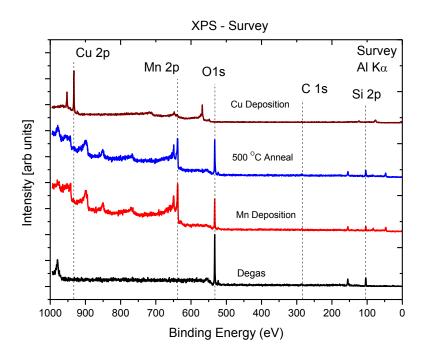

|    | 4.2     | Experimental details9                                                      | 3  |

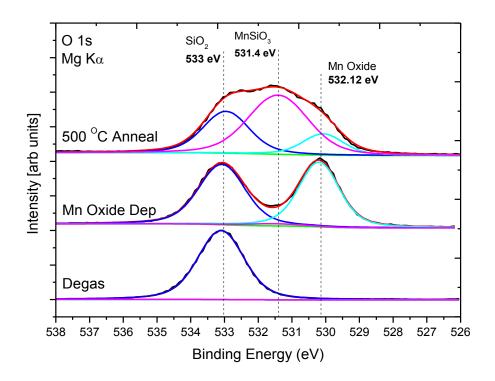

|    | 4.3     | Pure Cu & MnSiO <sub>3</sub> barrier MOS fabrication                       | 6  |

|    | 4.4     | Adhesion promotion of MnSiO <sub>3</sub> barrier9                          | 9  |

|    | 4.5     | Electrical characterisation                                                | 1  |

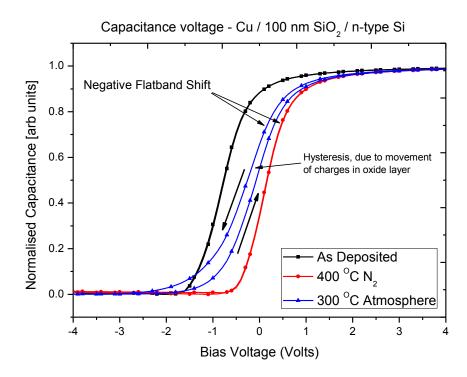

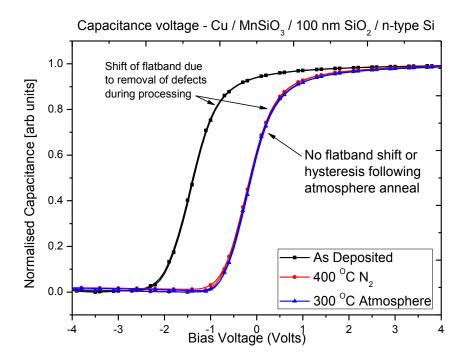

|    | 4.5     | 1 Capacitance voltage10                                                    | 2  |

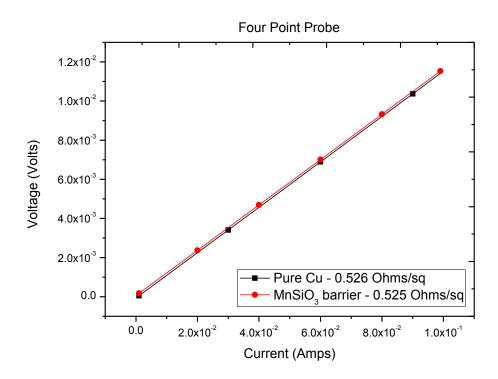

|    | 4.5     | 2 Four point probe                                                         | 4  |

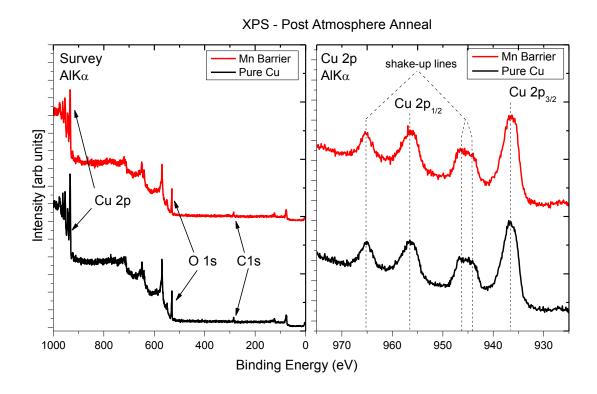

|    | 4.6     | XPS analysis post atmosphere anneal                                        | 5  |

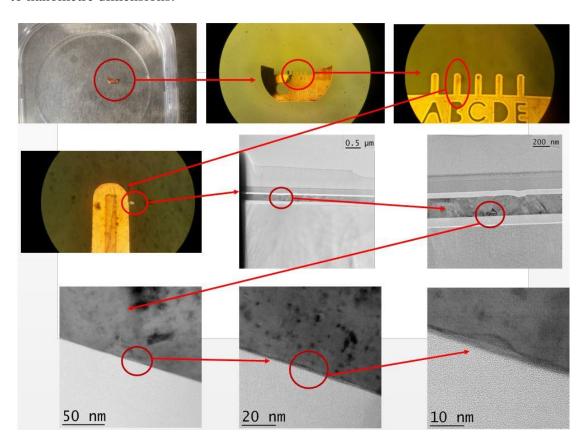

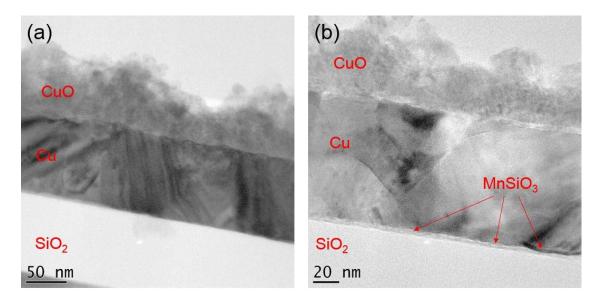

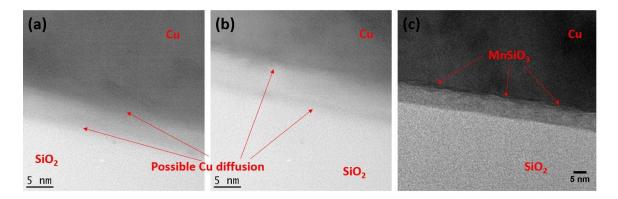

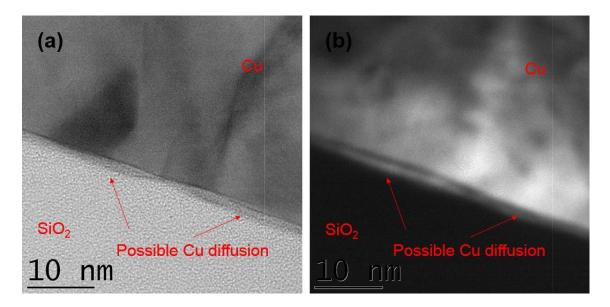

|    | 4.7     | Transmission electron microscopy                                           | 7  |

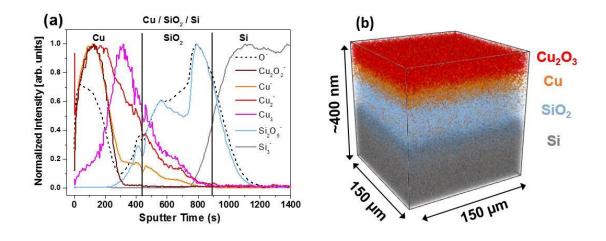

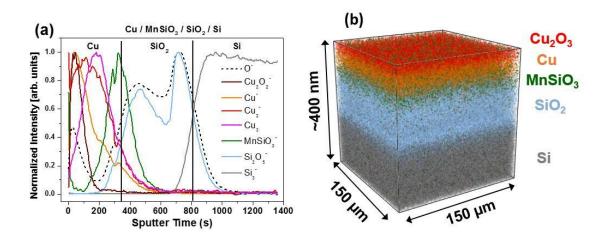

|    | 4.8     | Secondary ion mass spectroscopy                                            | 9  |

|    | 4.9     | Conclusions                                                                | 1  |

|    | 4.10    | References11                                                               | 3  |

| 5  | Ma      | nganese silicate barrier formation on different porosity carbon doped oxid | le |

| di | electri | cs11                                                                       | 7  |

|    | 5.1     | Introduction                                                               | 7  |

|    | 5.2     | Experimental details                                                       | 9  |

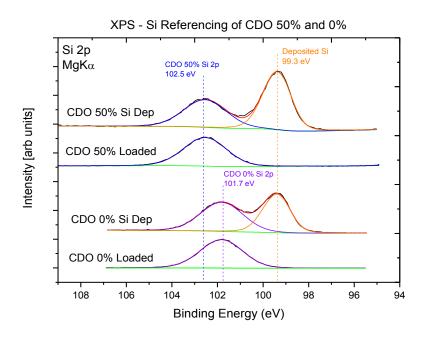

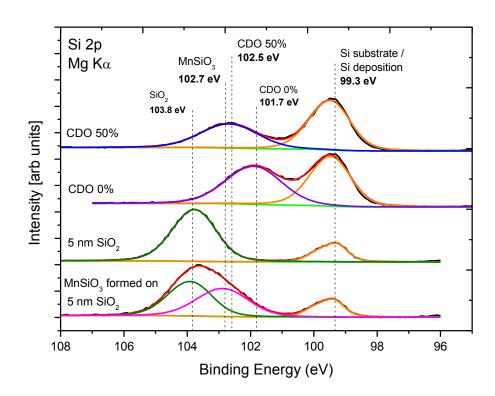

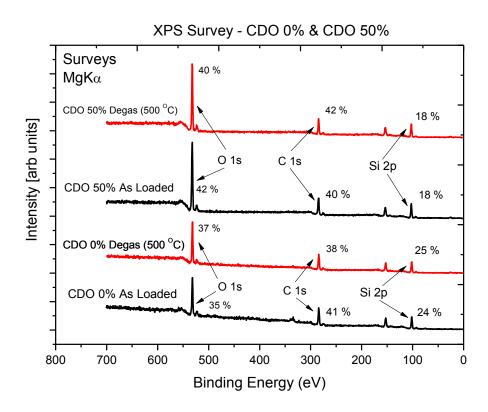

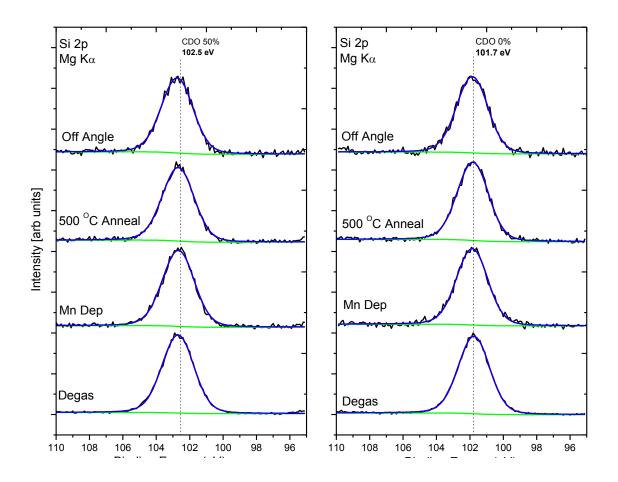

|    | 5.3     | XPS binding energy referencing of 50% and 0% porous CDO                    | 0  |

|    | 5.3     | Deposited Si as an XPS binding energy referencing for porous CD0           | 0  |

|    | dia     | lectrics 12                                                                | •  |

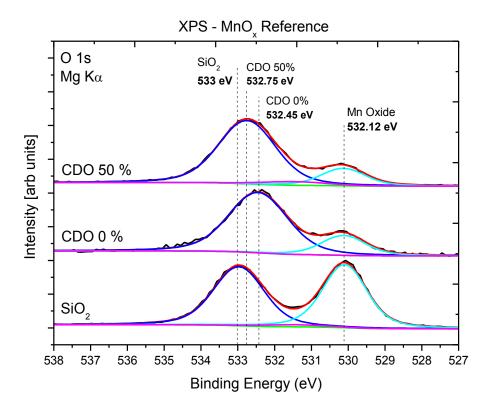

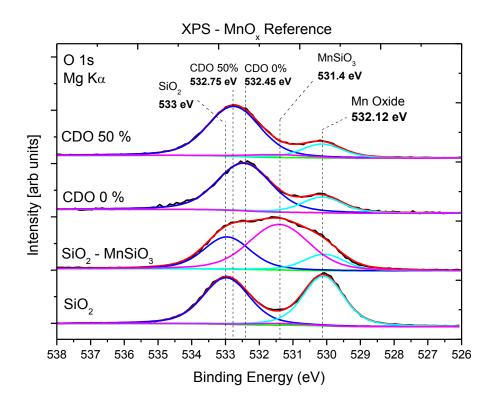

|     | 5.3 | .2 Deposited Mn oxide as a XPS binding energy reference for 0 % a      | nd 50% |  |

|-----|-----|------------------------------------------------------------------------|--------|--|

|     | por | rous CDO                                                               | 123    |  |

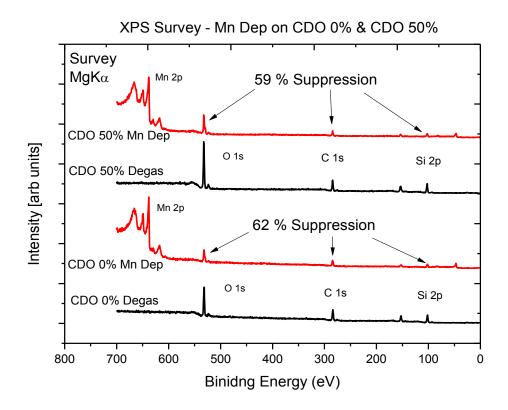

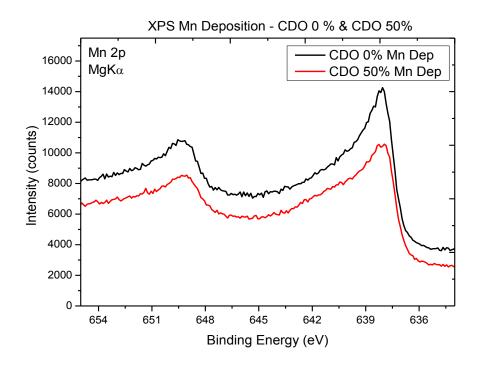

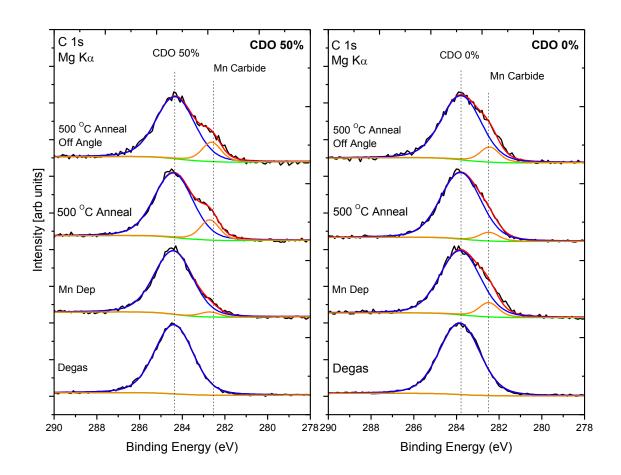

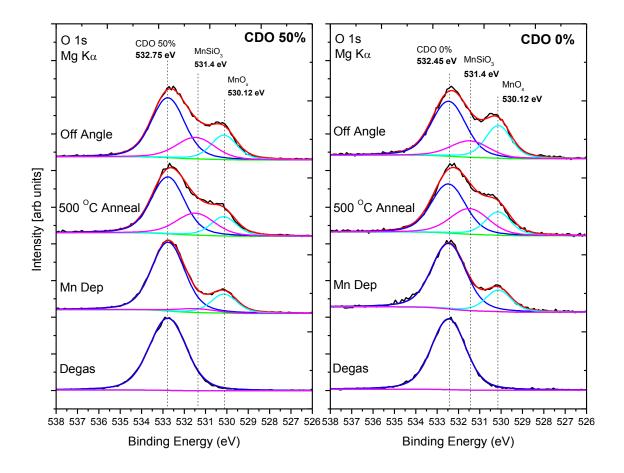

|     | 5.4 | Mn deposition for barrier formation on 0% and 50% porous CDO           | 126    |  |

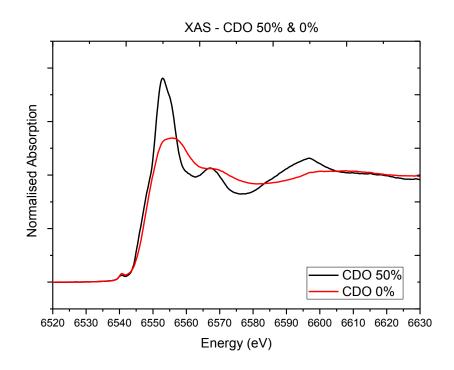

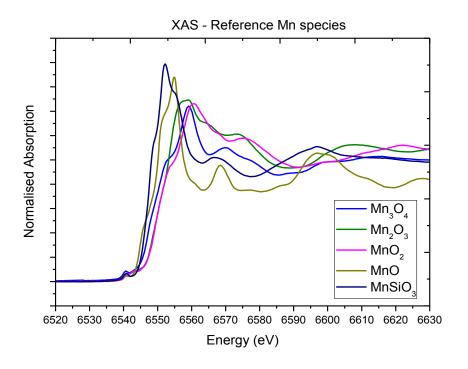

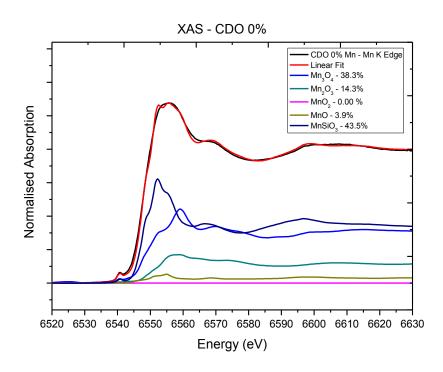

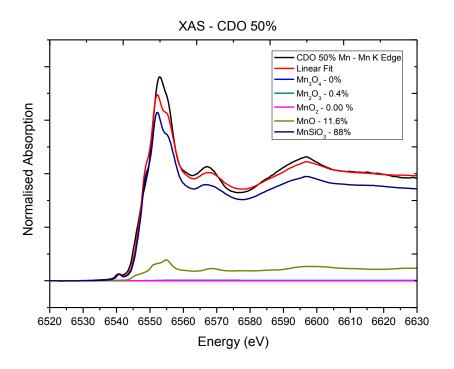

|     | 5.5 | XAS of CDO 0% & 50%                                                    | 135    |  |

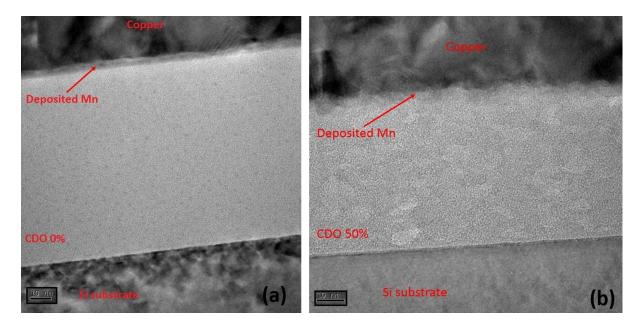

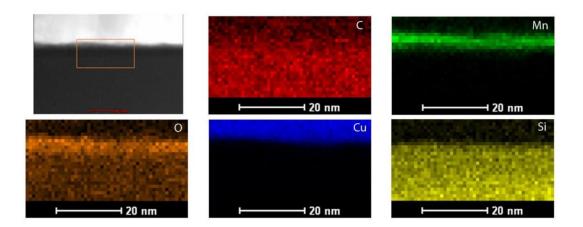

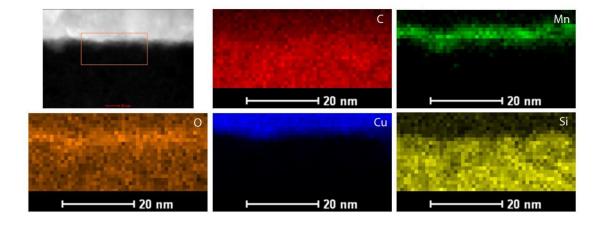

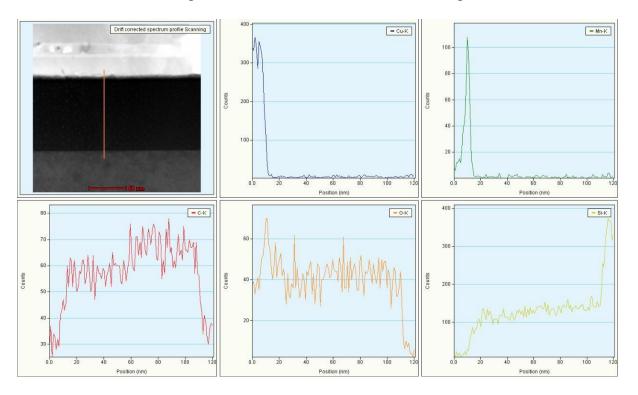

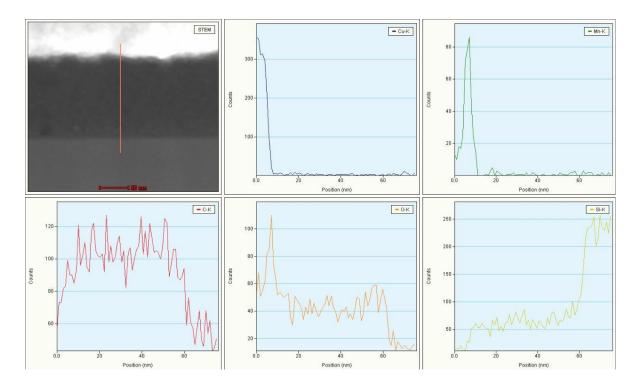

|     | 5.6 | TEM of CDO 0% & 50%                                                    | 140    |  |

|     | 5.7 | Chapter conclusions                                                    | 145    |  |

|     | 5.8 | References                                                             | 147    |  |

| 5   | Cu  | Al (90:10 % wt) alloy for use in BEOL IC interconnect technologies     | 150    |  |

|     | 6.1 | Introduction                                                           | 150    |  |

|     | 6.2 | Experimental details                                                   | 151    |  |

|     | 6.3 | XPS referencing of Cu, Cu oxide, Al & Al oxide                         |        |  |

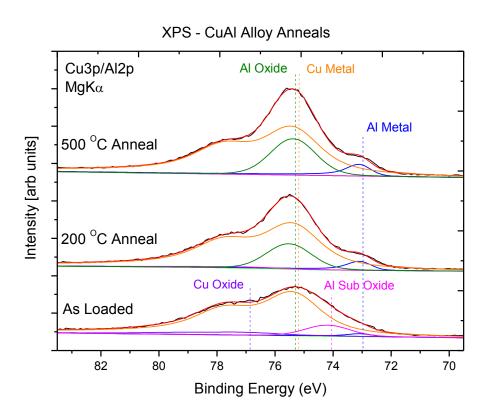

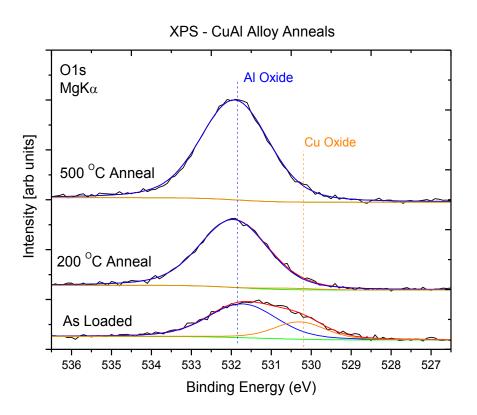

|     | 6.4 | In-situ annealing of CuAl alloy                                        |        |  |

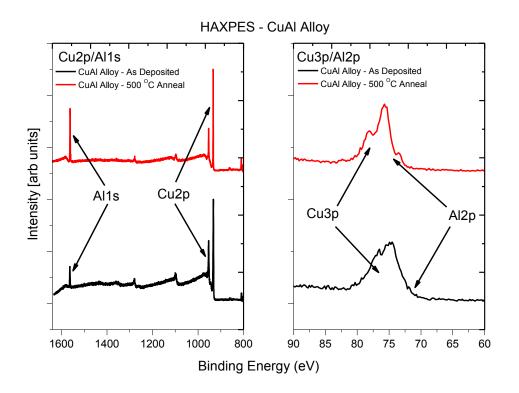

| 6.4 |     | .1 HAXPES of CuAl alloy                                                | 159    |  |

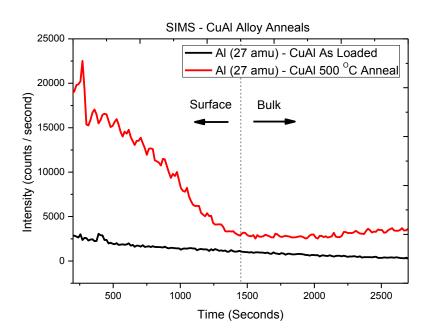

|     | 6.4 | .2 Secondary ion mass spectroscopy                                     | 160    |  |

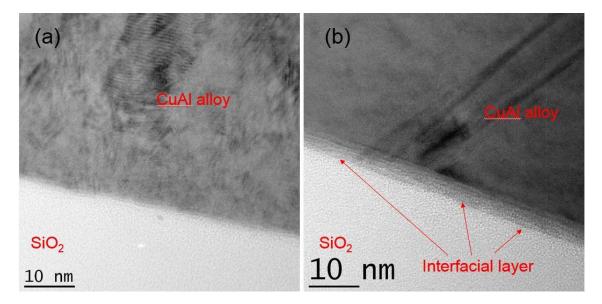

|     | 6.5 | Barrier formation of CuAl / 3 nm SiO <sub>2</sub>                      |        |  |

| •   |     | Electrical characterisation of CuAl alloy                              | 165    |  |

|     |     | Four point probe measurements                                          | 165    |  |

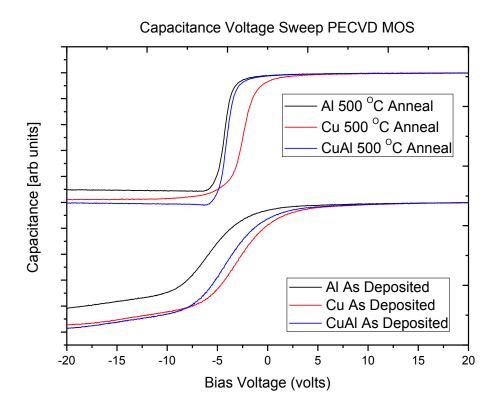

|     | 6.6 | Capacitance voltage measurements                                       | 167    |  |

|     | 6.7 | Transmission electron microscopy                                       | 169    |  |

|     | 6.8 | Conclusions                                                            | 173    |  |

|     | 6.9 | References                                                             | 175    |  |

| 7   | Cu  | Al alloy barrier layer properties for future Interconnect applications | 179    |  |

|                      | 7.1 | Intr   | oduction                                                                    | 179    |

|----------------------|-----|--------|-----------------------------------------------------------------------------|--------|

|                      | 7.2 | Exp    | perimental details                                                          | 180    |

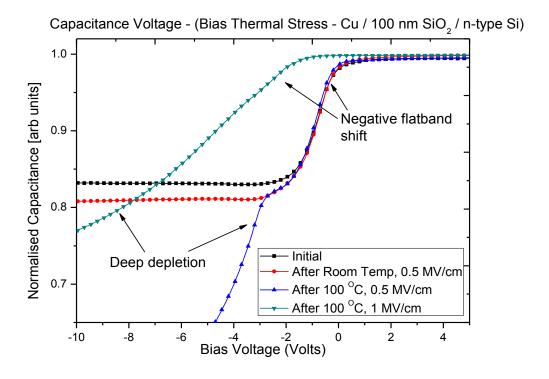

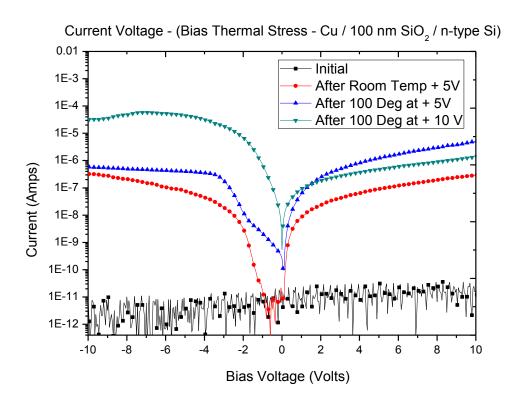

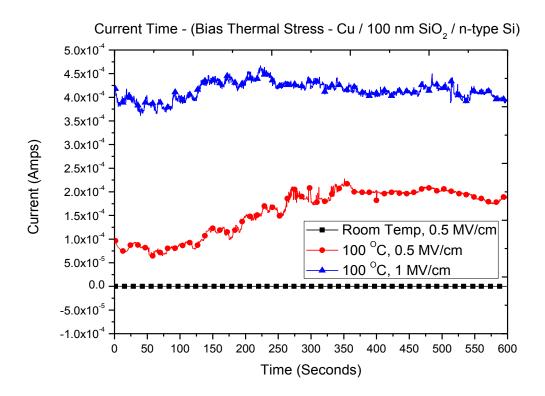

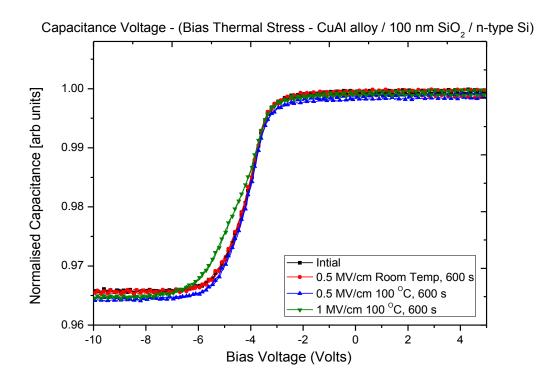

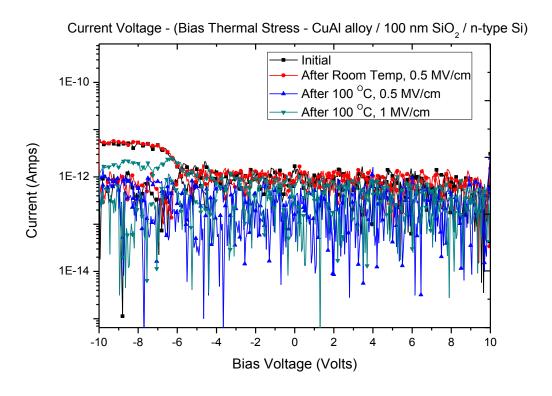

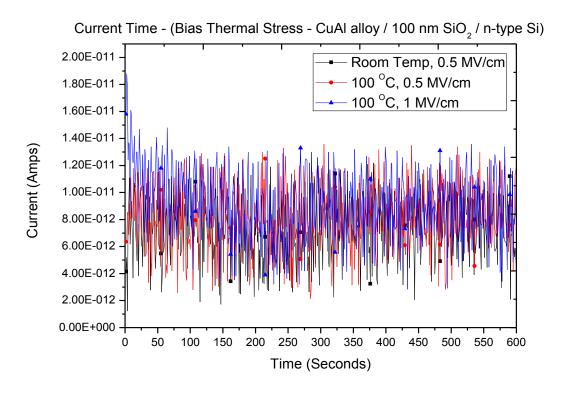

|                      | 7.3 | Bia    | s Thermal Stress of Cu & CuAl alloy MOS devices                             | 180    |

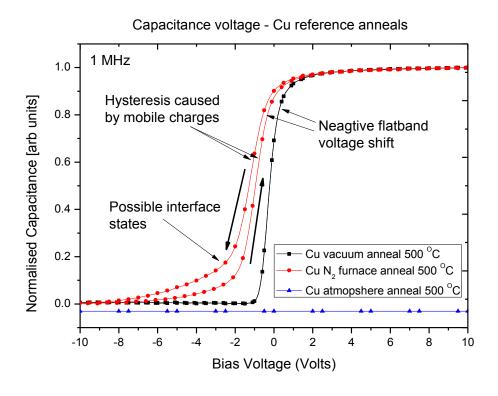

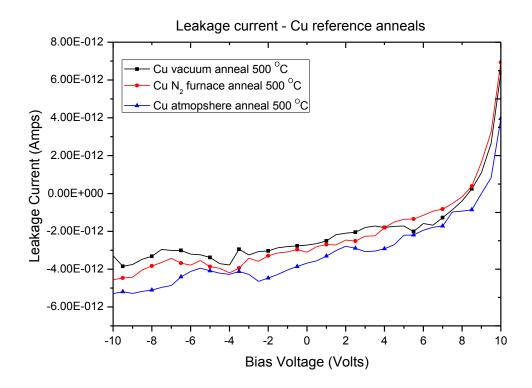

|                      | 7.3 | 3.1    | BTS of Cu reference MOS                                                     | 182    |

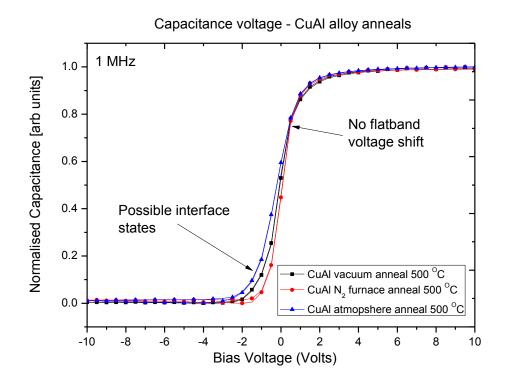

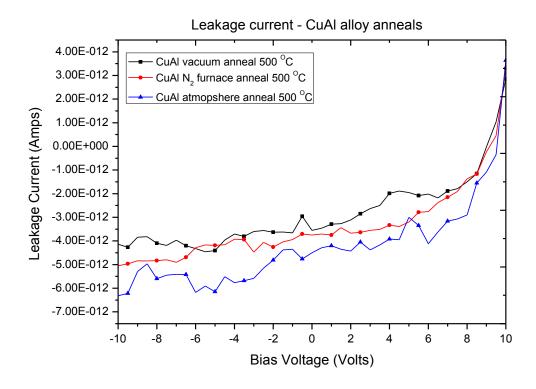

|                      | 7.3 | 3.2    | BTS of CuAl alloy MOS                                                       | 185    |

|                      | 7.4 | The    | ermal stressing of Cu and CuAl alloy MOS                                    | 188    |

|                      | 7.4 | 1.1    | Pure Cu reference MOS thermal stress                                        | 188    |

|                      | 7.4 | 1.2    | CuAl alloy MOS thermal stress                                               | 191    |

|                      | 7.4 | 1.3    | Low frequency CV analysis of thermal stress                                 | 193    |

|                      | 7.4 | 1.4    | Flatband voltage shift of pure Cu MOS following thermal stress              | 194    |

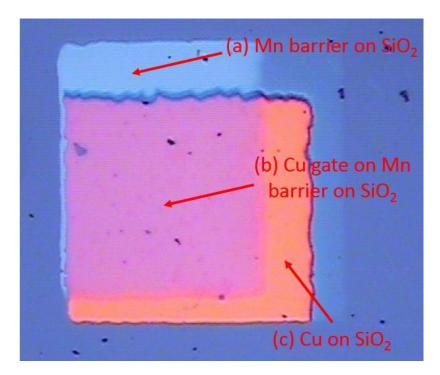

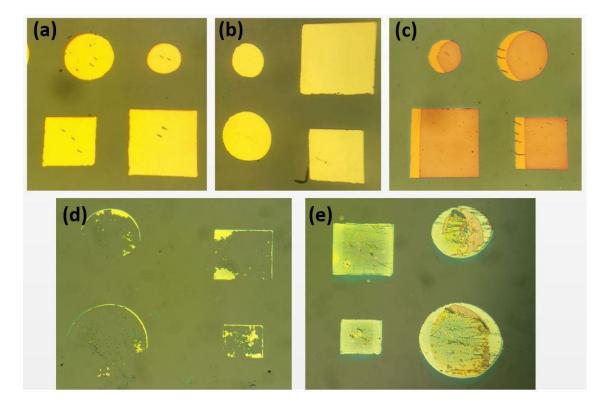

|                      | 7.4 | 1.5    | Imaging of Cu and CuAl MOS throughout thermal stressing                     | 197    |

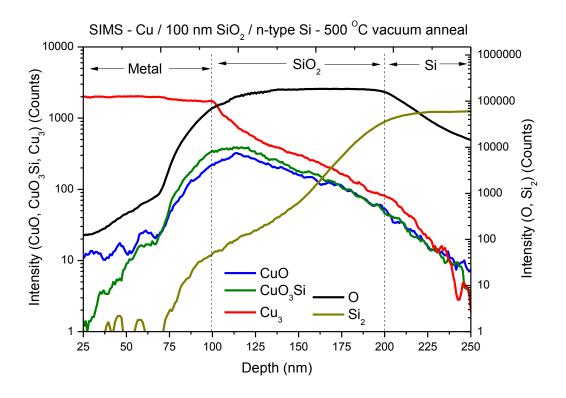

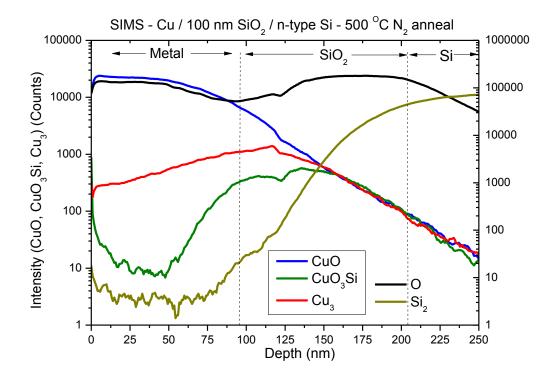

|                      | 7.5 | Sec    | condary Ion Mass Spectroscopy                                               | 203    |

|                      | 7.6 | Cor    | nclusions                                                                   | 207    |

|                      | 7.7 | Ref    | ferences                                                                    | 209    |

| 8.1 Concl<br>8.1.1 M |     | nclus  | sions and future work                                                       | 213    |

|                      |     | Coı    | nclusions                                                                   | 213    |

|                      |     | 1.1    | MnSiO <sub>3</sub> as a Cu diffusion barrier                                | 213    |

|                      |     | 1.2    | MnSiO <sub>3</sub> formation on 0% & 50% porous industrially relevant diele | ectric |

|                      | ma  | iteria | ls                                                                          | 214    |

|                      | 8.1 | 1.3    | CuAl (90:10 % wt) alloy for use in BEOL IC strategies                       | 214    |

|                      | 8.1 | 1.4    | Barrier layer properties of a CuAl (90:10 % wt) alloy                       | 215    |

|                      | 8.2 | Fut    | ure work                                                                    | 218    |

| 8.3 | References | 22 | 2( |  |

|-----|------------|----|----|--|

|     |            |    |    |  |

# Fabrication and characterisation of copper diffusion barrier layers for future interconnect applications.

#### **Conor Byrne**

#### **Abstract**

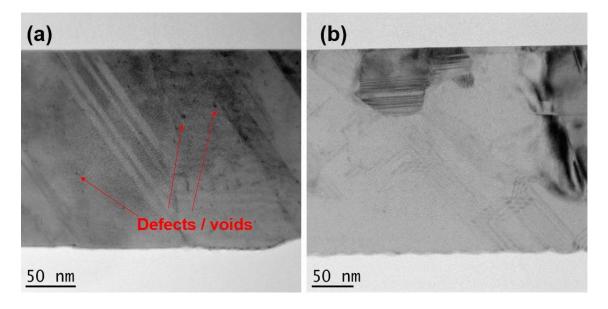

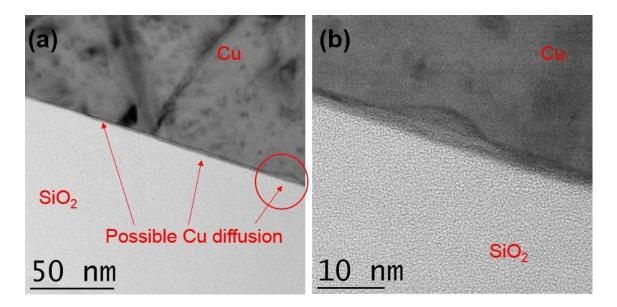

The focus of this thesis is the fabrication and characterisation of ultra-thin self-forming Cu diffusion barrier layers for future interconnect technologies. These barrier layers form by the chemical interaction of an expelled metal from a copper alloy with the surface of a dielectric material to form a stable chemical species suitable for integration into future interconnect fabrication strategies. Studies of both manganese and aluminium as the alloying elements were undertaken and the characterisation techniques included x-ray photoelectron spectroscopy (XPS), transmission electron microscopy (TEM), x-ray absorption spectroscopy (XAS) and secondary ion mass spectroscopy (SIMS). Electrical characterisation measurements used to establish the effectiveness of the barrier layers at preventing copper diffusion were performed on fabricated metal-oxide-semiconductor (MOS) structures. A novel approach involving interface chemistry studies and MOS device fabrication on the same dielectric substrate was successfully demonstrated. Barrier formation on a range of prototype low-k dielectric materials with different carbon concentrations and porosities were undertaken and surface chemical modifications prior to barrier layer formation were also investigated. The results show that both Mn and Al are effective at preventing copper diffusion into SiO<sub>2</sub>, but the inherent porous structure of low-k dielectrics present significant challenges to barrier layer formation, particularly at the dimensional range required for future technology nodes.

#### 1 Introduction

#### 1.1 Background

In 1965 Gordon Moore, co-founder of Intel, made one of the most famous technological observations in semiconductor history [1]. Moore noted that since production of the first integrated circuit (IC) chips in 1958, every two years the number of on-chip components had doubled and predicted that this trend would continue to advance the emerging semiconductor device industry.

This prediction has led to a manufacturing template which has been used to relentlessly drive the industry towards smaller and smaller feature sizes, thereby creating faster and cheaper IC chips for device integration. This growth in technological advancement coupled with lower cost and decreased power consumption has allowed mankind to explore, communicate, discover and invent at an ever increasing rate. From the first Moon landings in 1969, to the modern communication network of satellites and high speed server farms, the impact of increasingly complex computing power has been wide ranging. With mobile technology, anyone at virtually any location on the planet using a device no bigger than the palm of a human hand can access internet technology. Thus it can be seen that Moore's law has changed the way we live our lives in the developed world making it quite possibly one of the most dramatic observations made by a human in the history of mankind.

The current world leader in IC production is the Intel Corporation which adopts Moore's law in the famous "Tick-Tock" cycle [2]. This cycle begins with a "die-shrink" (tick) of

a previous generation of IC chip, thereby reducing feature sizes of on-chip components. The second part of the cycle is the "tock" stage where the on-chip feature size remains constant, but a change in on-chip architecture is made, thereby squeezing as much performance from the previous "tick" stage as possible, before the next die-shrink (tick) stage. From the first commercial microprocessor IC chip produced, the Intel 4004, with feature sizes of 10,000 nm to the currently developed Intel Skylake Core i7 (the "tock" to the released 14 nm Broadwell die-shrink) microprocessor with feature sizes of 14 nm, Intel have dominated the market. This downward trend in feature sizes has allowed more and more devices to be fabricated on a single IC chip, from the Intel 4004 with a transistor count of 2,300 to the currently available Intel 10 core Xeon Haswell-EP with a record breaking 5.5 billion transistors, showing that the modern IC transistor count is almost 2.4 million times that of the initial IC chip produced (give or take a few million transistors). To put this in perspective, the current Intel 10 core Xeon Haswell-EP processor is roughly the size of the nail on a small finger, but within that area there is a transistor for every man, woman and child on the face of the Earth.

This dramatic increase in transistor count, with parallel reduction in feature sizes has been possible only with intensive research in the areas of materials growth, deposition, photolithography, patterning, etching and engineering [3]. Thus the semiconductor field has been one of the most intensely researched scientific disciplines in the history of applied physics. Issues encountered during die-shrinking require intense research, traditionally related to the famously small transistors. However in recent years, research has begun to be increasingly focus on the interconnects, which essentially wire-up the transistors in a well-defined way. This is because performance bottlenecks are emerging due to the increasing complexity of interconnect fabrication.

The focus of the research work carried out in this thesis is on the back end of line (BEOL) where the interconnect structures are located. The continuous reduction in dimensions demands the fabrication of smaller and smaller interconnect structures and requires an intensive research effort if the projected performance improvements are to be realised [3].

# 1.2 RC time delay

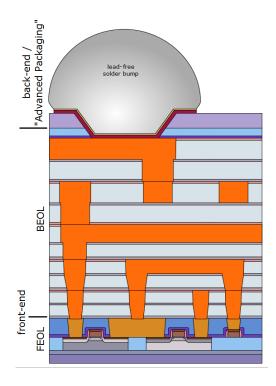

As stated previously one of the current challenges to improve device performance is found in the complexity of the BEOL interconnect stage of the IC chip as schematically shown in Figure 1.1. BEOL processes are concerned with the wiring of the transistors, which are fabricated in the front end of line (FEOL) process, to relay the digital signals in the IC chip. As seen in Figure 1.1, the structure of interconnects consist of a metal conduction line primarily copper, surrounded by an insulating material known as the inter-layer dielectric (ILD).

Figure 1.1: Side on schematic of a modern IC chip, displaying both FOEL and BEOL segments [4].

In order to demonstrate the issues with BEOL interconnects, an explanation of resistive-capacitive (RC) time delay must be presented. The switching frequency of an interconnect structure is determined by the RC time delay of the structure, given by:

$$\tau = R.C$$

Equation 1.1: RC time delay equation.

where R is the resistance of the metal wire and C is the parasitic capacitance between parallel metal wiring structures, separated by the ILD material. The resistance of the interconnect wire can in turn be given as:

$$R = \frac{\rho L}{A}$$

Equation 1.2: Resistance of an interconnect wire.

where R is the resistance of the interconnect wire, L is the length of the wire, A is the cross-sectional area of the interconnect wire and  $\rho$  is the intrinsic resistivity of the conducting material used. Thus it can be seen via Equation 1.2 that as the cross-sectional area (A) decreases due to die-shrinking, the overall resistance of the interconnect structure increases, in turn increasing the delay in switching speeds as given in Equation 1.1.

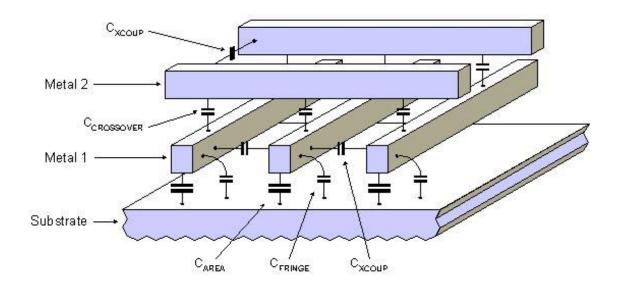

In addition to an increase in RC delay due to an increase in resistance, the delay time can increase due to an increase in parasitic capacitance between interconnect lines following die-shrinkage. As seen in Figure 1.2, two adjacent metal lines can be modelled as a parallel plate capacitor structure.

Figure 1.2: 3D representation of the parasitic capacitance between adjacent metal interconnect structures [5].

The capacitance between two interconnect lines, with an ILD material between them can be expressed via the parallel plate capacitor equation, given as:

$$C = \frac{\varepsilon A}{d}$$

Equation 1.3: Parallel plate capacitor equation.

where C is the capacitance between two metal plates of common cross sectional area A, separated by a distance d, with a material dielectric constant of  $\epsilon$ . Therefore as interconnect lines are fabricated closer together due to die-shrinking, the parasitic capacitance between the lines increases, in turn increasing the RC time delay of the interconnect structure overall.

Thus it can be seen that the process of die-shrinking negatively impacts on the RC time delay of the interconnect lines, causing a decrease in switching speeds of the device overall and potentially resulting in an increase in power consumption due to an increase in the resistance of the interconnect lines. As can be seen via Equation 1.2 and Equation 1.3, the only controllable factors available to combat the increase in RC time delay, are to lower the intrinsic resistivity of the metal in the conducting line and/or to decrease the electrical permittivity factor of the ILD material. Both of these approaches will be discussed below.

# 1.3 Copper as an interconnect material

Traditionally, aluminium (Al) was used as the interconnect metal of choice due to its low resistivity (28.2 x  $10^{-9} \Omega$ -m) and ease of deposition, etching and patterning to form interconnect lines. With the relentless shrinking of interconnect structures in accordance with Moore's law, the use of aluminium became too resistive a material to use as the interconnect metal line. Consequently, a change was needed to a lower resistivity material, however given the already low resistivity value of aluminium (28.2 x  $10^{-9} \Omega$ m), few choices were available to integrate as a new metal line, namely gold (24.4 x 10<sup>-9</sup>  $\Omega$ -m), copper (16.8 x  $10^{-9} \Omega$ -m) or silver (15.9 x  $10^{-9} \Omega$ -m) [6]. Due to the expense of using either gold or silver, copper (Cu) became the interconnect metal of choice. With the change to Cu came a number of advantages most notably, a decrease in interconnect resistivity and consequently a decrease in power consumption. In addition there was increased resistance to electromigration failure, compared to aluminium. . However, along with the benefits to the change in Cu also came a number of disadvantages such as the tendency for Cu diffusion into any surrounding ILD materials, poor adhesion of Cu to ILD materials and the less pronounced but still present electromigration issues especially with increased current density as a result of die shrinking [7].

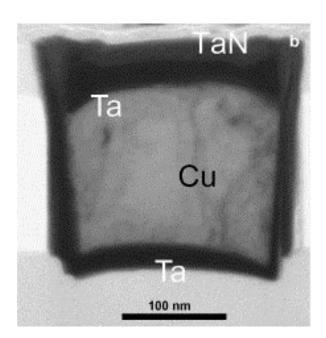

#### 1.3.1 Ta/TaN Cu diffusion barrier

As stated previously, with the change to Cu as the metal interconnect of choice came the issue of Cu diffusing into any surrounding silicon oxide based ILD materials. This issue if left unaddressed would eventually lead to interconnect device degradation and ultimately failure of the interconnect lines due to electrical shorting of the structures. Additionally Cu has been shown to cause deep level traps in Si, indicating that if any Cu were to diffuse into electrically active devices in the FEOL such as transistors, it would cause device failure. Thus the need for a physical barrier layer between the Cu metal line and ILD material became evident. The barrier stack currently in use for containment of Cu in the conducting lines is a dual layer of Ta/TaN. The need for a dual layer is due to the fact that although TaN is a good Cu diffusion barrier, Cu does not adhere well to it, thus an interlayer of Ta is placed between the TaN and Cu materials as seen in the microscopy image in Figure 1.3.

Figure 1.3: Cross sectional scanning electron microscopy (SEM) image of a Cu / Ta / TaN / ILD interconnect structure [5].

As interconnect structures continue to shrink in dimensions in accordance with Moore's law, the current Ta/TaN barrier arrangement has been difficult to correspondingly scale. Therefore, for future scaled structures, it would occupy too much of the volume available in the interconnect line, minimising the volume of Cu thereby causing an increase in interconnect resistance. In addition the physical vapour deposition (PVD) method of sequentially depositing these layers makes it difficult to obtain uniformly deposit barriers on increasingly high aspect ratio structures. Thus a new paradigm of barrier layer is needed to replace the relatively thick current Ta/TaN dual layer. The new barrier layer solution must be ultra-thin (~ 5 nm) in order to maximise volume available for Cu in the conducting line, promote adhesion between the Cu and ILD material and also prevent Cu from diffusing into the surrounding ILD material.

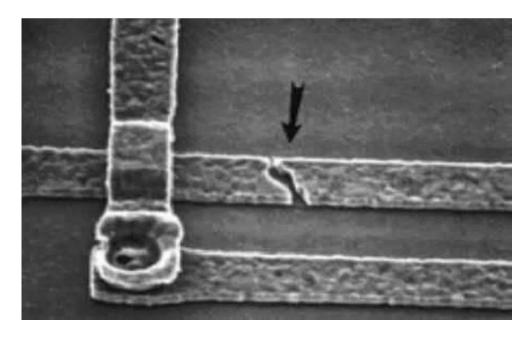

#### 1.3.2 Electromigration of Cu

Electromigration is the phenomenon of conducting material moving or distorting during electrical current transport. This physical phenomenon is problematic for IC interconnect structures due to the fact that it can result in the formation of voids within metal lines. When a metal line such as an interconnect carries an electrical current, an "electron wind" is generated in the metal. This "electron wind" can collide with metal atoms in the conducting lines of the structure (especially at grain boundary sites) and cause them to move or migrate to other regions. This in turn can create voids within the conducting line as can be seen in Figure 1.4 [8]. Aluminium was particularly prone to electromigration failure due to the relative low mass of single Al atoms. With the switch to Cu (higher mass value), electromigration is reduced however it is still problematic due to die shrinking [7] as the increased current density within the conducting lines increases the probability of electromigration. Poor adhesion between the copper and the surrounding

dielectric material can also lead to significant electromigration effects. Therefore the need for a barrier material with strong adhesion between the conducting metal line and ILD becomes increasingly important as line dimensions continue to shrink.

In an effort to minimise electromigration, the Al can be alloyed with Cu in the interconnect line. This process causes the Al to segregate to the grain boundaries in the Cu metal which greatly reduces electromigration problems by minimisation of movement of Cu atoms at the grain boundaries [9].

Figure 1.4: SEM imaging of a Cu interconnect line failure due to electromigration [4].

### 1.4 Low-k materials

Equation 1.1, the RC time delay factor can also be lowered by lowering the parasitic capacitance between the conducting metal lines within an IC chip. The capacitance between two interconnect lines can be modelled by the parallel plate capacitor as seen in Equation 1.3. Therefore, the smaller the distance between the conducting lines, the larger the capacitance. This is problematic in terms of die shrink as the metal lines are located

closer and closer to each other. The only variable that could be changed to lower the capacitance during die shrink is the dielectric constant  $-\varepsilon$ . By lowering the dielectric constant of the ILD, the capacitance overall will be lower and thus the RC time delay will also be reduced. The k-value of a material is defined as the electrical permittivity of the material divided by the electrical permittivity constant of free space, as given in Equation 1.4:

$$\kappa = \frac{\mathcal{E}_{material}}{\mathcal{E}_0}$$

Equation 1.4: k value equation for a dielectric material.

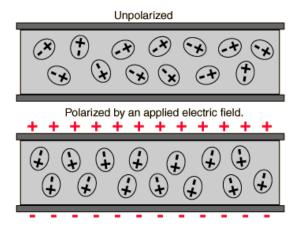

where k is the k-value of the material,  $\mathcal{E}_{material}$  is the electrical permittivity of the material and  $\mathcal{E}_0$  is the electrical permittivity of free space (8.85x10<sup>-12</sup> F/m). When the values for silicon dioxide (SiO<sub>2</sub>) are used, the k-value for SiO<sub>2</sub> is found to be ~ 3.9. This value is used as the bench mark for low-k materials as anything which is defined as low-k must have a lower k-value than 3.9. Dielectric materials such as SiO<sub>2</sub>, when placed in an electric field, can be polarised as schematically illustrated in Figure 1.5. When no electric field is placed across the dielectric, the orientation of the dipoles in the molecules are in a random orientation, with the sum of the fields equating to zero. When an external electric field is applied to the dielectric, the dipoles in the material distort and orientate into a position as shown in the lower half of Figure 1.5. The degree to which these molecules distort and orientate can be equated to the k-value of the material. Thus, if a material has a high k-value, a larger shift in dipole and orientation will be seen in comparison to a material of lower k-value. Due to the fact that a large shift in dipole under an applied electric field will give rise to a large capacitance overall, it can be seen that the

k-value of the material is related to the capacitance of the material i.e. a large k-value will give rise to a larger capacitance than a lower k-value material of similar dimensions. This can be shown when Equation 1.3 and Equation 1.4 are combined to yield Equation 1.5 which shows the dependence of capacitance on k-value.

$$C = \frac{\kappa \varepsilon_0 A}{d}$$

Equation 1.5: Parallel plate capacitance equation with k-value dependence.

Figure 1.5: Electrical polarisation of a dielectric material under applied voltage [10].

Thus, if the capacitance of the material is dependent on the electrical polarisability, by changing the material to a lower k-value, the parasitic capacitance of interconnect lines can be reduced thereby lowering the RC time delay.

One of the methods used in developing low-k materials was to replace some of the high polarisable Si-O bonds in  $SiO_2$  with less polarisable bonds such as silicon-carbon bonds. Thus by introducing carbon into the dielectric material, the k-value and in turn the

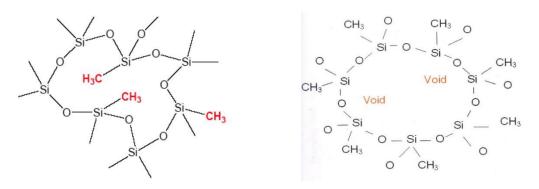

resulting capacitance should be lowered. These materials are usually referred to as CDO (carbon doped oxide) materials. The general schematic structure of these materials can be seen in Figure 1.6. With the addition of lower polarisable carbon bonds, it is possible to reduce the k-value to as low as ~ 2.5 [11]. While SiO<sub>2</sub> was the original ILD of choice, manufacturing has shifted its sights to CDO materials such as Black Diamond <sup>TM</sup>which was developed by Applied Materials (AMAT) and Aurora CDO <sup>TM</sup> which was developed by ASM international.

Figure 1.6: Structure of a CDO dielectric [12].

Figure 1.7: Structure of a CDO dielectric with voids [12].

By definition from Equation 1.4, the lowest k-value that can be achieved is a k-value of 1, which is that of a vacuum, although air has a similar k-value. Therefore by the introduction of voids in the dielectric material the overall k-value of the material will be lowered. This has been achieved using SiO<sub>2</sub> and even CDO materials to further push the k-value downward in an effort to reduce parasitic capacitance [13]. An example of a structural makeup of a CDO material with induced voids is presented in Figure 1.7. As can be seen, the chemical makeup of the dielectric is identical to that of the initial CDO layer in Figure 1.6, however the existence of voids in the material lowers the overall k-value of the dielectric.

In addition to the decrease in k-value and the RC time delay achieved with these materials, a set of challenges must be met. These challenges range from manufacturing difficulties due to the fact that these materials typically have a lower Young's modulus than traditional ILD materials meaning that they can be damaged easily during processing [14]. Further to physical damaging of the dielectric, the chemistry of these new carbon doped oxides means that any materials used in conjunction with them must not react in an undesirable way such as metal carbide formation at any metal-dielectric interface [15]. The introduction of voids to these materials also presents a fast route for any metals, especially Cu, to diffuse quickly through the porous material [16,17].

## 1.5 Self-forming Cu diffusion barrier

As described previously, the current method of preventing the Cu diffusion into the surrounding ILD material is by way of a TaN/Ta barrier. If this barrier could be scaled down while still retaining good Cu diffusion and adhesion properties it would allow more room in the interconnect trench for Cu leading to a decrease in line resistance and an overall decrease in RC time delay. However, the indications are that it is difficult to scale this barrier layer system to the thicknesses required for future interconnects and the fact that it is a physical vapour deposition (PVD) process makes it unsuitable for the high aspect ratio structures increasingly required in BEOL fabrication.

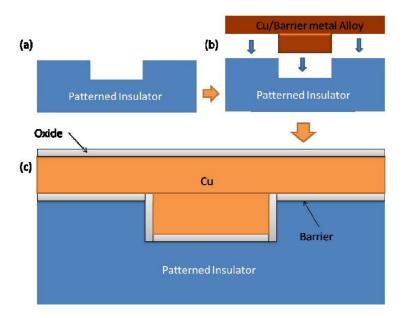

One solution which has been proposed is the use of a self-forming barrier (SFB) [18]. The idea behind this approach of barrier layer formation is to alloy a material such as aluminium or manganese with the Cu during deposition of the interconnect line. The structure is then annealed during which the alloyed material is expelled from the Cu and chemically reacts with the dielectric layer to form a barrier at the metal/ILD interface. Ideally, this reaction should be self-limiting to typically a few nanometers (~3nm) to

ensure the barrier formed is of the required thickness dimension. Any excess of the alloying element will diffuse to the surface of the Cu line during the thermal anneal where it can be removed by further processing steps such as chemical mechanical polishing (CMP). This process is schematically shown in Figure 1.8 where (a) is the patterned ILD material, (b) is the deposition of the Cu alloy and (c) is the subsequent anneal, chemical reaction and formation of the self-forming barrier at the surface of the ILD layer. Two candidate metals which are currently being investigated for use as an alloying element with Cu to form a SFB are manganese and aluminium. The metal manganese (Mn) shows great promise for use as an SFB alloying material due to the fact that it is expelled from Cu when annealed [19]. This means that during the anneal stage, the Mn will be expelled from the Cu before the Cu has time to migrate through the ILD material. The Mn then chemically reacts at the interface to form manganese silicate which has potential to be an excellent barrier material in terms of preventing Cu ion diffusion and has good adhesion properties [18].

Figure 1.8: Self forming barrier process [4].

The second alloy material under investigation for use in the SFB approach is aluminium (Al). This metal has a number of advantages for use in processing, the first being it is a metal which has previously been used in the industry and thus is well understood for manufacturing purposes. The second aspect which makes Al an attractive candidate is the high heat of formation of  $Al_2O_3 \sim -1677.4$  kJ/mol which is significantly higher than that of the stable oxide of silicon,  $SiO_2 \sim -910.4$  kJ/mol [20]. These thermodynamic values indicate that Al should readily react with the ILD to form a chemically stable layer of  $Al_2O_3$  which has the potential to act as an excellent Cu diffusion barrier layer. The third promising aspect of using Al metal is the fact that Al can migrate to the Cu grain boundaries during the anneal stage where it can act to suppress electromigration in the interconnect line [9,21].

### 1.6 Thesis investigation

The experimental work presented in this thesis is on the topic of chemical, structural and electrical performance of self-forming Cu diffusion barriers formed on a variety of dielectric substrates. An introduction has been outlined, describing previous generations of IC material fabrication and design. Issues with future iterations of die-shrinking in relation to materials has been outlined, in particular the need for a Cu diffusion barrier to overcome the problematic issues of (a) Cu diffusion into surrounding ILD material, (b) promotion adhesion between the Cu line and ILD material and (c) be thin enough to allow maximum volume of Cu fill within interconnect lines to minimise resistance. As stated previously, self-forming barriers could be a viable solution to the problems associated with current barrier layer stacks. The work in this thesis follows on from previous chemical and structural studies of copper diffusion barrier layer formation in the Surface and Interface Research Group (SIRG) in DCU [4,22] which paved much of the foundational work of in-situ chemical analysis of MnSiO<sub>3</sub> as a self-forming barrier candidate material on SiO<sub>2</sub> dielectric substrates. Studies of barrier formation on prototype low-k dielectric materials and the development of a capability to fabricate metal-oxidesemiconductor (MOS) test structures for electrical testing of the barrier integrity were undertaken. In addition an alternative self-forming barrier layer candidate metal, aluminium (Al), is explored from both interface chemistry and electrical test device perspectives. The following is a brief outline of the work presented in the experimental results chapters of this thesis:

# <u>Chapter 4</u>: "In situ parallel fabrication and interface characterisation of metal oxide semiconductor barrier layer test structures"

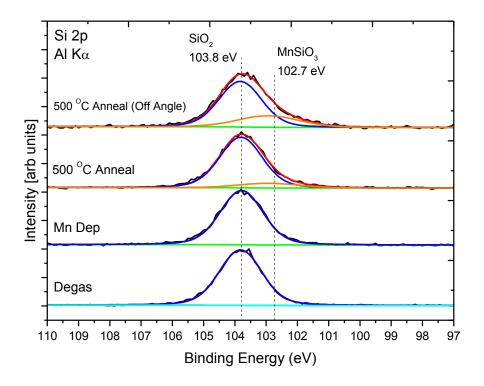

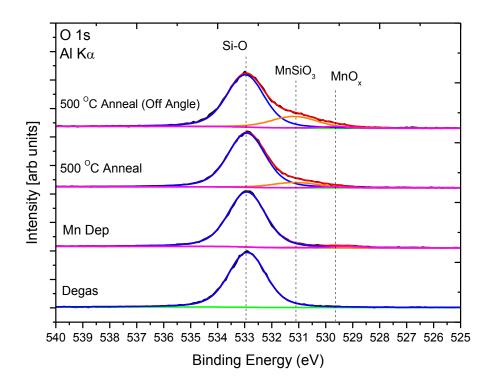

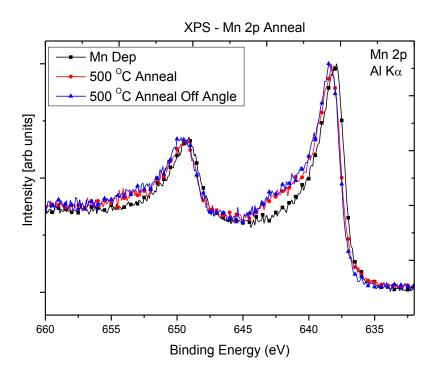

This chapter follows directly on from the initial in-situ interface chemistry study of Mn deposited on SiO<sub>2</sub> dielectric layers to form MnSiO<sub>3</sub> barrier layers undertaken by the SIRG [4,22,23,15,24,25,19,26]. This chapter further expands on the analysis of the barrier formed by utilising a novel approach of in-situ fabrication of MOS structures with and without a MnSiO<sub>3</sub> barrier layer, in an ultra-high vacuum (UHV) system monitored by XPS analysis throughout fabrication process. The highly controlled environment in which the MOS devices were fabricated, allowed direct correlation of the chemistry of barrier formation with the subsequent electrical testing of the fabricated MOS devices.

# <u>Chapter 5</u>: "Manganese silicate barrier formation of different porosity carbon doped oxide dielectrics"

This chapter focuses on the formation of a MnSiO<sub>3</sub> barrier on industrially relevant, high porosity (50% porous) and low porosity (0% porosity) carbon doped oxide (CDO) materials. Both 50% and 0% CDO materials were exposed to identical thin film Mn depositions and anneal treatments, thereby allowing the effect of porosity on barrier layer formation to be observed. In-situ X-ray photoelectron spectroscopy (XPS) and well as X-ray absorption spectroscopy (XAS) and transmission electron microscopy (TEM) were employed to characterise the formation of MnSiO<sub>3</sub> on these technologically relevant dielectric materials.

#### Chapter 6: "CuAl (90:10 %) alloy for use in BEOL IC interconnect technologies"

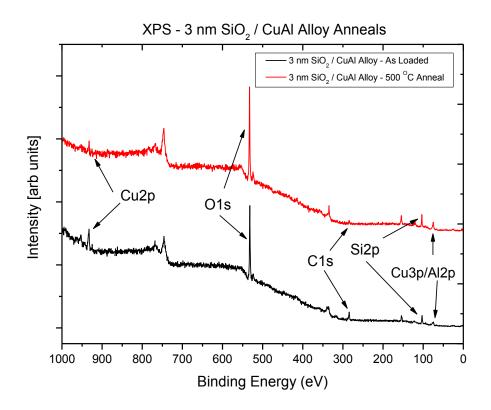

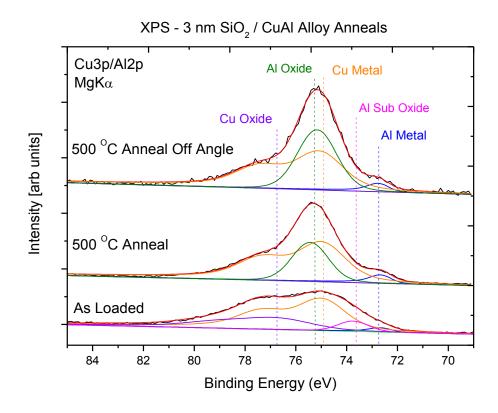

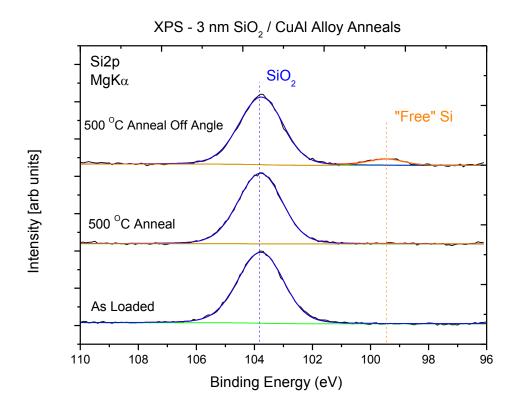

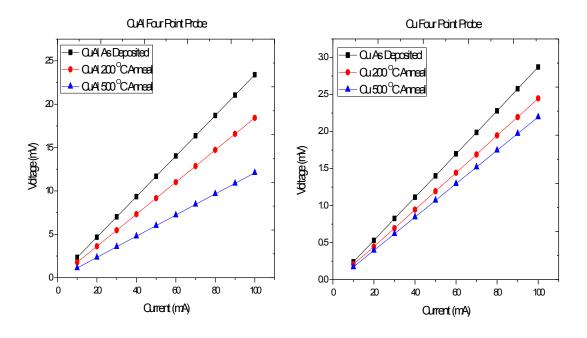

A copper-aluminium alloy is the focus of this chapter as an alternative candidate for self-forming barrier layer formation on SiO<sub>2</sub>. A Cu/Al alloy was studied as opposed to a sequential deposition study (as in the Mn studies) in order to expand upon the self-forming barrier concept. A variety of methods including X-ray photoelectron spectroscopy (XPS), secondary ion mass spectroscopy (SIMS), hard energy X-ray photoelectron spectroscopy (HAXPES),Transmission electron microscopy (TEM) and a range of electrical characterisations are employed to study a CuAl (90:10 % wt) alloy deposited on 100 nm SiO<sub>2</sub> dielectric substrates.

# <u>Chapter 7</u>: "CuAl alloy barrier layer properties for future interconnect applications"

This final experimental results chapter carries on from the previous chapter by using a CuAl alloy as a self-forming barrier. In depth electrical analysis is performed on both reference pure Cu MOS and CuAl alloy MOS devices in order to establish the effectiveness of the CuAl alloy at preventing Cu diffusion into the underlying oxide layer. Bias thermal stress (BTS) and pure thermal stress testing was performed in addition to electrical characterisation of capacitance voltage (CV) and leakage current (IV) measurements. Scanning electron microscopy was used to image both the Cu and CuAl alloy in addition to atomic force microscopy (AFM) and optical imaging of the sample surfaces following thermal stress treatments. Secondary ion mass spectroscopy (SIMS) was employed to track the diffusion of Cu into the oxide layer of the MOS devices following thermal stress measurements.

### 1.7 References

- [1] G. Moore, "Cramming more components onto integrated circuits," *Electronics*, McGraw-Hill, New York, pp. 114–117, Apr-1965.

- [2] K. Skaugen, "Intel Tick-Tock Model," in *Intel Development Forum*, 2011.

- [3] "International Roadmap For Semiconductors Interconnects," p. 6, 2006.

- [4] J. Bogan, "Growth and chemical characterisation studies of Mn silicate barrier layers on SiO<sub>2</sub> and CDO." Dublin City University. School of Physical Sciences, 01-Nov-2012.

- [5] "Performance improvements in microelectronic applications." [Online].

Available: http://web.eng.fiu.edu/syao002/5425.htm. [Accessed: 07-May-2015].

- [6] "Wolfram|Alpha: Computational Knowledge Engine." [Online]. Available: http://www.wolframalpha.com/. [Accessed: 07-May-2015].

- [7] B. Li, T. D. Sullivan, T. C. Lee, and D. Badami, "Reliability challenges for copper interconnects," *Microelectron. Reliab.*, vol. 44, no. 3, pp. 365–380, Mar. 2004.

- [8] C. M. Tan and A. Roy, "Electromigration in ULSI interconnects," *Mater. Sci. Eng. R Reports*, vol. 58, no. 1–2, pp. 1–75, Oct. 2007.

- [9] S. Yokogawa, H. Tsuchiya, Y. Kakuhara, and K. Kikuta, "Analysis of Al Doping Effects on Resistivity and Electromigration of Copper Interconnects," *IEEE Trans. Device Mater. Reliab.*, vol. 8, no. 1, pp. 216–221, Mar. 2008.

- [10] "Electricity | Physics :: Dielectrics, polarization, and electric dipole moment |

Encyclopedia Britannica." [Online]. Available:

http://www.britannica.com/EBchecked/topic/182915/electricity/71560/Dielectric

s-polarization-and-electric-dipole-moment. [Accessed: 07-May-2015].

- [11] G. Dubois, W. Volksen, T. Magbitang, R. D. Miller, D. M. Gage, and R. H. Dauskardt, "Molecular Network Reinforcement of Sol–Gel Glasses," *Adv. Mater.*, vol. 19, no. 22, pp. 3989–3994, Nov. 2007.

- [12] "http://web.stanford.edu/class/ee311/NOTES/Interconnect%20Lowk.pdf."

[Online]. Available: http://web.stanford.edu/class/ee311/NOTES/Interconnect

Lowk.pdf. [Accessed: 07-May-2015].

- [13] W. Volksen, T. P. Magbitang, R. D. Miller, S. Purushothaman, S. a. Cohen, H. Nakagawa, Y. Nobe, T. Kokubo, and G. J. M. Dubois, "A Manufacturing Grade, Porous Oxycarbosilane Spin-On Dielectric Candidate with K ≤ 2.0," *J. Electrochem. Soc.*, vol. 158, no. 7, p. G155, 2011.

- [14] G. Dubois, W. Volksen, T. Magbitang, M. H. Sherwood, R. D. Miller, D. M. Gage, and R. H. Dauskardt, "Superior mechanical properties of dense and porous organic/inorganic hybrid thin films," *J. Sol-Gel Sci. Technol.*, vol. 48, no. 1–2, pp. 187–193, May 2008.

- [15] P. Casey, J. Bogan, and G. Hughes, "Photoemission study of carbon depletion from ultralow-κ carbon doped oxide surfaces during the growth of Mn silicate barrier layers," *J. Appl. Phys.*, vol. 110, no. 12, p. 124512, Dec. 2011.

- [16] F. Lanckmans and K. Maex, "Use of a capacitance voltage technique to study copper drift diffusion in (porous) inorganic low-k materials," *Microelectron. Eng.*, vol. 60, no. 1–2, pp. 125–132, Jan. 2002.

- [17] P.-I. Wang, J. S. Juneja, Y. Ou, T.-M. Lu, and G. S. Spencer, "Instability of Metal Barrier with Porous Methyl Silsesquioxane Films," *J. Electrochem. Soc.*, vol. 155, no. 2, p. H53, 2008.

- [18] J. Koike and M. Wada, "Self-forming diffusion barrier layer in Cu–Mn alloy metallization," *Appl. Phys. Lett.*, vol. 87, no. 4, p. 041911, Jul. 2005.

- [19] J. G. Lozano, J. Bogan, P. Casey, A. P. McCoy, G. Hughes, and P. D. Nellist, "Scanning transmission electron microscopy investigations of self-forming diffusion barrier formation in Cu(Mn) alloys on SiO2," *APL Mater.*, vol. 1, no. 4, p. 042105, Oct. 2013.

- [20] A. P. McCoy, J. Bogan, L. Walsh, C. Byrne, P. Casey, and G. Hughes, "The addition of aluminium to ruthenium liner layers for use as copper diffusion barriers," *Appl. Surf. Sci.*, vol. 307, pp. 677–681, Jul. 2014.

- [21] K. Maekawa, K. Mori, N. Suzumura, K. Honda, Y. Hirose, K. Asai, A. Uedono, and M. Kojima, "Impact of Al in Cu alloy interconnects on electro and stress migration reliabilities," *Microelectron. Eng.*, vol. 85, no. 10, pp. 2137–2141, Oct. 2008.

- [22] A. McCoy, "Chemical investigations of ruthenium based barrier layer systems for future interconnect technologies." Dublin City University. School of Physical Sciences, 01-Nov-2014.

- [23] J. G. Lozano, P. Nellist, J. Bogan, P. Casey, A. McCay, and G. Hughes, "STEM Analysis Of Cu(Mn) Self-Forming Diffusion Barriers on SiO<sub>2</sub> For Applications In The Semiconductor Industry," *Microsc. Microanal.*, vol. 18, no. S2, pp. 1842–1843, Nov. 2012.

- [24] A. P. McCoy, P. Casey, J. Bogan, J. G. Lozano, P. D. Nellist, and G. Hughes, "Chemical and structural investigations of the incorporation of metal manganese into ruthenium thin films for use as copper diffusion barrier layers," *Appl. Phys. Lett.*, vol. 101, no. 23, p. 231603, Dec. 2012.

- [25] P. Casey, J. Bogan, J. G. Lozano, P. D. Nellist, and G. Hughes, "Chemical and structural investigation of the role of both Mn and Mn oxide in the formation of manganese silicate barrier layers on SiO2," *J. Appl. Phys.*, vol. 110, no. 5, p. 054507, Sep. 2011.

- [26] P. Casey, J. Bogan, B. Brennan, and G. Hughes, "Synchrotron radiation photoemission study of in situ manganese silicate formation on SiO[sub 2] for barrier layer applications," *Appl. Phys. Lett.*, vol. 98, no. 11, p. 113508, 2011.

### 2 Experimental Techniques

#### 2.1 Introduction

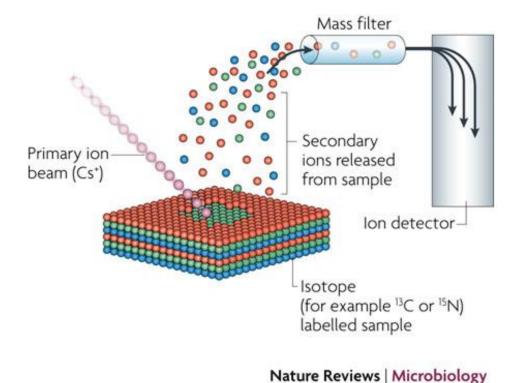

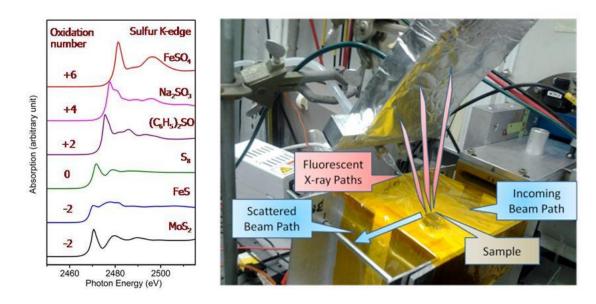

A variety of experimental techniques are used in this study in order to characterise and test Cu diffusion barrier growth, structure, chemical composition and electrical effectiveness. The main technique used in the study was an in-situ approach of metal depositions and anneal stages in conjunction with X-ray photoelectron spectroscopy (XPS) analysis. XPS is an ideal technique to use for in-situ Cu diffusion barrier layer studies however; the technique only gives information on chemical composition and chemical interactions within approximately the top 5-7 nm of the surface of interest. Other ex-situ techniques are exploited in order to gain additional information such as transmission electron microscopy (TEM), used to image the interfaces of samples and elementally map the interfaces when used in electron energy loss spectroscopy (EELS) mode. Secondary ion mass spectroscopy (SIMS) is a chemical depth profiling technique, utilising a high energy ion beam to sputter the surface of the sample of interest. As the beam sputters through the sample, ejected fragments of the sample surface are analysed with a mass spectrometer in order to track elemental changes throughout the structure of the samples. X-ray absorption measurements (XAS) is a further technique used to identify the precise chemical species present within a sample. Electrical characterisation of fabricated barrier layers is of great interest due to the industrial relevance of electrical testing of future interconnect components. Capacitance-voltage (CV) sweeps are performed on fabricated metal oxide semiconductor (MOS) structures both with and without a Cu diffusion barrier in order to test barrier effectiveness at preventing Cu diffusion into the oxide material.

# 2.2 X-ray photoelectron spectroscopy

As stated previously, the main experimental technique used in this study was X-ray photoelectron spectroscopy (XPS). The use of XPS demands an ultra-high vacuum environment to ensure effective operation of the technique and to maintain the chemical composition of the sample in a stable state throughout the measurement period. An insitu approach was typically adopted in this study, meaning that any substrates of interest were inserted into a UHV system with in-situ XPS, thin film metal deposition and annealing capabilities, thereby allowing the sample to remain in UHV during the course of experimental procedure without the need to break vacuum and expose the interface of interest to atmospheric contamination. This allowed XPS spectra to be acquired from ultra-clean interfaces, thereby minimising any contamination problems during experimentation.

### 2.2.1 Basic Principles

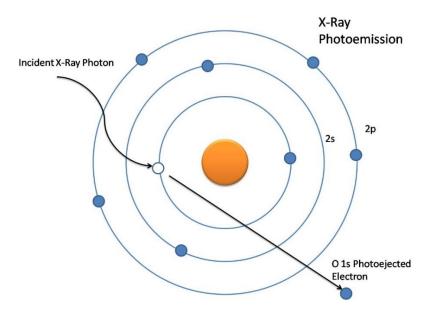

XPS is a highly surface sensitive technique used to identify the chemical species present in approximately the top ~7 nm of a surface of interest. This is achieved by irradiating the sample with mono-energetic soft X-rays [1]. Conventional XPS typically utilises a dual X-ray anode configuration of a magnesium (Mg) and aluminium (Al) anode in order to produce characteristic X-ray lines of Mg K $\alpha$  (1253.6 eV) and Al K $\alpha$  (1486.6 eV) energies. As the sample is irradiated by either anode radiation, electrons are emitted from the sample surface via the photoelectron effect with binding energy (E<sub>b</sub>) given as;

$$E_h = hv - KE$$

Equation 2.1: Binding energy of an electron.

Where h is Planks constant (6.626 x 10<sup>-34</sup> m<sup>2</sup>kg/s), v is the frequency of the electromagnetic radiation which caused the photoelectron to be ejected and KE is the kinetic energy of the electron ejected from the atom. Due to the fact that the photon energy (hv) is well defined, a measurement of the kinetic energy of the emitted electron should give the necessary information needed to obtain the binding energy of the electron from its initial atomic state. In addition, due to the well-defined electron energy levels within an atom, elemental identification can be achieved via the measurement of the kinetic energy of electrons emitted from the sample surface during irradiation from the anode target. The fact that soft X-rays are used, in contrast to conventional photoelectric effect which typically utilises UV radiation, electrons from higher binding energy core levels of the atom can be ejected, as schematically shown in Figure 2.1.

Figure 2.1: Creation of a photoelectron via the absorbance of an incident X-ray photon [2].

Thus, using a relatively more energetic radiation source, deeper core level electrons can be ejected, enabling multiple electron levels in the atom to be measured. In order to precisely measure the binding energy of emitted electrons, an accurate measurement of the kinetic energy of the photoemitted electrons must be made. This measurement is achieved via the use of an electron energy analyser as seen in Figure 2.2 which is connected to a data acquisition system.

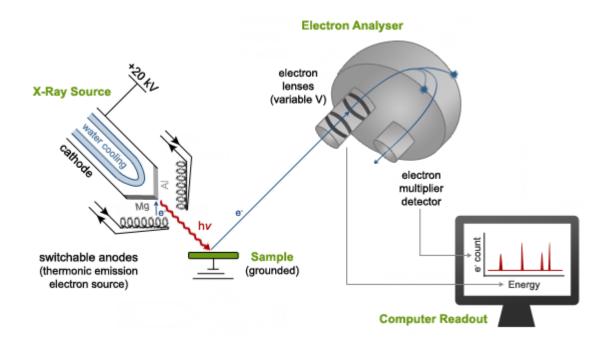

Figure 2.2: Typical XPS experimental set up [3]

As seen in Equation 2.1, the binding energy is only dependant on the kinetic energy of the electron (assuming the exact photon energy of the radiation used is known). This however is only correct for isolated atoms [4], and not true for electrons emerging from a solid surface sample, as used in XPS analysis. Consideration must be given to the workfunction of the material ( $\phi_s$ ) which is defined as the energy difference between the sample Fermi level and the vacuum level. Thus, Equation 2.1 must be modified to allow for this change, giving:

$$E_b = hv - KE - \Phi_s$$

Equation 2.2: Modified binding energy equation due to the sample workfunction.

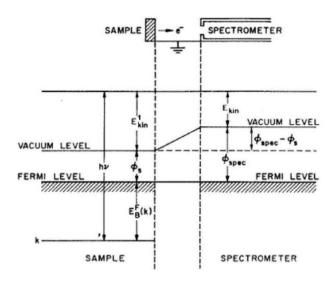

As stated previously, the sample and electron analyser must be grounded during analysis. This then causes both the Fermi level of the sample and spectrometer to be at the same energy level as schematically shown in Figure 2.3.

Figure 2.3: Energy band diagram of sample and electron analyser grounded [5].

As can be seen from Figure 2.3, the kinetic energy of the electron as measured by the electron analyser will not be equal to the value described via Equation 2.1 due to the effects of both the sample workfunction ( $\phi_s$ ) and the spectrometer workfunction ( $\phi_{spec}$ ) [5]. Thus the actual kinetic energy of the electron (KE) as measured by the spectrometer (KE<sub>spec</sub>) will be given as:

$$KE = KE_{spec} + (^{\Phi}_{spec} - ^{\Phi}_{s})$$

Equation 2.3: Kinetic energy of electron measured by spectrometer due to variable workfunction differences of sample and spectrometer.

When this definition of KE is substituted into Equation 2.2, it is found that the binding energy of the electron as measured via the kinetic energy measurement in the electron energy analyser, with work function,  $\phi_{\text{spec}}$ , can be given as:

$$E_b = hv - KE_{spec} - \Phi_{spec}$$

Equation 2.4: Binding energy of the electron measured via spectrometer following photoemission process.

Thus, if the photon energy (hu), kinetic energy of the electron as measured by the spectrometer ( $KE_{spec}$ ) and workfunction of the spectrometer ( $\phi_{spec}$ ) are known, the binding energy of the electron before being emitted from the atom can be calculated. The workfunction of the spectrometer can be experimentally found by calibrating the system with a known standard such as gold (Au). A scan of the intense Au 4f peak, which has a well-established binding energy (BE) position of 83.98 eV [6] allows calibration of the binding energy axis during data acquisition.

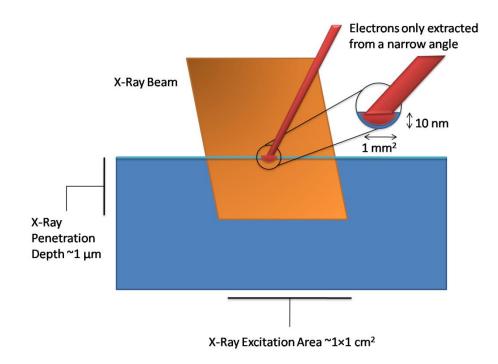

## 2.2.2 Sampling Depth of XPS

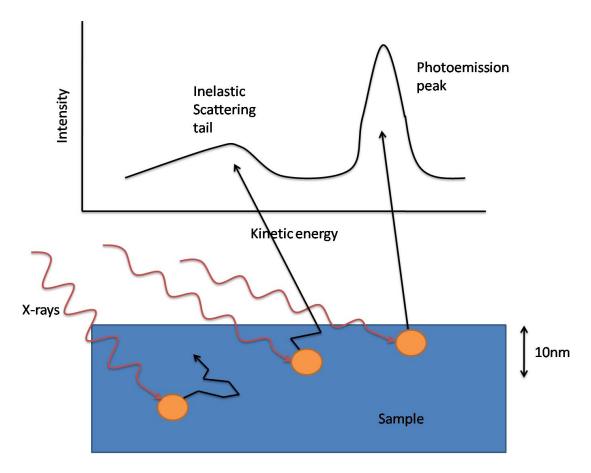

As stated previously, XPS is a very surface sensitive technique, with the ability to acquire chemical information from ~ 5-7 nm into a sample surface. The XPS sampling depth for a particular surface depends on the sample parameters such as density and the angle of detection. Thus the guide thickness of ~ 7 nm sampling depth can be drastically altered via the above parameters. Figure 2.4 schematically illustrates the relative areas and depth penetrations of both the incoming X-ray photon and outgoing photoelectrons. As can be seen, the average depth penetration of a 1 keV photon into solid matter is on the order of

$\sim 1$  µm, this is in contrast to the escape depth of the electrons from the sample surface which is on the order of < 10 nm. Photons of 1 keV do not interact with matter as much as electrons, which interact strongly within the sample via collisions.

Figure 2.4: Diagram of sample surface during XPS analysis showing the typical penetration depth for the incident X-rays and the sampling depth of the photoemitted electrons [4].

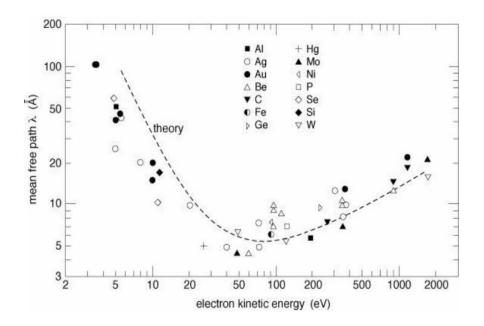

If no electron collisions occurred within the sample following the photoabsorption process, the XPS sampling depth would be equal to the photon penetration depth. Thus it can be seen that the depth sensitivity of XPS is not a human engineered design, but a result of probabilistic scattering of electrons via collisions within the sample. The probability of an electron scattering within the sample following photoemission can be directly related to the sampling depth, showing that a low probability of collisions gives a greater sampling depth. Thus an understanding of the mean free path (MFP), which is defined as the average distance an electron with a given energy will travel in the sample

XPS analysis. Figure 2.5 shows a plot of electron MFP as a function of kinetic energy for a wide range of different materials. The inelastic mean free path (IMPF) is defined the average distance an electron of a certain kinetic energy will travel in a material before undergoing an inelastic collision (a collision which alters the original kinetic energy

Figure 2.5: Mean free path (MFP) for electrons in a variety of materials with various kinetic energies [7].

value). The probability of an electron undergoing an inelastic collision within the sample P(d) following photoemission is given as:

$$P(d) = \exp(-\frac{d}{\lambda})$$

Equation 2.5: Probability of electron undergoing inelastic collision as a function of travelling distance.

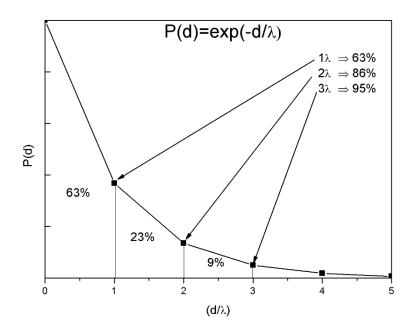

where d is the travel distance of the electron and  $\lambda$  is the IMFP of the electron of a certain kinetic value within a particular material (sample and kinetic energy dependant). Using Equation 2.5, a plot can be generated showing that as the electron travels further through the solid sample (d increasing) the probability of an inelastic collision increases. This curve is shown in Figure 2.6, which indicates that the majority (~95 %) of non-scattered electrons come from the top  $3\lambda$  of the sample surface, which is commonly referred to as the sampling depth. As the distance travelled increases to  $4\lambda$ , it can be seen that the probability of an electron not undergoing an inelastic collision is virtually zero. It is however theoretically possible (although extremely unlikely) that an electron which was ejected from the sample at the highest photon penetration depth into the sample could traverse through the sample and into the electron analyser without undergoing a scattering

Figure 2.6: Graph of the probability of an electron undergoing an inelastic collision within a sample material [2].

event. In addition the penetration depth of a photon into a solid material is also given as a probabilistic event, as seen in the Beer-Lambert law shown in Equation 2.6.

$$I = I_0 \cdot exp^{(-\mu x)}$$

Equation 2.6: Beer-Lambert law.

where  $I_0$  is the original intensity of photon intensity before entering the sample,  $\mu$  is the linear absorption coefficient (material and photon energy dependant) and x is the distance travelled into the sample. Due to the exponential decay of the original intensity (I<sub>0</sub>) of the radiation to an intensity of I at a distance x into the sample, it is seen that the probability is small, but non-zero that a photon could travel to the bottom of the sample and cause photoemission of an electron. As stated above, this electron then has the ability to travel through the sample without undergoing any inelastic scattering and be detected by the electron analyser. This shows that theoretically the sampling depth of XPS is infinite, however given the extremely low probabilities of these events actually happening, and the fact that 95% of the electrons come from within the top  $3\lambda$  of the sample surface, XPS is practically defined as having a sampling depth of  $\sim 7$  nm /  $3\lambda$ . Only electrons which escape the surface and enter the analyser without undergoing inelastic collisions can be related back to the original BE of that electron, thus providing elemental and chemical information from the sample surface. Electrons which undergo inelastic scattering contribute to the XPS spectra in various ways, mainly as an increase in background of the spectra as seen in Figure 2.7, in contrast to the non-scattered electrons which give rise to sharp well defined photoemission peaks.

Figure 2.7: Scattered and non-scattered electrons contributing to the XPS spectra [4].

### 2.2.3 Spectral Features

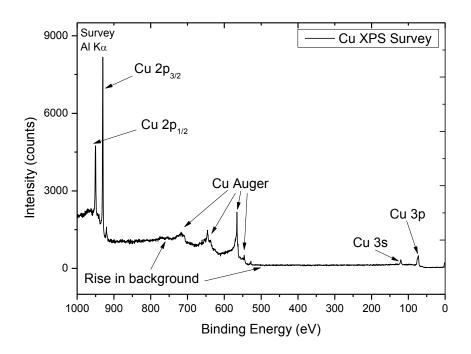

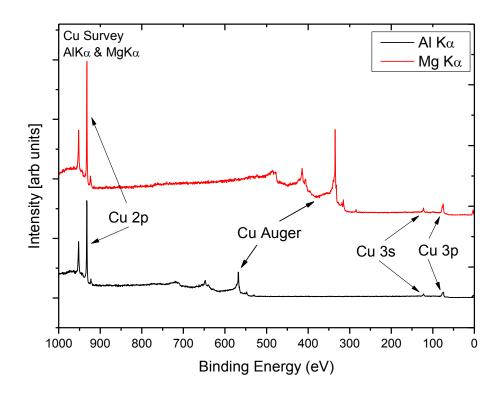

The plot of a typical XPS survey scan (0 - 1000 eV) for a pure Cu film is shown in Figure 2.8 with the electron binding energy scale on the x-axis (eV) and with the corresponding number of electron counts for each BE position on the y-scale.

Figure 2.8: XPS survey spectra of a pure Cu film.

As can be seen from the Cu survey spectra, a number of spectral features are evident. Two photoemission peaks at ~ 75 eV and ~ 123 eV are due to non-scattered electrons photoemitted from the Cu 3p and Cu 3s orbitals, respectively. Between the BE positions of ~ 550 eV and ~ 750 eV are a number of features associated with Cu Auger processes which will be described in detail in a later section. At higher BE ( ~ 933 eV and ~ 953 eV) are photoemission lines originating from the Cu 2p orbital, with orbital splitting evident from the well separated Cu 2p<sub>3/2</sub> (~933 eV) and Cu 2p<sub>1/2</sub> (~953 eV). Thus is can also be seen that the Cu 2p orbitals are at a higher BE position relative to the outer orbital shells of the Cu 3s and Cu 3p lines. An important point to note is the fact that the Cu 2p photoemitted electrons have a kinetic energy much lower than the Cu 3p photo-emitted electrons (~ 858 eV kinetic energy difference). As stated previously, photoemitted electrons with a larger KE will have a larger IMFP, thus increasing the effective sampling depth. This indicates that although the sampling depth for the Cu film may be on the order

of ~ 7 nm, not all spectral features may come from this depth. In fact the Cu 2p lines, due to the much lower KE of the ejected electrons, are much more surface sensitive relative to the higher KE of the Cu 3p orbital. In addition to the spectral lines described above, a rise in the background of the spectrum is also noted towards higher binding energies (lower KE). This is due to scattered photoemitted electrons loosing KE, and contributing to the spectral background. Auger lines, as observed in Figure 2.8 are a spectral features caused via the Auger process which is an internal electron emission process as schematically depicted in Figure 2.9.

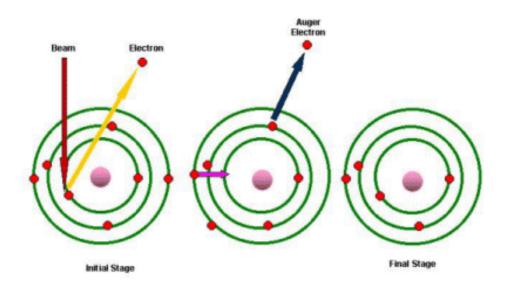

Figure 2.9: Auger process within an atom [8].

As shown within the diagram, an initial inner-core electron is removed due to absorption of a photon or energy transfer from an incident high energy electron-beam. An outer level electron then fills the vacancy left from the initial electron ejection. Quantum mechanics shows that the electron, originally in the outer orbital, has too much energy to reside in the inner orbital when it makes the transition to fill the vacancy. Thus the energy can be transferred to an electron in an outer orbit, where upon if this electron receives enough energy it can be ejected from the atom and detected in the photoemission spectrum. In

contrast to photoemission peaks, where the KE of the ejected electron is dependent upon the photon energy used, the Auger process is independent of initial photon energy due to the fact that it is an internal excitation process within the atom. Thus if photoemission spectra are acquired with both the Mg K $\alpha$  and Al K $\alpha$ , the photoemission peaks for the Cu sample will reside in the same positions on a binding energy scale, whereas the Auger lines will move depending on what anode is selected. If a kinetic energy x-axis is selected, the Auger lines would remain stationary upon anode switching, with the photoemission lines moving to new KE positions. This effect, as seen in Figure 2.10, where a Cu film was subjected to two XPS survey spectra scans, with the Al X-ray anode and also with the Mg X-ray anode. A shift in Auger features is evident relative to the locked positions of the photoemission peak features as a binding energy axis is used.

Figure 2.10: XPS Cu survey spectra using both Al and Mg anodes showing the apparent shift on the AES spectral features on a binding energy axis.

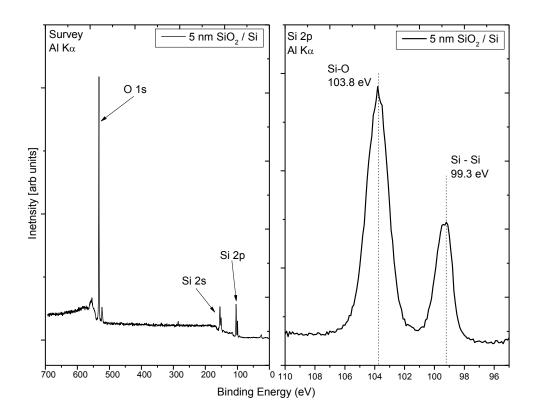

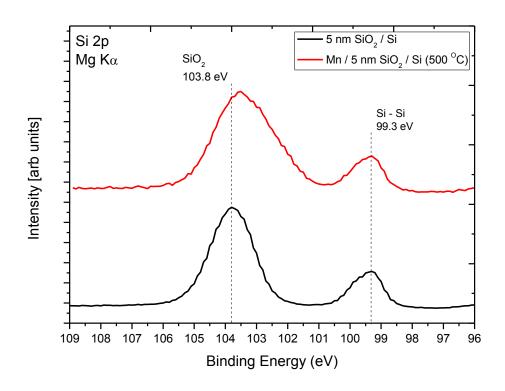

Survey spectra, typically taken from 0 eV upwards to  $\sim$  1000 eV are primarily used to identify all elements within the sample surface. Once all elements have been identified, narrow window, high resolution spectra of the strongest photoemission lines for each element are taken. Figure 2.11 displays XPS survey and narrow window spectra for a 5 nm thermally grown SiO<sub>2</sub> layer on a Si substrate.

Figure 2.11: XPS survey and Si 2p spectra of 5 nm SiO<sub>2</sub> on Si substrate.

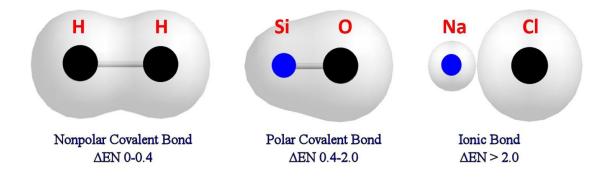

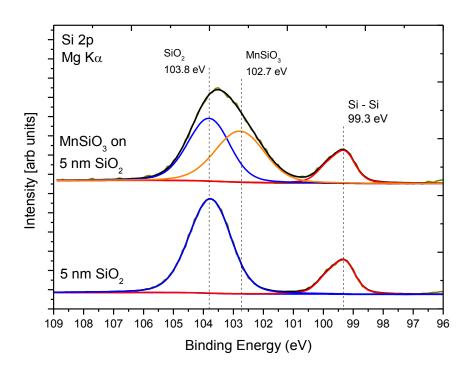

As can be seen from the survey spectra, a large O 1s peak is evident, attributed to the oxygen in the thin 5 nm over layer of SiO<sub>2</sub>. Additional photoemission peaks are identified at lower binding energy (LBE) attributed to the Si 2s and Si 2p photoemission lines. A high resolution narrow window scan of the Si 2p spectrum reveals two component peaks. Due to the ultra-thin nature of the 5 nm SiO<sub>2</sub> film, signal from the underlying Si substrate is also acquired. The substrate Si, which is bonded to Si only (Si-Si bonds) appears at a binding energy position of 99.3 eV. The higher binding energy (HBE) component at a position of 103.8 eV is attributed to the over layer SiO<sub>2</sub>, within which silicon is bonded to oxygen. This identification of chemical state bonding can be explained due to the fact that different elements have different electronegativity values. The effect of electronegativity values on chemical bonding is schematically shown in Figure 2.12.

Figure 2.12: Electronegativity influence on chemical bonding showing changes in electron cloud densities [9].

As seen, two atoms of the same electronegativity (hydrogen for example) in a chemical bond, share the outer shell electrons equally in a perfectly covalent bonding arrangement. If two atoms of different electronegative values are involved in a chemical bond, a slight electron charge transfer is noted, with the majority of the negative charge residing around the atom with the highest electronegativity (in this case oxygen), thereby creating a slight positive charge around the atom with the lower electronegativity (in this example, silicon). If two atoms with a large difference in electronegativity bond, total charge transfer occurs, this is called ionic bonding and is demonstrated with the ionic bond NaCl, where the electronegative Cl receives the full share of the valence electron from the Na atom, thereby leaving the Na atom in an overall positive state. This explains the "chemical shift" of the SiO<sub>2</sub> peak in the Si 2p spectrum of Figure 2.11 relative to the Si-Si bonding of the substrate. As photoelectrons are emitted from the Si 2p orbital in the SiO<sub>2</sub> layer, they are being excited from a silicon atom in a slightly positive charge, lowering the KE value relative to the silicon-silicon bonds in the substrate. If the silicon atoms were bonded to an element of lower electronegativity than itself, a new peak would emerge at

a LBE position relative to the silicon-silicon bonding of the substrate. This "chemical-shift" allows XPS to not only perform elemental identification, but also identify the specific bonding environment for each element present. This property of XPS is heavily exploited in this thesis to understand the nature of chemical bond formation for barrier layers.

### 2.2.4 Additional Spectral Features

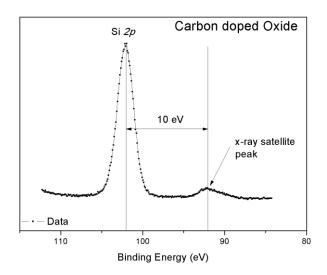

In addition to photoemission peaks, Auger lines and chemically shifted peaks, further spectral features can be seen within XPS spectra. Figure 2.13 shows the feature associated with a higher energy X-ray component in addition to the main  $K\alpha$  component used in conventional XPS which is present in spectra acquired by both of the commonly used Al and Mg anodes.

Figure 2.13: Si 2p spectrum showing X-ray satellite feature [2].

Due to the fact that higher energy X-ray components will produce photoelectrons with a higher kinetic energy, this will produce a small peak at lower binding energy relative to the main photoelectron peak. This feature ~ 10 eV (typical position for strongest satellite peak using Al anode) at LBE can be problematic during peak fitting analysis (discussed in a later chapter) due to the fact that these satellite peaks may overlap with the main photoemission lines, for example in the Mn 2p spectra. The use of an X-ray monochromator eliminates these additional X-ray components (not available within this study). A list of satellite features and their relative intensities for both Al and Mg anodes are given in Table 2-1.

|                            | α1,2 | α3  | 0.4  | α5   | <b>0</b> .5 | β    |

|----------------------------|------|-----|------|------|-------------|------|

| Mg<br>displacement<br>(eV) | 0    | 8.4 | 10.1 | 17.6 | 20.6        | 48.7 |

| Relative height (%)        | 100  | 8   | 4.1  | 0.6  | 0.5         | 0.5  |

| Al displacement (eV)       | 0    | 9.8 | 11.8 | 20.1 | 23.4        | 69.7 |

| Relative height (%)        | 100  | 6.4 | 3.2  | 0.4  | 0.3         | 0.6  |

Table 2-1: X-ray satellite features for both Al and Mg anodes [10].

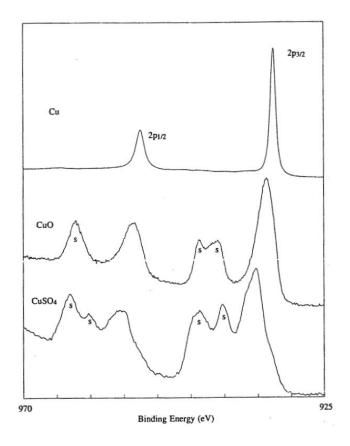

Further to satellite features, shake-up features can also be seen within XPS spectra. Figure 2.14 shows these shake-up features in the Cu 2p spectra of various Cu species.

Figure 2.14: Shake-up features associated with Cu bonding states within the Cu 2p spectrum [11].

These spectral features are caused by coupling of the photoemitted electrons with valence states within the atom, thereby imparting energy to these states. The result is a lower kinetic energy emission, manifesting as a higher binding energy component.

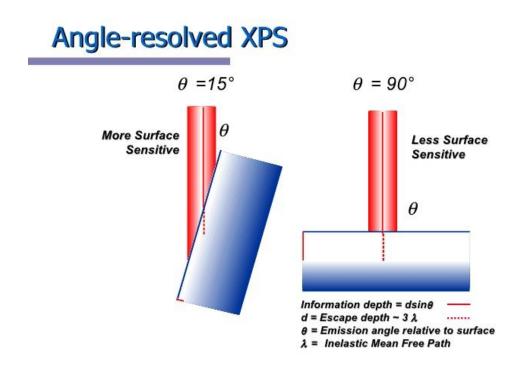

### 2.2.5 Angularly Resolved XPS

In order to maximise the effective sampling depth into the material, the sample is typically placed at an angle of 90° (normal emission) with respect to the analyser. Although at this angle, XPS is considered to be extremely surface sensitive, by rotating the sample off-

angle relative to the analyser, even greater surface sensitivity can be obtained as shown in Figure 2.15

Figure 2.15: Angularly resolved XPS (ARXPS) and its impact on sampling depth [12].

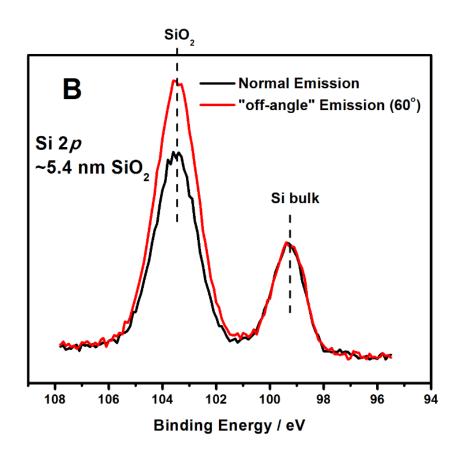

As the sample is rotated relative to the analyser, increased surface sensitivity is gained due to the fact that sampling depth is effectively reduced. This effect is demonstrated in Figure 2.16, using a 5 nm thermal SiO<sub>2</sub> layer on a Si substrate showing that the surface localised oxide layer increases in intensity relative to the substrate silicon signal as the emission angle is changed from normal emission to 60° off normal.

Figure 2.16: ARXPS demonstrated using 5 nm SiO<sub>2</sub> over layer on Si substrate

## 2.3 Electrical Measurements

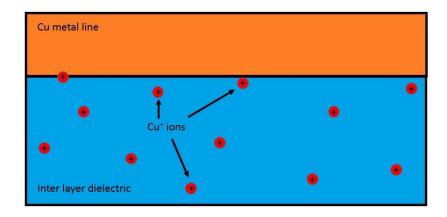

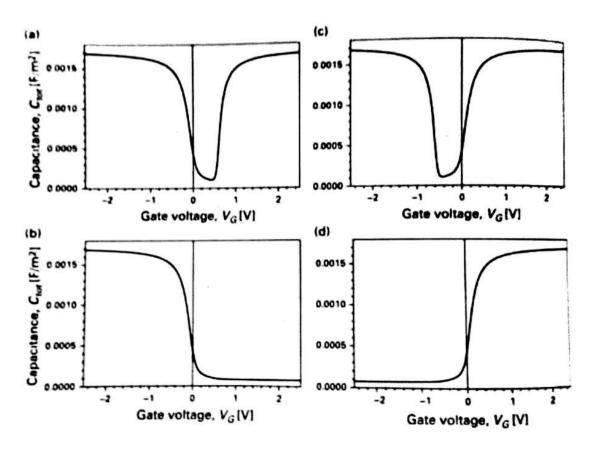

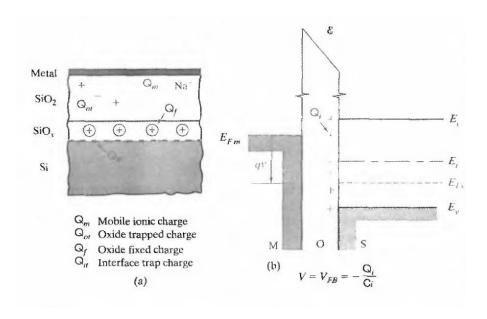

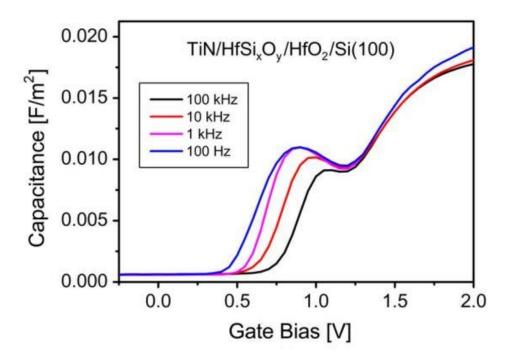

Electrical characterisation of barrier materials is of great importance due to the electrical nature of the interconnect structures within which the barrier will reside. As stated previously, Cu has a tendency to diffuse into any surrounding ILD materials in the form of Cu<sup>+</sup> ions [7-10] [13-16]. Due to the charged nature of the diffusing Cu, electrical measurements sensitive to charge detection can be used to investigate Cu ion diffusion into ILD materials. Capacitance-voltage characterisation of MOS structures provides an ideal method to test for this Cu diffusion activity. In addition to CV measurements, current-voltage (IV) leakage measurements can also be used to study Cu diffused into ILD materials, due to the heightened leakage current associated with the presence of Cu in the dielectric material.

#### 2.3.1 The MOS structure

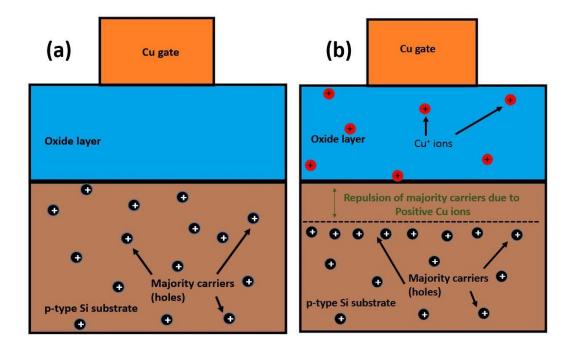

In order to electrically characterise the effectiveness of barrier layer materials at preventing Cu ion diffusion, an electrical device must be fabricated, which allows the diffusion of Cu into a dielectric layer, and also allows the incorporation of a barrier layer between the Cu layer and ILD material. Cu ion diffusion into an ILD material is schematically shown in Figure 2.17.This indicates that if Cu<sup>+</sup> ions diffuse into a dielectric material, that dielectric will exhibit an overall positive charge.

Figure 2.17: Schematic illustration of Cu ion diffusion into an ILD material.

Thus, if a technique can be developed to identify this charged state, a method of Cu ion diffusion detection can be realised. By fabricating a MOS structure with a Cu metal gate on a SiO<sub>2</sub> dielectric layer grown on adoped Si substrateas shown in Figure 2.18 (a), the effects of Cu ion diffusion into the dielectric can be detected by CV measurements.

Figure 2.18: Cu MOS device (a) without Cu diffusion and (b) with Cu diffusion into the ILD.

As can be seen in Figure 2.18 (b), if Cu<sup>+</sup> ions diffuse into the dielectric material, they can repel the majority carriers of a p-type Si substrate (or attract majority electrons in a n-type substrate). This doped substrate is therefore sensitive to the presence of any charge build up in the oxide layer, making MOS structures ideal for detection of Cu ion diffusion. Additionally, any barrier layer under test can be deposited onto the dielectric layer before Cu gate deposition in order to test the effectiveness of the barrier at preventing Cu diffusion.

### 2.3.2 Capacitance-voltage sweep

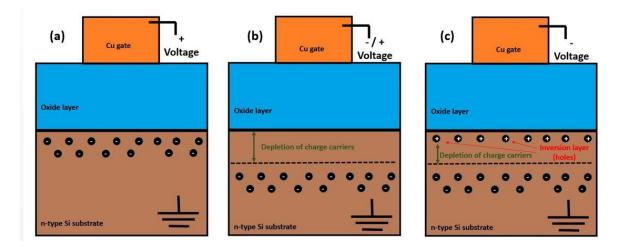

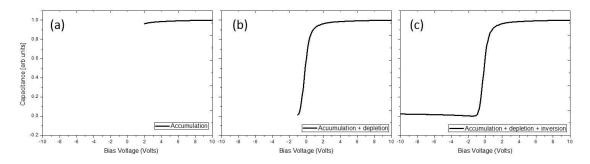

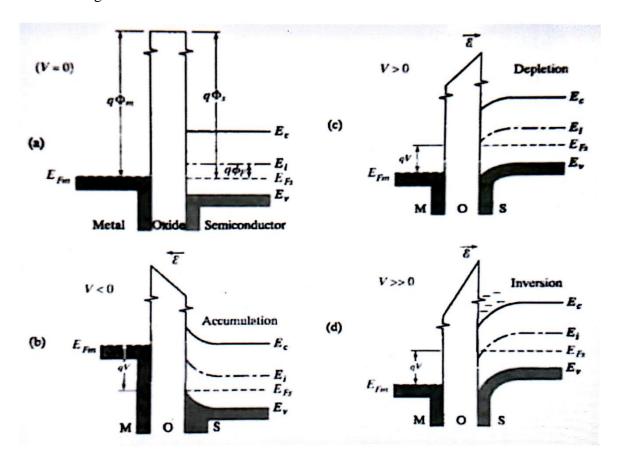

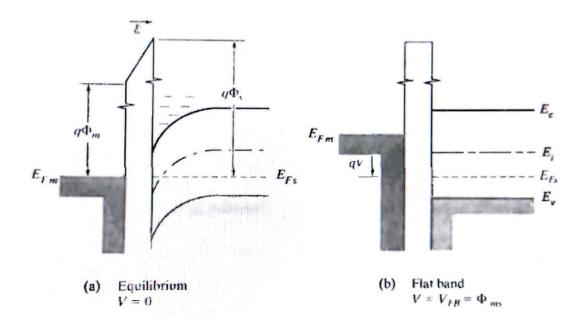

The MOS structure can be viewed as a capacitor structure, due to the metal gate, dielectric layer and doped Si substrate. In contrast to a traditional metal-insulator-metal (MIM) structure (which has constant capacitance, irrespective of applied voltage), the MOS structure will have a variable capacitance, due to the fact that a semiconductor is used as one of the oxide electrical contacts. This can be explained via Figure 2.19, which shows an n-type Si MOS capacitor subjected to various gate voltages while grounding the Si substrate.

Figure 2.19: MOS capacitor subjected to (a) positive gate bias, (b) intermediate bias and (c) negative bias.

As can been seen in (a), when the gate voltage is positive, an accumulation of majority carriers (electrons in an n-type Si substrate) occurs at the Si/SiO<sub>2</sub> interface, thus the device acts as a typical capacitor structure, with the capacitance due to the oxide layer calculated as:

$$C_{ox} = \frac{k\varepsilon A}{d}$$

Equation 2.7: Oxide capacitance of a MOS structure in accumulation.

where k is the dielectric constant of the oxide layer,  $\varepsilon$  is the electrical permittivity of free space, A is the area of the gate electrode and d is the thickness of the oxide layer.

As the voltage is decreased towards negative values, a depletion layer (no charge carriers present) forms in the Si substrate. This depletion layer acts as an additional capacitor in series with the dielectric capacitance and can be calculated as:

$$\frac{1}{C_{total}} = \frac{1}{C_{ox}} + \frac{1}{C_{Dep}}$$

Equation 2.8: Capacitors in series relating to the dielectric capacitance and the capacitance associated with the depletion region.

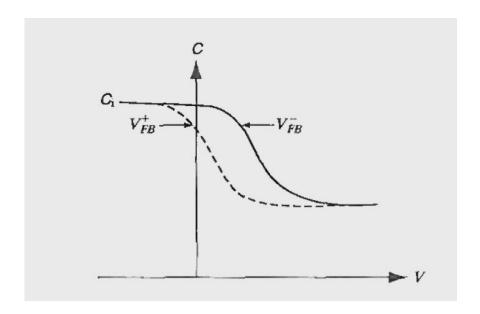

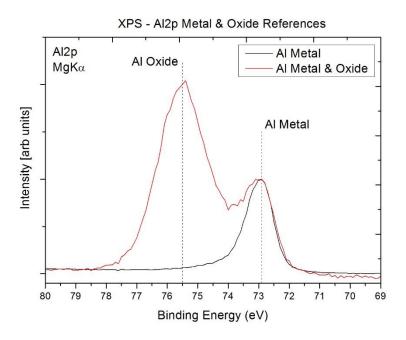

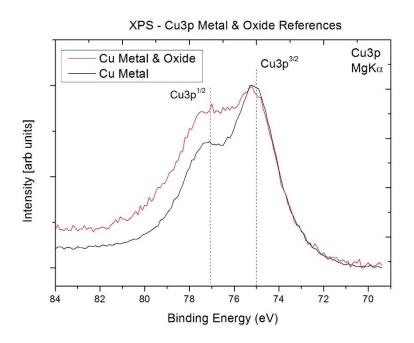

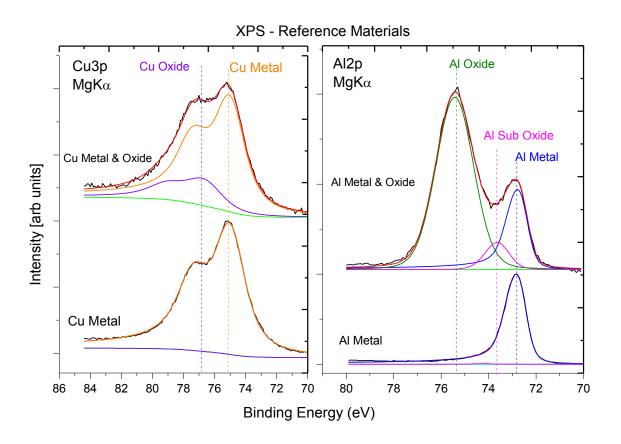

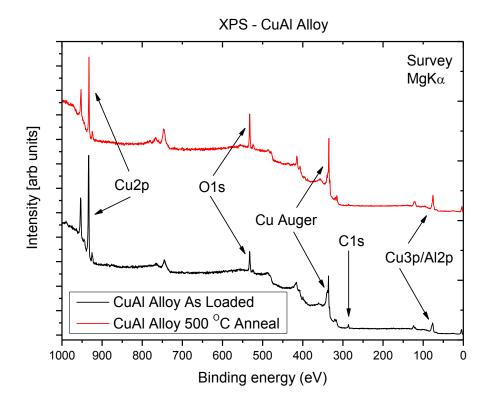

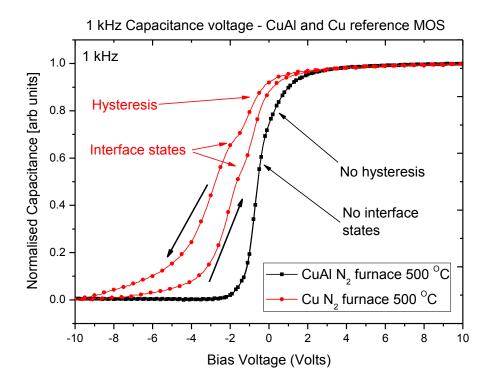

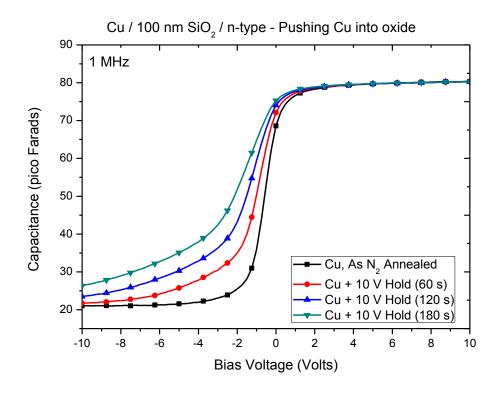

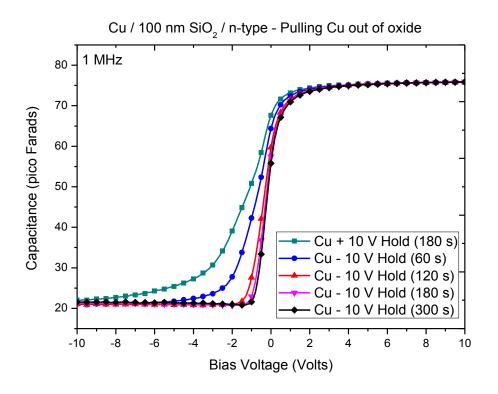

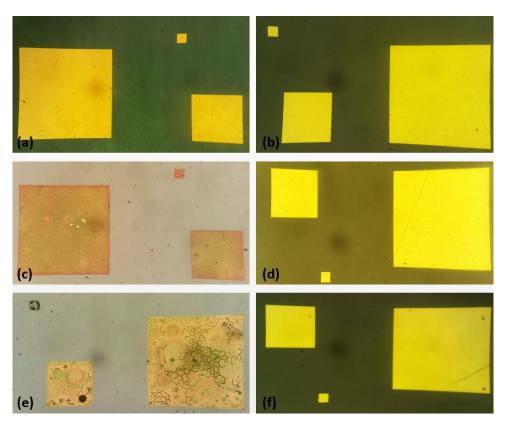

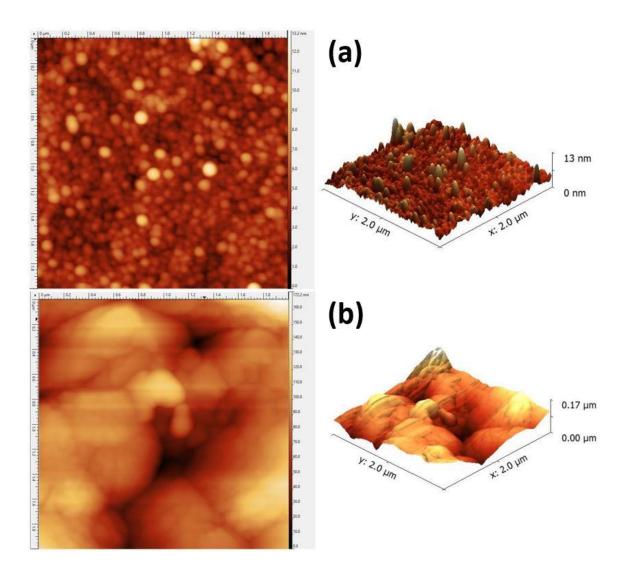

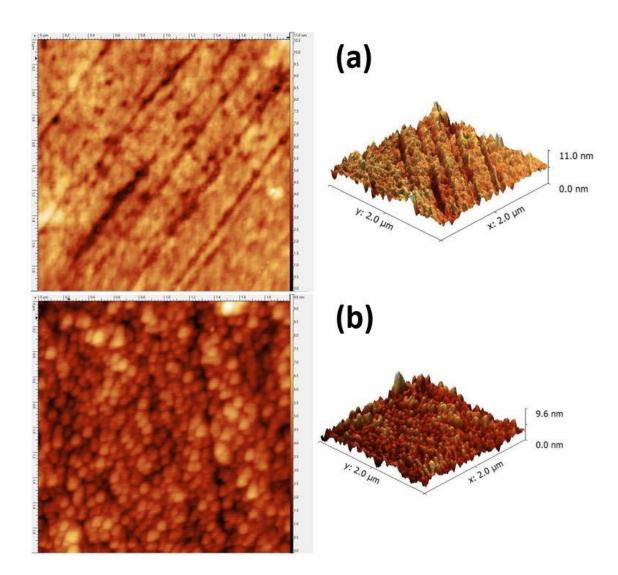

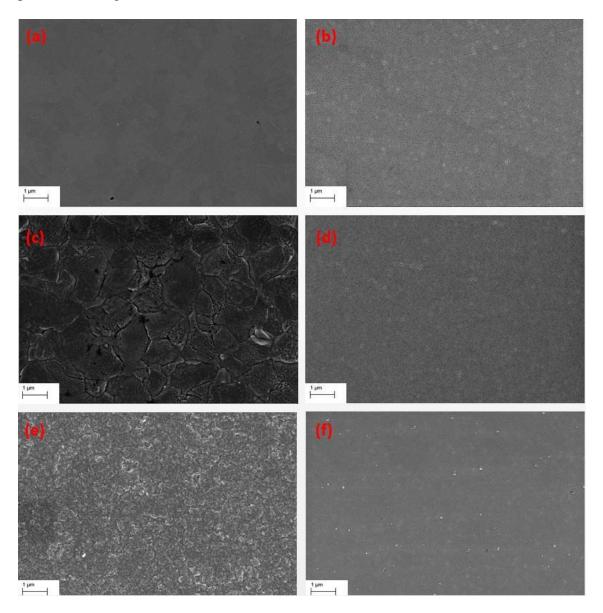

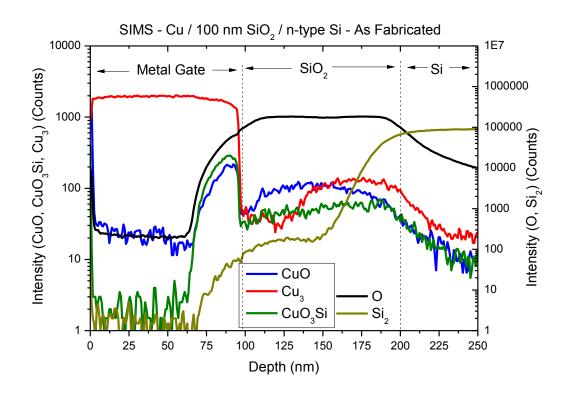

where  $C_{Dep}$  is the capacitance due to the depletion layer formed, which can be calculated from Equation 2.7 using the k value of Si, and depletion width d.