## Frequency dispersion reduction and bond conversion on *n*-type GaAs by *in situ* surface oxide removal and passivation

C. L. Hinkle, <sup>a)</sup> A. M. Sonnet, and E. M. Vogel<sup>b)</sup>

Department of Electrical Engineering, The University of Texas at Dallas, Richardson, Texas 75080, USA

S. McDonnell and G. J. Hughes

School of Physical Sciences, Dublin City University, Glasnevin, Dublin 9, Ireland

M. Milojevic, B. Lee, F. S. Aguirre-Tostado, K. J. Choi, J. Kim, and R. M. Wallace Materials Science and Engineering, The University of Texas at Dallas, Richardson, Texas 75080, USA

(Received 4 September 2007; accepted 2 October 2007; published online 19 October 2007)

The method of surface preparation on *n*-type GaAs, even with the presence of an amorphous-Si interfacial passivation layer, is shown to be a critical step in the removal of accumulation capacitance frequency dispersion. *In situ* deposition and analysis techniques were used to study different surface preparations, including NH<sub>4</sub>OH, Si-flux, and atomic hydrogen exposures, as well as Si passivation depositions prior to *in situ* atomic layer deposition of Al<sub>2</sub>O<sub>3</sub>. As–O bonding was removed and a bond conversion process with Si deposition is observed. The accumulation capacitance frequency dispersion was removed only when a Si interlayer and a specific surface clean were combined. © *2007 American Institute of Physics*. [DOI: 10.1063/1.2801512]

GaAs has once again attracted attention as an alternative substrate for metal oxide semiconductor (MOS) technologies. The advantages of GaAs over silicon are well-known, mainly having a higher electron mobility and breakdown voltage as well as a direct band gap suggesting GaAs for a wide range of devices. The elimination of anomalous frequency dispersion of the accumulation capacitance of GaAs MOS devices is a major motivation behind surface and interface treatment studies. Previous reports have attributed this dispersion, viz., the reduction of maximum capacitance with increasing measurement frequency, to a high density of interface states which results in Fermi-level pinning. Recent studies have indicated that the disruption of As-O bonding at the dielectric/GaAs interface results in an unpinned interface. Revisiting earlier works on Si passivation of GaAs surfaces (see, for example, Refs. 2 and 3), recent reports of Si deposition on GaAs for surface passivation in conjunction with high-k dielectrics (for example, Refs. 4 and 5), have stimulated this study using in situ deposition and analysis methods. In this letter, in situ analysis techniques are used to correlate differences in electrical characteristics caused by different surface treatments employed on the technologically relevant *n*-type GaAs surface for use in enhancement mode transistors.

The samples used in this work were n-type Si-doped GaAs wafers with a doping concentration of  $5 \times 10^{17}$  cm<sup>-3</sup>. One set of samples was degreased in acetone, methanol, and isopropyl alcohol for 1 min each, followed by a 3 min etch in 29% NH<sub>4</sub>OH, and dried with N<sub>2</sub>, while another set was prepared, *in situ* with no chemical treatment, using a hydrogen cracker source (cell temperature of 1400 °C,  $P_{\rm H_2}$ =1  $\times$  10<sup>-6</sup> mbar) producing atomic H with a substrate temperature of 430 °C for 30 min. Silicon of various thicknesses was deposited at room temperature on treated GaAs by

e-beam evaporation (deposition rate=18–132 Å/min in a multitechnique deposition/characterization system (base pressure= $2\times10^{-11}$  mbar). MOS capacitors were made using such treated surfaces followed by atomic layer deposition (ALD) of 10 nm of Al<sub>2</sub>O<sub>3</sub> using trimethylaluminum (TMA) and H<sub>2</sub>O at 300 °C in an adjacent chamber and *ex situ*, rf sputtered TaN as the gate metal using shadow masks. An *ex situ* electron-beam evaporated Ni/Au/Ge alloy annealed at 425 °C was used as an Ohmic back contact. 10

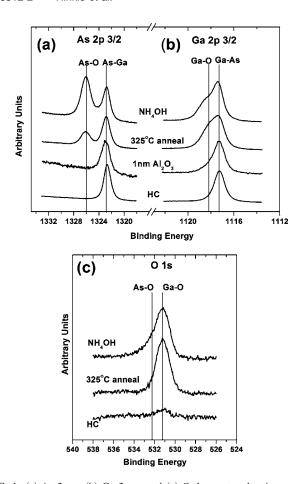

The two types of surface cleans produce widely disparate surfaces with respect to bonding. The native oxide of GaAs exhibits  $\mathrm{As^{+5}}$  and  $\mathrm{As^{+3}}$  oxidation states in addition to Ga–O formation. Exposure of the native oxide to the NH<sub>4</sub>OH etch reduces the As–O bond concentration, as seen in photoelectron spectroscopy. As–O bonding is further reduced by a post-etch, *in situ* anneal in vacuum up to 325 °C, as seen by monochromatic (Al  $K\alpha_{1,2}$ , 1486.7 eV) x-ray photoelectron spectroscopy (XPS) in Fig. 1(a). Analysis of the corresponding O 1s region for the annealed surface [Fig. 1(c)] reveals that the O concentrations for the etched surface and the annealed surface are comparable, indicating no significant loss of oxygen and suggesting that the bond conversion from As–O to Ga–O bonding is favored with such treatments.  $^{13,14}$

Atomic hydrogen exposure removes As-O and Ga-O bonds by producing water and unstable As and Ga oxides that desorb at the 430 °C substrate temperature used here. Figures 1(a) and 1(b) show the striking difference in the concentrations of As-O and Ga-O bondings, respectively, for each of the two treatments with both peaks being below the detection limit after H exposure. Figure 1(c) illustrates the reduction in the total amount of oxygen after exposure to the atomic hydrogen.

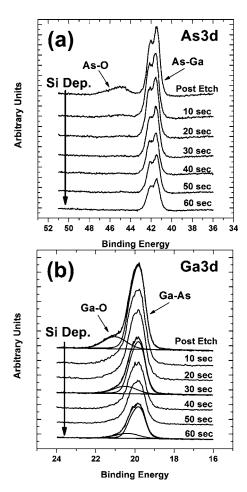

Exposure of the NH<sub>4</sub>OH-etched surface to a Si flux<sup>15</sup> also results in the reduction of As–O bonding [Fig. 2(a)] in favor of Si–O bond formation without the loss of surface oxygen. As seen in the Ga 3*d* region [Fig. 2(b)], the presence of Ga–O is detected as a shoulder in the photoelectron spectra. The feature is seen to shift toward the bulk Ga peak as a

<sup>&</sup>lt;sup>a)</sup>Electronic mail: chris.hinkle@utdallas.edu

b) Electronic mail: eric.vogel@utdallas.edu

c)Electronic mail: rmwallace@utdallas.edu

FIG. 1. (a) As  $2p_{3/2}$ , (b) Ga  $2p_{3/2}$ , and (c) O *Is* spectra showing marked difference in surface oxygen between NH<sub>4</sub>OH clean, 325 °C anneal, ALD Al<sub>2</sub>O<sub>3</sub> deposition, and atomic hydrogen exposure.

function of Si-flux exposure, suggesting that the Si exposure gradually results in Ga–O–Si bonding over Ga–O–As bonding. The ratio of the Ga–O peak area to the bulk Ga peak area indicates that there is no detectable loss of Ga–O bonds, consistent with a bond conversion process. We note that under the *in situ* deposition techniques employed here, no As–O–Si bonding is detected in contrast to previous reports.<sup>4</sup>

The amount of  $SiO_x$  that arises as the Si is deposited on the differently prepared surfaces as calculated using Si 2p XPS spectra also differs (not shown). On an NH<sub>4</sub>OH treated surface exposed to a Si deposition of  $\sim 1.1$  nm, 40% of the Si 2p signal is from some form of  $SiO_x$  rather than Si–Si bonds. The H-treated surface, with a substantially lower amount of oxygen, has a significantly lower percentage of its Si 2p signal due to an oxide after Si deposition. This  $SiO_x$  layer could be a direct cause of Fermi-level pinning, as reported recently. <sup>16</sup>

The capacitance-voltage (C-V) characteristics of samples with  $Al_2O_3$  deposited directly on the  $NH_4OH$  and hydrogentreated n-type GaAs (100) surfaces show the same amount of accumulation capacitance  $(C_{acc})$  frequency dispersion for both types of surface preparations (not shown). These similarities, despite the different starting surfaces, are probably due to the comparable number of interfacial oxide bonds after dielectric deposition due to the subsequent exposure to oxygen from  $H_2O$  in the ALD cycles. We note that the As–O peak of the  $NH_4OH$  treated surface is reduced below detection limit after ALD deposition [Fig. 1(a)], as seen by previous groups. There is also detectable Ga–O bond forma-

FIG. 2. (a) As 3d XPS results showing As–O removal as a function of Si deposition and (b) Ga 3d XPS results showing bond conversion after Si-flux exposure to the NH<sub>4</sub>OH treated GaAs surface.

tion for the atomic hydrogen–treated sample after  $Al_2O_3$  deposition, in contrast to the H-cleaned surface prior to  $Al_2O_3$  deposition. As a result, As–O and Ga–O species are similar in concentration for these two post-ALD surfaces (not shown).

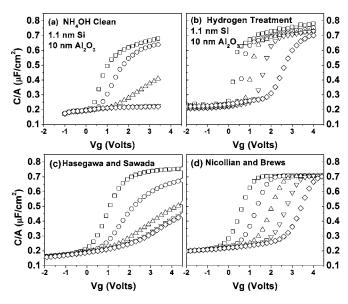

Figure 3 shows the changes in the dispersion observed from a device consisting of a Si interlayer deposited on the prepared GaAs surface followed by Al<sub>2</sub>O<sub>3</sub> deposition. Figure 3(a) shows the C-V response of 1.1 nm e-beam deposited Si with 10 nm Al<sub>2</sub>O<sub>3</sub> on an NH<sub>4</sub>OH cleaned surface. The frequency dispersion is still prevalent suggesting that simply depositing a Si interlayer without further surface treatment will not reduce the dispersion. Figure 3(b) shows the significant reduction in  $C_{\rm acc}$  frequency dispersion for the identical Si and Al<sub>2</sub>O<sub>3</sub> depositions on a H-treated substrate. The shift in the voltage transition region as a function of frequency is a behavior generally attributed to the presence of unpassivated interface states. 19 This occurs when the capacitance due to interface traps is larger than the oxide capacitance. The amount of oxygen at the starting surface appears to be of utmost importance for the reduction of this dispersion. Furthermore, each of the stacks which produced the C-V curves shown has interfaces that show As-O below the detection limit of XPS. Due to the different accumulation capacitance responses, it is unlikely that As-O is the root of the dispersion.

The frequency dispersion of the voltage transition observed in the capacitors with reduced accumulation disper-

FIG. 3. *C-V* curves of (a) NH<sub>4</sub>OH cleaned GaAs surface and (b) atomic H–treated GaAs surface, each with 1.1 nm Si interlayer and 10 nm ALD deposited Al<sub>2</sub>O<sub>3</sub>, and simulated data using the (c) Hasegawa-Sawada model and (d) Nicollian-Brews model. Symbols correspond to different frequencies:  $\Box$ , 100 Hz;  $\bigcirc$ , 1 kHz;  $\triangle$ , 10 kHz;  $\nabla$ , 100 kHz; and  $\Diamond$ , 1 MHz.

sion [Fig. 3(b)] can be modeled using the Nicollian-Brews (NB) interface state model. <sup>19</sup> Figure 3(d) shows a simulation of this model using an interface state density  $(D_{it})$  of approximately  $5 \times 10^{13}$  cm<sup>-2</sup> eV<sup>-1</sup>. The NB model cannot, however, simulate the  $C_{\rm acc}$  dispersion characteristics of Fig. 3(a). Hasegawa and Sawada (HS) proposed a structurally different model to explain the  $C_{\rm acc}$  dispersion phenomenon using a "disordered" GaAs layer at the interface of the crystalline substrate and the dielectric.<sup>20</sup> Following this model, we assume that trap states in the bulk of the dielectric can be occupied by tunneling due to a postulated lower band gap of a disordered dielectric/interface region. Using the same value of  $D_{it}$  used in the NB model as a parameter for the HS model produces the C-V curves shown in Fig. 3(c), exhibiting a behavior reminiscent of the experimental curves [Fig. 3(a)]. The C-V models, therefore, suggest that the interfacial defect density may not be the reason for reduced accumulation capacitance frequency dispersion. These models, while using the same interface state density, produce different C-V characteristics due to the disordered layer in the HS model.

In summary, the starting surface of GaAs must be prepared so that the atomic concentrations of surface As and Ga oxide species are below the XPS detectable limits, less than  $\sim 1$  at. % ( $< 10^{13}$  cm<sup>-2</sup>), to reduce the  $C_{\rm acc}$  frequency dispersion seen in GaAs MOS capacitors. However, while the surface cleans examined do not appear to be sufficient to reduce the dispersion due to oxide formation from subsequent dielectric deposition, Si deposition on a starting surface that

has residual oxide species is not in itself sufficient to reduce the dispersion. These results suggest that an interlayer on an oxide-free surface is required to reduce the dispersion, as shown by a Si interlayer on a hydrogen cleaned surface. We also observe the removal of As–O bonds with a Si-flux exposure, ALD Al<sub>2</sub>O<sub>3</sub> deposition, as well as hydrogen exposure. We also note that As–O bonds are below XPS detectable limits in a number of devices examined here; however, some show reduced dispersion while others do not. This strongly suggests that the As–O bonding is not the primary species responsible for the frequency dispersion of accumulation capacitance.

This work is supported by the MARCO Focus Center on Materials, Structures, and Devices, the NIST, Semiconductor Electronics Division, Science Foundation Ireland, and the Texas Enterprise Fund. The authors thank Professor P. Ye at Purdue for useful discussions.

<sup>1</sup>M. J. Hale, S. I. Yi, J. Z. Sexton, A. C. Kummel, and M. Passlack, J. Chem. Phys. **119**, 6719 (2003).

<sup>2</sup>H. Hasegawa, M. Akazawa, H. Ishii, and K. Matsuzaki, J. Vac. Sci. Technol. B 7, 870 (1989).

<sup>3</sup>J. L. Freeouf, D. A. Buchanan, S. L. Wright, T. N. Jackson, and B. Robinson, Appl. Phys. Lett. **57**, 1919 (1990).

<sup>4</sup>S. Oktyabrsky, V. Tokranov, M. Yakimov, R. Moore, S. Koveshnikov, W. Tsai, F. Zhu, and J. C. Lee, Mater. Sci. Eng., B **135**, 272 (2006).

<sup>5</sup>S. J. Koester, E. W. Kiewra, Y. Sun, D. A. Neumayer, J. A. Ott, M. Copel, D. K. Sadana, D. J. Webb, J. Fompeyrine, J. P. Locquet, C. Marchiori, M. Sousa, and R. Germann, Appl. Phys. Lett. **89**, 042104 (2006).

<sup>6</sup>X. Yuan, H.-C. Lin, and P. Ye, IEEE Trans. Electron Devices **54**, 1811 (2007)

<sup>7</sup>T. Akatsu, A. Plossl, H. Stenzel, and U. Gosele, J. Appl. Phys. **86**, 7146 (1999).

<sup>8</sup>M. Yamada, Y. Ide, and K. Tone, Appl. Surf. Sci. **70-1**, 531 (1993).

<sup>9</sup>P. Sivasubramani, J. Kim, M. J. Kim, B. E. Gnade, and R. M. Wallace, J. Appl. Phys. **101**, 114108 (2007).

<sup>10</sup>N. Braslau, J. Vac. Sci. Technol. **19**, 803 (1981).

<sup>11</sup>G. Landgren, R. Ludeke, Y. Jugnet, J. F. Morar, and F. J. Himpsel, J. Vac. Sci. Technol. B 2, 351 (1984).

<sup>12</sup>M. V. Lebedev, D. Ensling, R. Hunger, T. Mayer, and W. Jaegermann, Appl. Surf. Sci. 229, 226 (2004).

<sup>13</sup>C. Y. Su, I. Lindau, P. R. Keath, P. W. Chye, and W. E. Spicer, J. Vac. Sci. Technol. **17**, 936 (1980).

<sup>14</sup>P. Kruse, J. G. McLean, and A. C. Kummel, J. Chem. Phys. **113**, 9217 (2000).

<sup>15</sup>G. D. Wilk, Y. Wei, H. Edwards, and R. M. Wallace, Appl. Phys. Lett. **70**, 2288 (1997).

<sup>16</sup>D. L. Winn, M. J. Hale, T. J. Grassman, A. C. Kummel, R. Droopad, and M. Passlack, J. Chem. Phys. **126**, 084703 (2007).

<sup>17</sup>M. M. Frank, G. D. Wilk, D. Starodub, T. Gustafsson, E. Garfunkel, Y. J. Chabal, J. Grazul, and D. A. Muller, Appl. Phys. Lett. **86**, 152904 (2005).

<sup>18</sup>M. L. Huang, Y. C. Chang, C. H. Chang, Y. J. Lee, P. Chang, J. Kwo, T. B. Wu, and M. Hong, Appl. Phys. Lett. **87**, 252104 (2005).

<sup>19</sup>E. H. Nicollian and J. R. Brews, MOS Physics and Technology, Wiley, Hoboken, NJ, (1982).

<sup>20</sup>H. Hasegawa and T. Sawada, IEEE Trans. Electron Devices 27, 1055 (1980).