# SYMMETRIC REARRANGEABLE NETWORKS AND ALGORITHMS

<sup>ву</sup> Amitabha Chakrabarty

> THESIS DIRECTED BY: DR. MARTIN COLLIER

# A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

SCHOOL OF ELECTRONIC ENGINEERING DUBLIN CITY UNIVERSITY I hereby certify that this material, which I now submit for assessment on the programme of study leading to the award of Doctor of Philosophy is entirely my own work, that I have exercised reasonable care to ensure that the work is original, and does not to the best of my knowledge breach any law of copyright, and has not been taken from the work of others save and to the extent that such work has been cited and acknowledged within the text of my work.

Signed:

ID number: 57113807

Date: 28/09/2011

# ABSTRACT

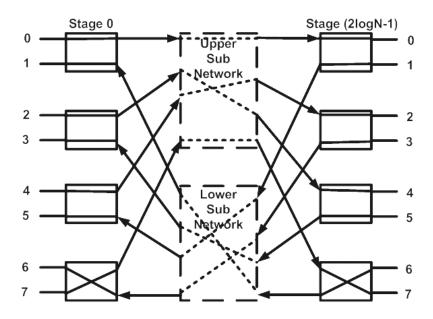

class of symmetric rearrangeable nonblocking networks has been considered in this thesis. A particular focus of this thesis is on Beneš networks built with  $2 \times 2$  switching elements. Symmetric rearrangeable networks built with larger switching elements have also being considered. New applications of these networks are found in the areas of System on Chip (SoC) and Network on Chip (NoC). Deterministic routing algorithms used in NoC applications suffer low scalability and slow execution time. On the other hand, faster algorithms are blocking and thus limit throughput. This will be an acceptable trade-off for many applications where achieving "wire speed" on the on-chip network would require extensive optimisation of the attached devices. In this thesis I designed an algorithm that has much lower blocking probabilities than other suboptimal algorithms but a much faster execution time than deterministic routing algorithms. The suboptimal method uses the looping algorithm in its outermost stages and then in the two distinct subnetworks deeper in the switch uses a fast but suboptimal path search method to find available paths. The worst case time complexity of this new routing method is  $O(N \log N)$  using a single processor, which matches the best known results reported in the literature.

Disruption of the ongoing communications in this class of networks during rearrangements is an open issue. In this thesis I explored a modification of the topology of these networks which gives rise to what is termed as repackable networks. A repackable topology allows rearrangements of paths without intermittently losing connectivity by breaking the existing communication paths momentarily. The repackable network structure proposed in this thesis is efficient in its use of hardware when compared to other proposals in the literature.

As most of the deterministic algorithms designed for Beneš networks implement a permutation of all inputs to find the routing tags for the requested inputoutput pairs, I proposed a new algorithm that can work for partial permutations. If the network load is defined as  $\rho$ , the mean number of active inputs in a partial permutation is,  $\overline{m} = \rho N$ , where N is the network size. This new method is based on mapping the network stages into a set of sub-matrices and then determines the routing tags for each pair of requests by populating the cells of the sub-matrices without creating a blocking state. Overall the serial time complexity of this method is  $O(N \log N)$  and  $O(\overline{m} \log N)$  where all N inputs are active and with  $\overline{m} < N$  active inputs respectively. With minor modification to the serial algorithm this method can be made to work in the parallel domain. The time complexity of this routing algorithm in a parallel machine with N completely connected processors is  $O(\log^2 N)$ . With  $\overline{m}$  active requests the time complexity goes down to  $(\log \overline{m} \log N)$ , which is better than the  $O(\log^2 \overline{m} + \log N)$ , reported in the literature for  $2^{\frac{1}{2}[(\log^2 N - 4\log N)^{\frac{1}{2}} - \log N]} \le \rho \le 1$ . I also designed multistage symmetric rearrangeable networks using larger switching elements and implement a new routing algorithm for these classes of networks.

The network topology and routing algorithms presented in this thesis should allow large scale networks of modest cost, with low setup times and moderate blocking rates, to be constructed. Such switching networks will be required to meet the bandwidth requirements of future communication networks.

# ACKNOWLEDGEMENTS

I would like to express my thanks to everyone who helped me throughout my PhD journey. But above everyone, my sincere gratitude goes to my supervisor, Dr. Martin Collier, without whom this journey would not have been possible. Thanks go to him for providing me with the right mix of freedom and guidance throughout my period in DCU.

I wish to thank Prof. Barry McMullin, Prof. Noel O'Connor, Dr. Conor McArdle and Dr. Eugen Schenfeld for serving on my doctoral committee and for their comments and suggestions.

Thanks go to all the faculty members of School of Electronic Engineering, especially Dr. Noel Murphy for his kindness towards me. Thanks should also go to the members of the Switching and Systems Laboratory for making my stay at the lab such a pleasant experience.

I would like to thank all my friends in Dublin for being there with me always. Thanks go to my elder brother, Dr. Debasish Chakraborty and his family for their continuous support throughout. Lastly and most importantly thanks go to my parents for allowing me to study outside Bangladesh for my degree and to stay away from them for so long.

# LIST OF PUBLICATIONS

- A. Chakrabarty, M. Collier, Symmetric Rearrangeable Networks: A New Routing Algorithm and Emerging Applications, International Journal of Electronics and Communications (Elsevier) (Submitted).

- A. Chakrabarty, M. Collier, Optimum Cost Multistage Symmetric Repackable Networks, International Journal of Grid and High Performance Computing (IJGHPC), IGI Global. (In press)

- A. Chakrabarty, M. Collier, And S. Mukhopadhyay, Adaptive Routing Strategy for Large Scale Rearrangeable Symmetric Networks, International Journal of Grid and High Performance Computing (IJGHPC), IGI Global, 2010.

- A. Chakrabarty, M. Collier, *Efficient Implementation of Symmetric Multistage Repackable Networks*. Proceeding of the International Conference on Computational Intelligence and Communication Networks (CICN-2010). IEEE Computer Society Press, 2010.

- A. Chakrabarty, M. Collier, And S. Mukhopadhyay, *Symmetric Rearrange-able Networks: Algorithms and Rearrangement Limits*. Proceeding of the 7th International Conference on Information Technology : New Generations. IEEE Computer Society Press. Las Vegas, Nevada, USA, April 12-14, 2010.

- A. Chakrabarty, M. Collier, And S. Mukhopadhyay, *Matrix-Based Routing Algorithm for Benes Networks*. Proceeding of the International Conference on Future Computational Technologies and Applications (FUTURE COM-PUTING 2009). IEEE Computer Society Press. Athens, Greece, November 15-20, 2009.

- A. Chakrabarty, M. Collier, And S. Mukhopadhyay, *Dynamic Path Selection Algorithm for Benes Networks*. Proceeding of the IEEE International conference on Computational Intelligence, Communication Systems and Networks (CICSyN2009). IEEE Computer Society Press, 2009.

# CONTENTS

| <b>List of Publications</b> |

|-----------------------------|

|-----------------------------|

| Li | st of   | Figures | 3                                | iv  |

|----|---------|---------|----------------------------------|-----|

| Li | st of ' | Tables  |                                  | vii |

| 1  | Intr    | oductio | on                               | 1   |

|    | 1.1     | Motiv   | ration                           | 2   |

|    | 1.2     | Thesis  | s Contribution                   | 4   |

|    |         | 1.2.1   | Problem Statement                | 4   |

|    |         | 1.2.2   | Solutions                        | 4   |

|    |         | 1.2.3   | Methodology                      | 6   |

|    | 1.3     | Summ    | nary of Contributions            | 6   |

|    | 1.4     | Outlir  | ne of the Thesis                 | 8   |

| 2  | Swi     | tching  | Techniques                       | 10  |

|    | 2.1     | Multi   | plexing                          | 10  |

|    |         | 2.1.1   | Frequency Division Multiplexing  |     |

|    |         | 2.1.2   | Time Division Multiplexing       | 12  |

|    |         | 2.1.3   | Wavelength Division Multiplexing | 12  |

|    | 2.2     | Switcl  | hing                             | 13  |

|    |         | 2.2.1   | Circuit Switching                | 14  |

|    |         | 2.2.2   | Packet Switching                 | 15  |

|    |         | 2.2.3   | Multi-Rate Circuit Switching     | 17  |

|    |         | 2.2.4   | Virtual Cut-Through Switching    |     |

|    |         | 2.2.5   | Wormhole Switching               | 19  |

|   |                                                                                                                                                                         | 2.2.6 Optical Burst Switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 19                                                                                                                                                                                 |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 2.3                                                                                                                                                                     | Communication Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20                                                                                                                                                                                 |

|   |                                                                                                                                                                         | 2.3.1 Interconnection Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21                                                                                                                                                                                 |

|   |                                                                                                                                                                         | 2.3.2 Networks Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 24                                                                                                                                                                                 |

|   | 2.4                                                                                                                                                                     | Bidirectional Multistage Interconnection Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 29                                                                                                                                                                                 |

|   | 2.5                                                                                                                                                                     | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31                                                                                                                                                                                 |

| 3 | Rea                                                                                                                                                                     | rrangeable Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32                                                                                                                                                                                 |

|   | 3.1                                                                                                                                                                     | Clos Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32                                                                                                                                                                                 |

|   | 3.2                                                                                                                                                                     | Beneš Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 37                                                                                                                                                                                 |

|   | 3.3                                                                                                                                                                     | Preliminaries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 39                                                                                                                                                                                 |

|   | 3.4                                                                                                                                                                     | Blocking Probabilities: The Lee and Jacobaeus Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 42                                                                                                                                                                                 |

|   | 3.5                                                                                                                                                                     | Beneš based Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 46                                                                                                                                                                                 |

|   | 3.6                                                                                                                                                                     | Overviews on Beneš networks Routing Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 51                                                                                                                                                                                 |

|   | 3.7                                                                                                                                                                     | Application Domain of Beneš Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 58                                                                                                                                                                                 |

|   |                                                                                                                                                                         | 3.7.1 On Chip Communication Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 59                                                                                                                                                                                 |

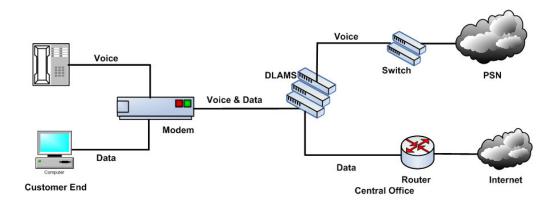

|   |                                                                                                                                                                         | 3.7.2 Digital Subscriber Loop Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 61                                                                                                                                                                                 |

|   |                                                                                                                                                                         | 3.7.3 Optical Domain Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 63                                                                                                                                                                                 |

|   | 3.8                                                                                                                                                                     | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 64                                                                                                                                                                                 |

|   |                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                    |

| 4 | Sym                                                                                                                                                                     | nmetric Multistage Repackable Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 66                                                                                                                                                                                 |

| 4 | <b>Syn</b><br>4.1                                                                                                                                                       | Imetric Multistage Repackable Networks         Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>66</b><br>66                                                                                                                                                                    |

| 4 | •                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                    |

| 4 | 4.1                                                                                                                                                                     | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 66                                                                                                                                                                                 |

| 4 | 4.1<br>4.2                                                                                                                                                              | Introduction    Repackable Networks Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 66<br>67                                                                                                                                                                           |

| 4 | 4.1<br>4.2<br>4.3                                                                                                                                                       | IntroductionRepackable Networks OverviewPreliminariesGeneral Rearrangement Scenario                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 66<br>67<br>68                                                                                                                                                                     |

| 4 | 4.1<br>4.2<br>4.3<br>4.4                                                                                                                                                | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 66<br>67<br>68<br>70                                                                                                                                                               |

| 4 | 4.1<br>4.2<br>4.3<br>4.4                                                                                                                                                | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 66<br>67<br>68<br>70<br>71                                                                                                                                                         |

| 4 | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> </ul>                                                                                             | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 66<br>67<br>68<br>70<br>71<br>72                                                                                                                                                   |

| 4 | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ul>                                                                                | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 66<br>67<br>68<br>70<br>71<br>72<br>77                                                                                                                                             |

| 4 | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8                                                                                                                    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 66<br>67<br>68<br>70<br>71<br>72<br>77<br>81                                                                                                                                       |

|   | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8                                                                                                                    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 66<br>67<br>68<br>70<br>71<br>72<br>77<br>81<br>83                                                                                                                                 |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>Hyte</li> </ul>                                        | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ul> <li>66</li> <li>67</li> <li>68</li> <li>70</li> <li>71</li> <li>72</li> <li>77</li> <li>81</li> <li>83</li> <li>85</li> </ul>                                                 |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>Hyte</li> <li>5.1</li> </ul>                           | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ul> <li>66</li> <li>67</li> <li>68</li> <li>70</li> <li>71</li> <li>72</li> <li>77</li> <li>81</li> <li>83</li> <li>85</li> <li>85</li> </ul>                                     |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>Hyte</li> <li>5.1</li> </ul>                           | Introduction       Repackable Networks Overview         Repackable Networks Overview       Preliminaries         General Rearrangement Scenario       General Rearrangement Scenario         Principle of Repackable Networks       Principle of Repackable Networks         4.5.1       Network Architecture         Crosspoint Requirements       Preliminaries         Hardware Structure of the Bypass links       Summary         Orid Routing Algorithm       Preliminaries         A Formal Description of the Looping Algorithm       Summary | <ul> <li>66</li> <li>67</li> <li>68</li> <li>70</li> <li>71</li> <li>72</li> <li>77</li> <li>81</li> <li>83</li> <li>85</li> <li>85</li> <li>88</li> </ul>                         |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>Hyth</li> <li>5.1</li> <li>5.2</li> </ul>              | Introduction       Repackable Networks Overview         Repackable Networks Overview       Preliminaries         General Rearrangement Scenario       Principle of Repackable Networks         4.5.1       Network Architecture         Crosspoint Requirements       Preliminaries         Hardware Structure of the Bypass links       Preliminaries         Summary       Preliminaries         A Formal Description of the Looping Algorithm       52.1                                                                                           | <ul> <li>66</li> <li>67</li> <li>68</li> <li>70</li> <li>71</li> <li>72</li> <li>77</li> <li>81</li> <li>83</li> <li>85</li> <li>88</li> <li>89</li> </ul>                         |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>Hyte</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> </ul> | Introduction       Repackable Networks Overview         Preliminaries       Preliminaries         General Rearrangement Scenario       Principle of Repackable Networks         4.5.1       Network Architecture         Crosspoint Requirements       Preliminaries         Hardware Structure of the Bypass links       Preliminaries         Summary       Preliminaries         A Formal Description of the Looping Algorithm       S2.1         Example       Random Routing                                                                     | <ul> <li>66</li> <li>67</li> <li>68</li> <li>70</li> <li>71</li> <li>72</li> <li>77</li> <li>81</li> <li>83</li> <li>85</li> <li>85</li> <li>88</li> <li>89</li> <li>90</li> </ul> |

|    |       | 5.4.3 Example                                                               | 100 |

|----|-------|-----------------------------------------------------------------------------|-----|

|    | 5.5   | Simulation Results                                                          | 101 |

|    | 5.6   | Hybrid Routing                                                              | 102 |

|    | 5.7   | Simulation Results                                                          | 104 |

|    | 5.8   | Time Complexity Analysis                                                    | 111 |

|    | 5.9   | Summary                                                                     | 113 |

| 6  | Mat   | rix Based Routing Algorithm                                                 | 116 |

|    | 6.1   | Introduction                                                                | 116 |

|    | 6.2   | Conceptual Basis of the Algorithm                                           | 118 |

|    |       | 6.2.1 Preliminaries                                                         | 119 |

|    | 6.3   | Symmetric Rearrangeable Networks Routing                                    | 122 |

|    |       | 6.3.1 Basic Routing Algorithm                                               | 122 |

|    |       | 6.3.2 Example                                                               | 123 |

|    | 6.4   | Simulation Results                                                          | 125 |

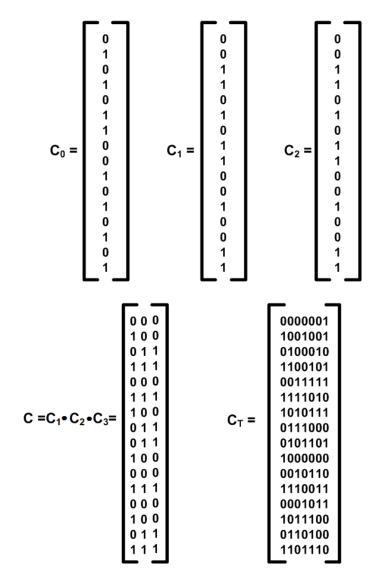

|    |       | 6.4.1 The Routing Tag and Its Validity                                      | 127 |

|    |       | 6.4.2 Example                                                               | 128 |

|    |       | 6.4.3 Reconfiguration Cost                                                  | 130 |

|    | 6.5   | Complexity Analysis                                                         | 132 |

|    | 6.6   | Routing in Optical Domain                                                   | 136 |

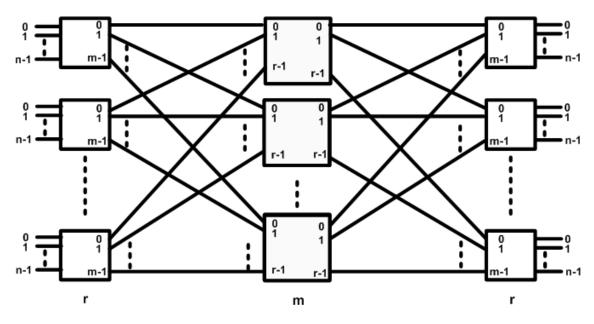

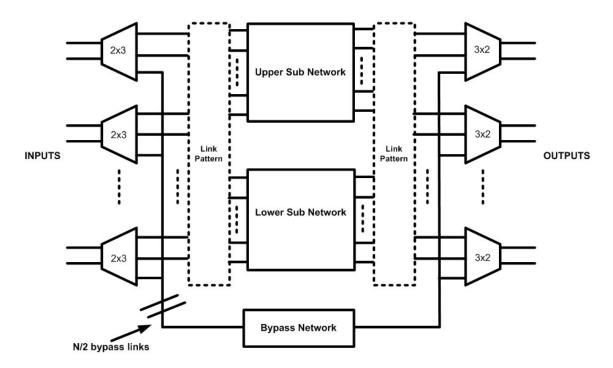

|    | 6.7   | Networks with Large Switching Elements                                      | 140 |

|    |       | 6.7.1 Reducing Network Depth                                                | 140 |

|    | 6.8   | Networks with $3 \times 3$ Switching Elements $\ldots \ldots \ldots \ldots$ | 143 |

|    | 6.9   | Routing Algorithm                                                           | 146 |

|    | 6.10  | Simulation Results                                                          | 148 |

|    | 6.11  | Summary                                                                     | 148 |

| 7  | Con   | clusion and Future Work                                                     | 152 |

|    | 7.1   | Contributions                                                               | 152 |

|    | 7.2   | Future Work                                                                 | 154 |

| Bi | bliog | raphy                                                                       | 156 |

# LIST OF FIGURES

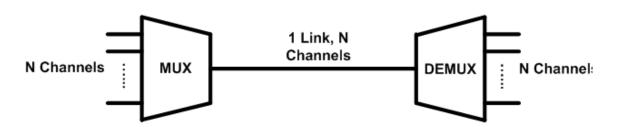

| 2.1  | General multiplexing technique.                                 | 11    |

|------|-----------------------------------------------------------------|-------|

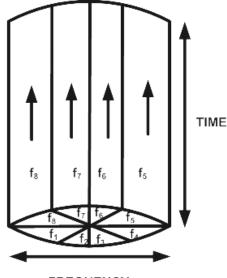

| 2.2  | Frequency division multiplexing                                 | 11    |

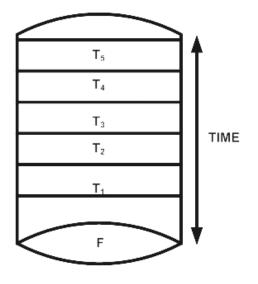

| 2.3  | Time division multiplexing.                                     | 12    |

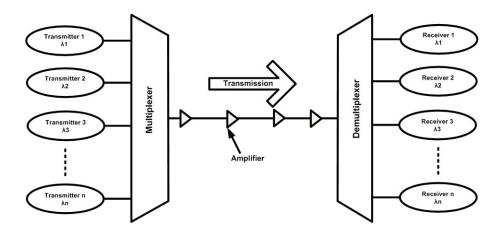

| 2.4  | (Dense)Wavelength division multiplexing                         | 13    |

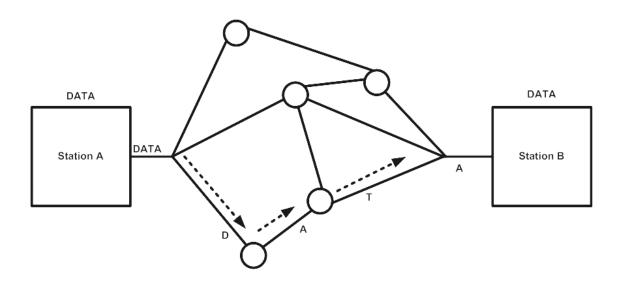

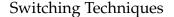

| 2.5  | Circuit switching.                                              | 15    |

| 2.6  | Space division switching.                                       | 16    |

| 2.7  | Packet switching.                                               | 17    |

| 2.8  | Virtual circuit routing.                                        | 17    |

| 2.9  | Datagram routing.                                               | 18    |

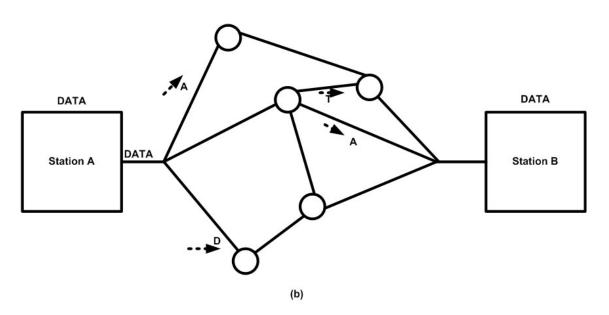

| 2.10 | Communication with and without switching system                 | 20    |

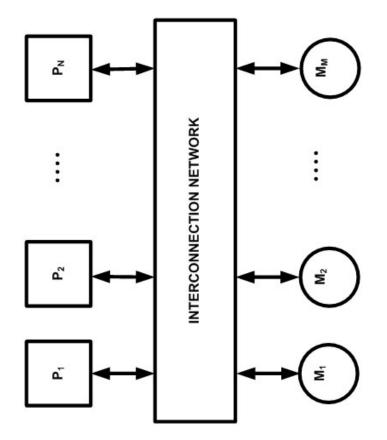

| 2.11 | Processor memory communication using an interconnection network | x. 22 |

| 2.12 | dedicated-path networks.                                        | 23    |

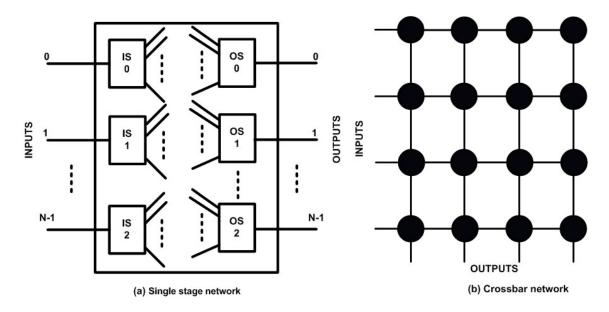

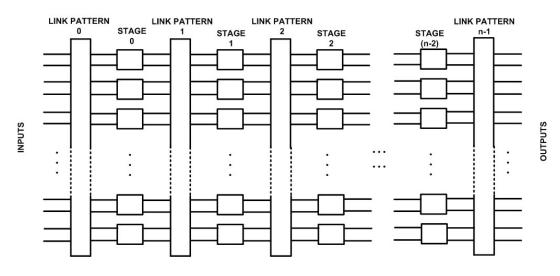

| 2.13 | Single stage and multi stage networks                           | 25    |

| 2.14 | General view of a self routing network.                         | 25    |

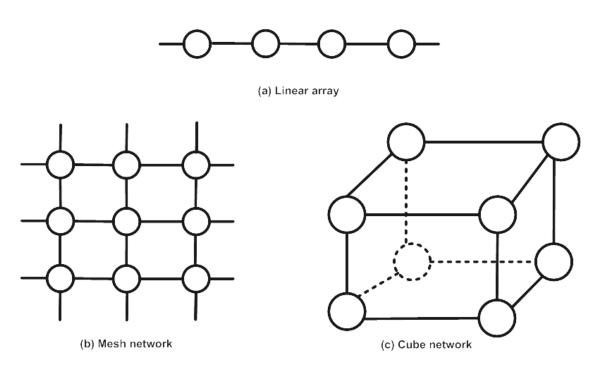

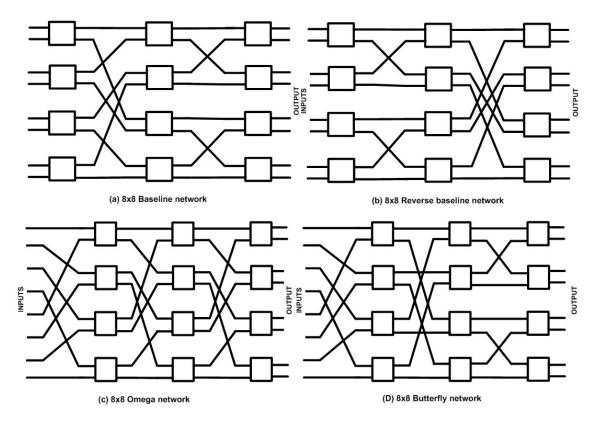

|      | Common networks                                                 | 27    |

| 2.16 | Bidirectional butterfly network                                 | 30    |

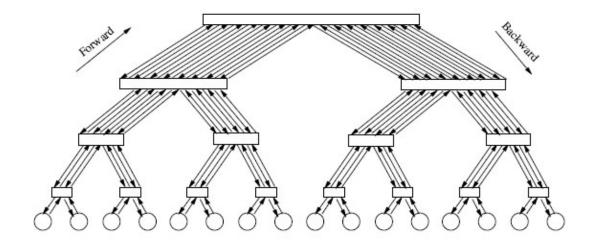

| 2.17 | Fat tree with 16 nodes                                          | 31    |

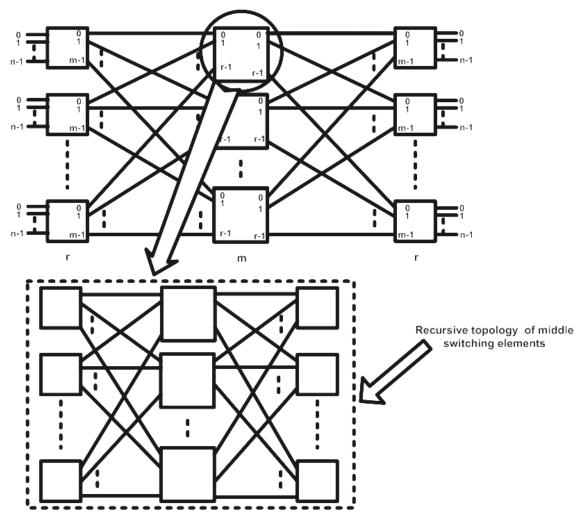

| 3.1  | Clos network.                                                   | 33    |

| 3.2  | Recursive Clos network.                                         | 37    |

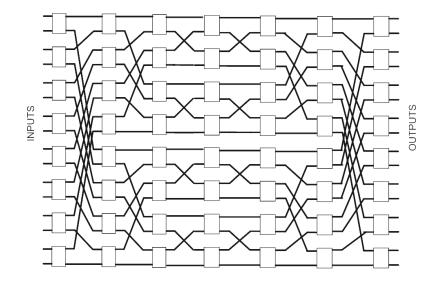

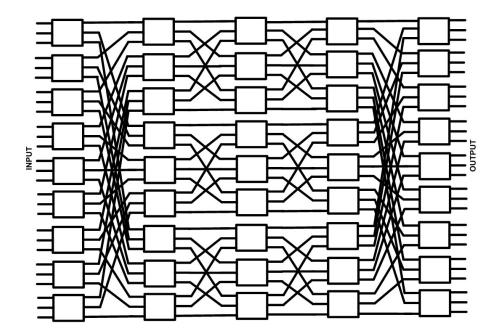

| 3.3  | A $16 \times 16$ Beneš network                                  | 38    |

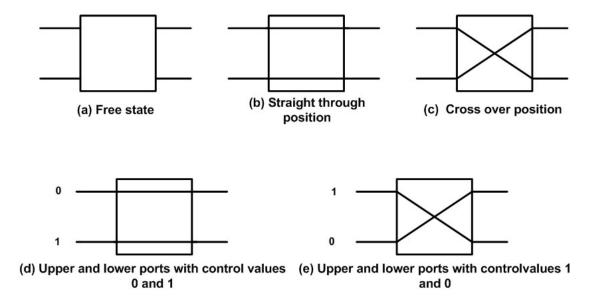

| 3.4  | Possible settings for switching elements.                       | 40    |

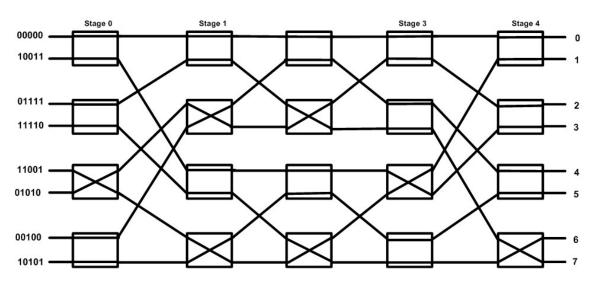

| 3.5  | Routing using the generated conflict free routing tags.         | 42    |

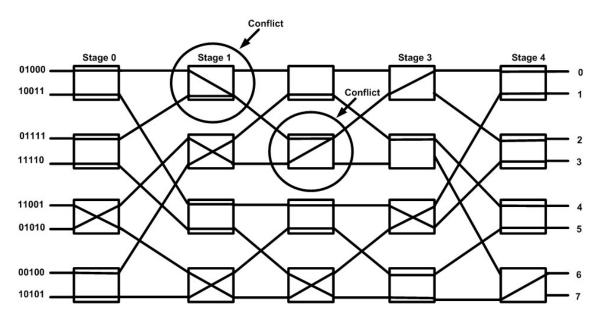

| 3.6  | Conflicting state inside the switch.                            | 43    |

| 3.7  | $N \times N$ Cantor network.                                    | 47    |

| 3.8  | $16 \times 16$ K-Beneš Network                                  | 48    |

|      |                                                                 |       |

| 3.9  | Modification to the inner stage networks                                             | 51    |

|------|--------------------------------------------------------------------------------------|-------|

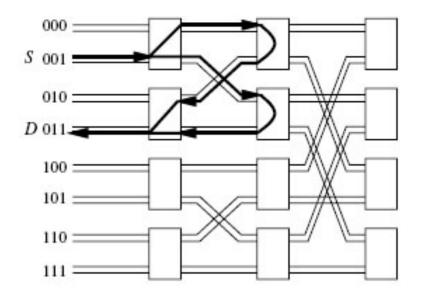

|      | Path setup using looping algorithm.                                                  | 53    |

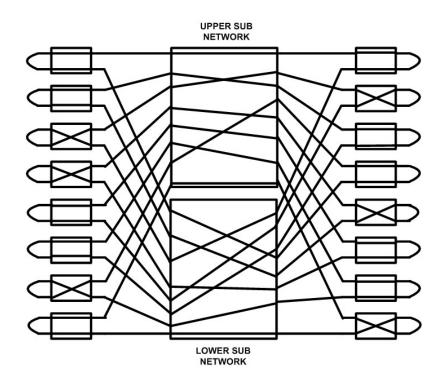

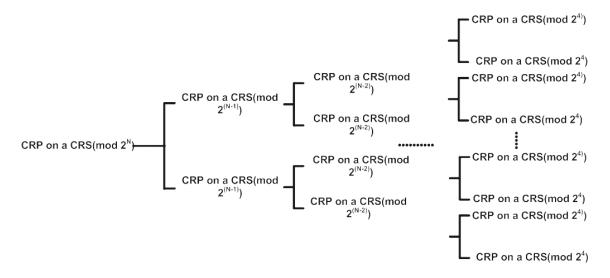

| 3.11 | A full binary tree of CRP's                                                          | 56    |

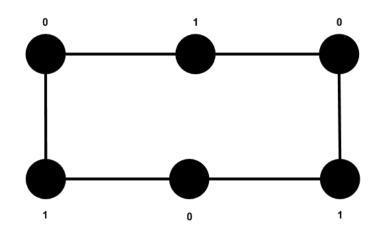

| 3.12 | 2 - Colored connected graph.                                                         | 58    |

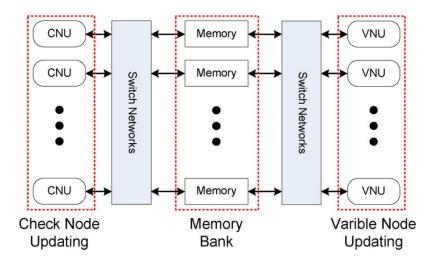

| 3.13 | Architecture of partial parallel LDPC decoder. [1]                                   | 62    |

| 3.14 | Typical DSL configuration.                                                           | 63    |

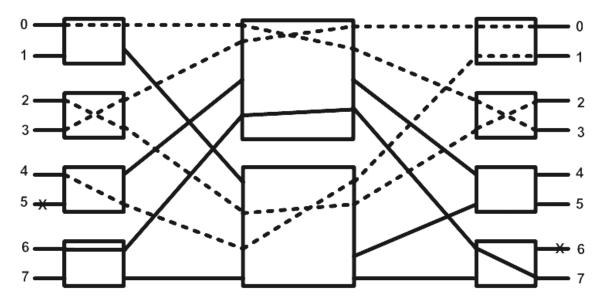

| 4.1  | A network having a chain with length 4                                               | 69    |

| 4.2  | Two isolated links from inputs 6 and 7                                               | 70    |

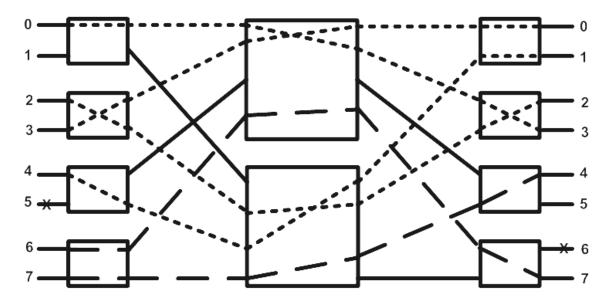

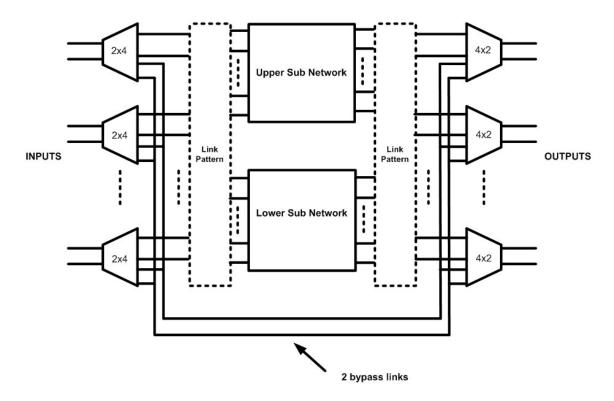

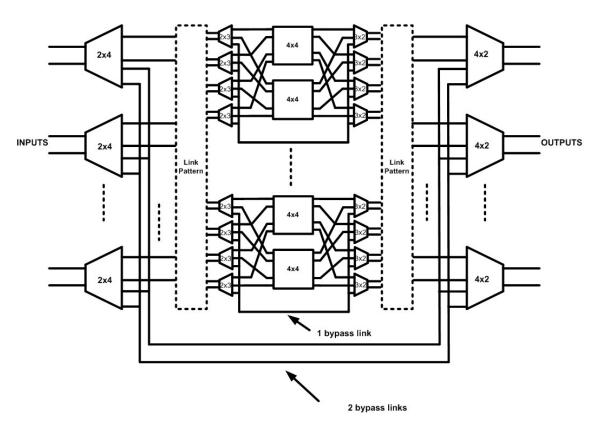

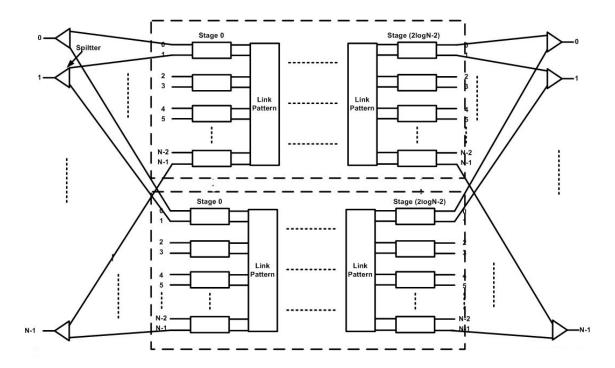

| 4.3  | Symmetric repackable network for simultaneous reswitching                            | 73    |

| 4.4  | Repackable network with 2 bypass links                                               | 73    |

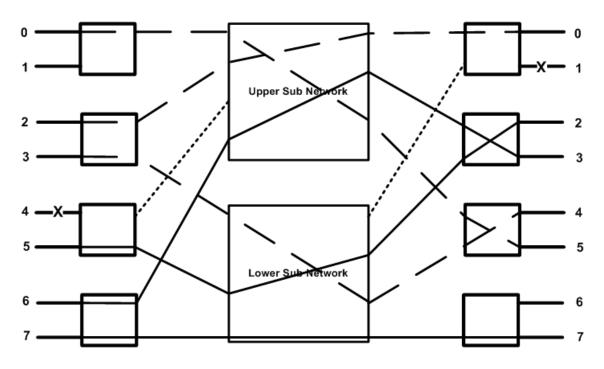

| 4.5  | Blocking state in the network for request $4 \rightarrow 1$                          | 74    |

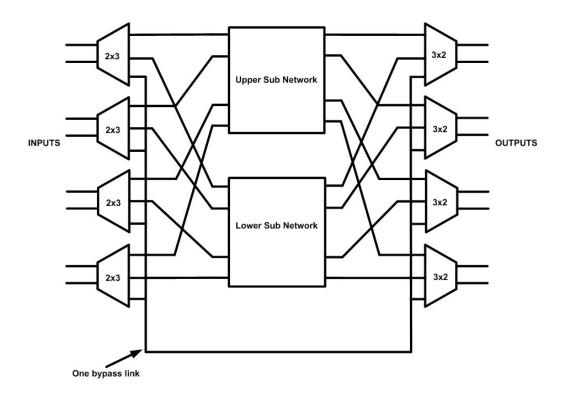

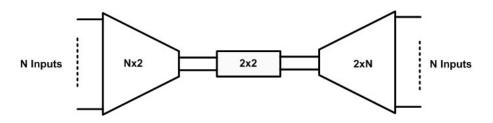

| 4.6  | Repackable network with one bypass link.                                             | 77    |

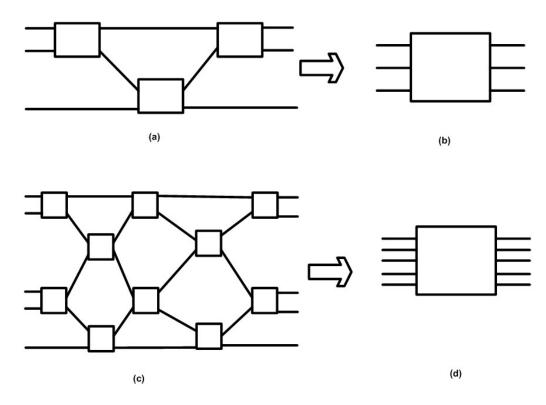

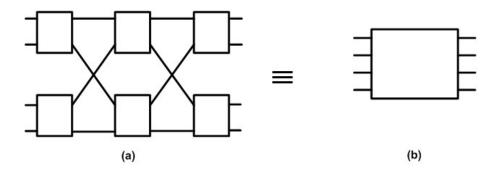

| 4.7  | (a). $4 \times 4$ rearrangeable network. (b). $4 \times 4$ crossbar                  | 79    |

| 4.8  | $16 \times 16$ Beneš network with $4 \times 4$ crossbar in the middle stage $\ldots$ | 79    |

| 4.9  | Mixed bypass links repackable network                                                | 81    |

| 4.10 | Logical representation of bypass links                                               | 81    |

| 4.11 | Hardware structure of 2 bypass links.                                                | 82    |

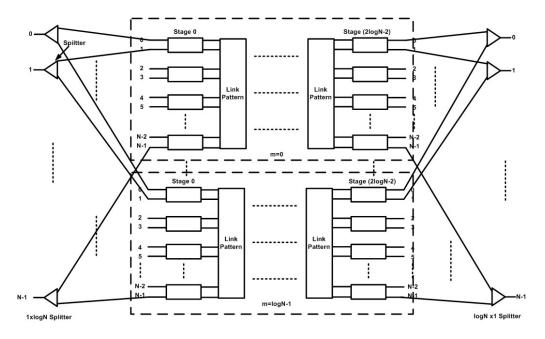

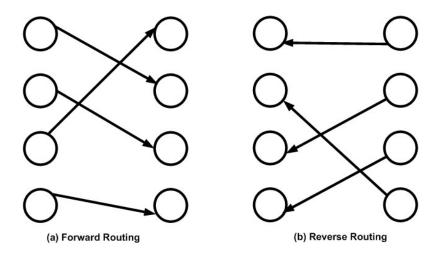

| 5.1  | Forward and reverse routing                                                          | 86    |

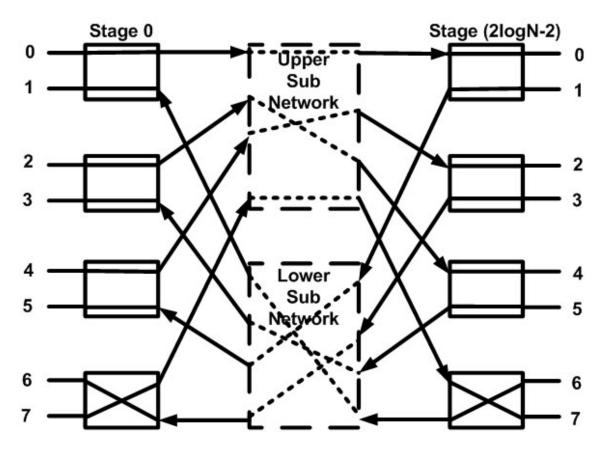

| 5.2  | Switching element settings in stage 0 and $(2log N - 2)$                             | 92    |

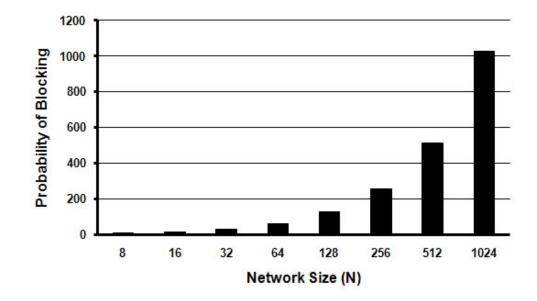

| 5.3  | Blocking probability for random routing                                              | 93    |

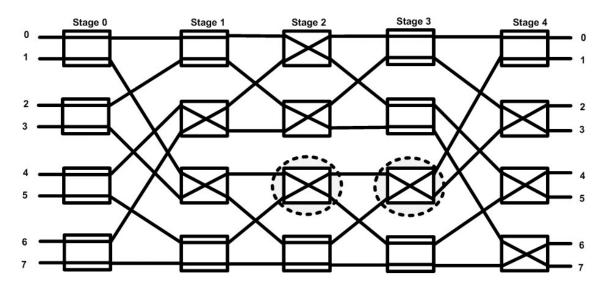

| 5.4  | Network setup using adaptive method for $P_{(0:7)} = (5\ 1\ 7\ 4\ 3\ 2\ 0\ 6)$ .     | 101   |

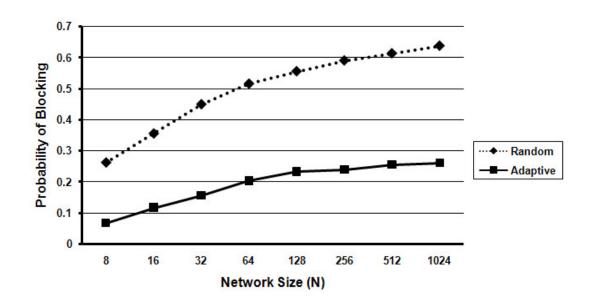

| 5.5  | Probability of blocking using random and adaptive routing                            | 102   |

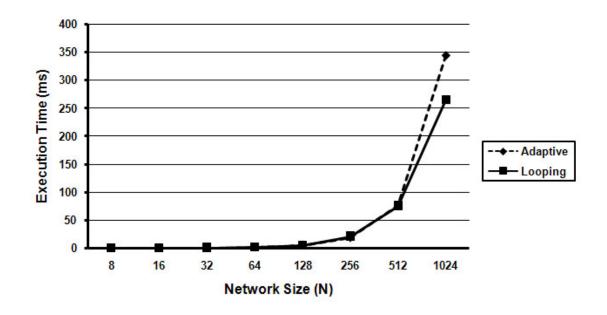

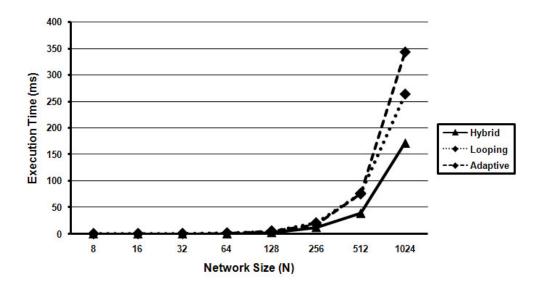

| 5.6  | Execution time for adaptive and the looping algorithm                                | 103   |

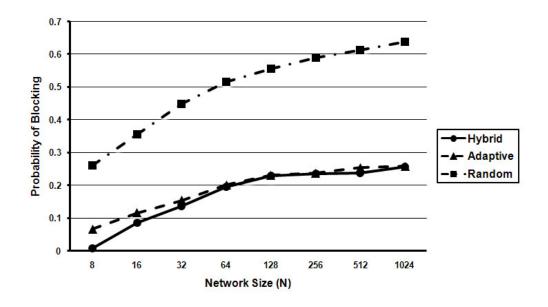

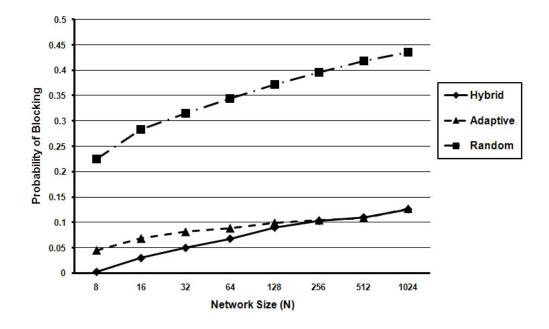

| 5.7  | Performance of three different methods for full input occupancy.                     | 105   |

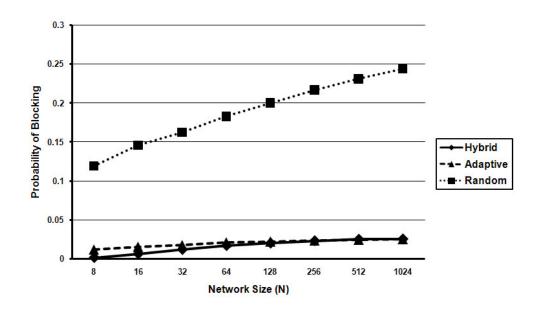

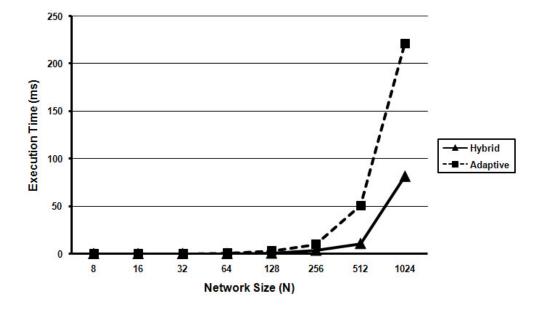

| 5.8  | 50% input occupancy graphs for three methods                                         | 105   |

| 5.9  | 75% input occupancy graph for three methods                                          | 106   |

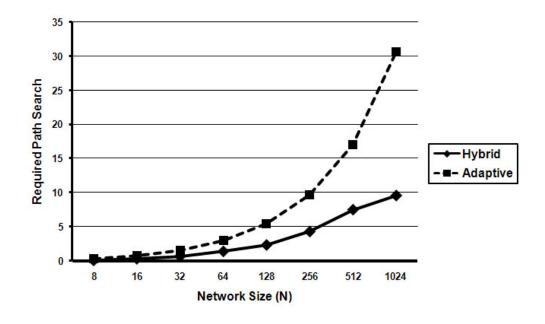

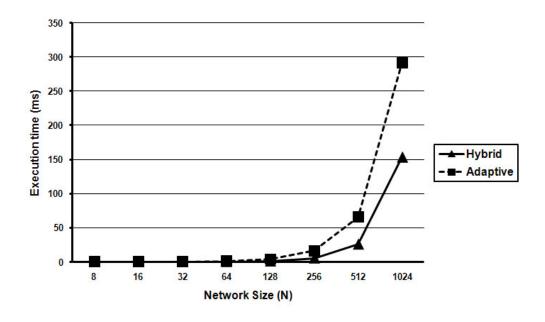

| 5.10 | Path search graph for a full occupancy network                                       | 106   |

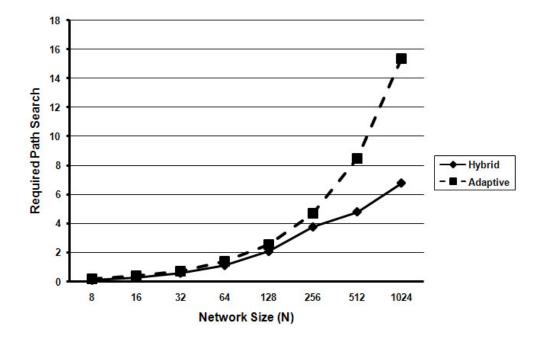

| 5.11 | Path search graph for a $50\%$ input occupancy network                               | 107   |

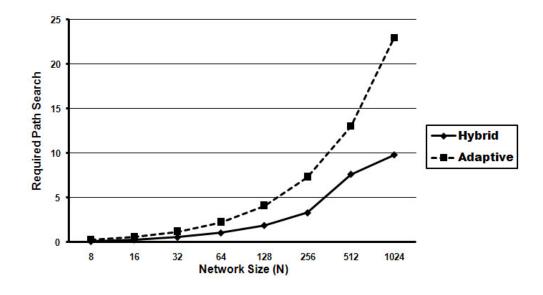

| 5.12 | Path search graph for a $75\%$ input occupancy network                               | 107   |

| 5.13 | Execution time for full occupancy network                                            | 108   |

| 5.14 | Execution time for a $50\%$ input occupancy network                                  | 109   |

| 5.15 | Execution time for a $75\%$ input occupancy network                                  | 109   |

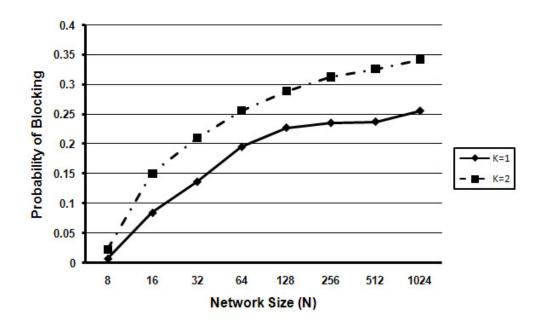

| 5.16 | Probability of blocking for hybrid routing with $k = 1$ and $k = 2$                  | 110   |

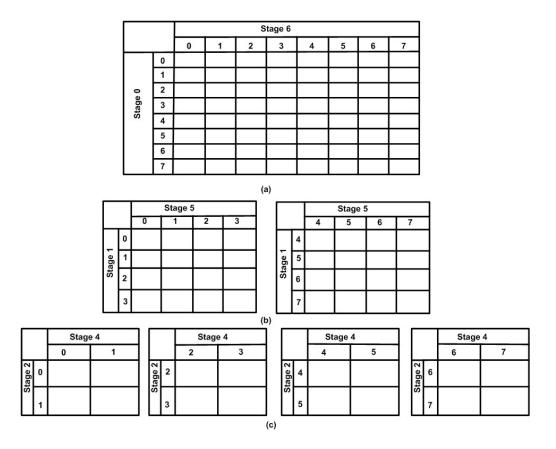

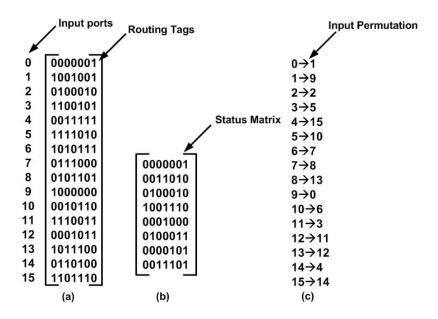

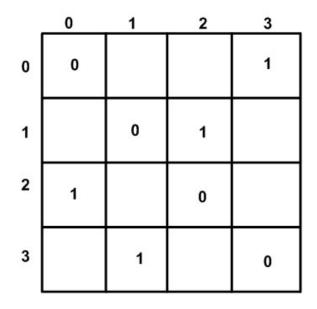

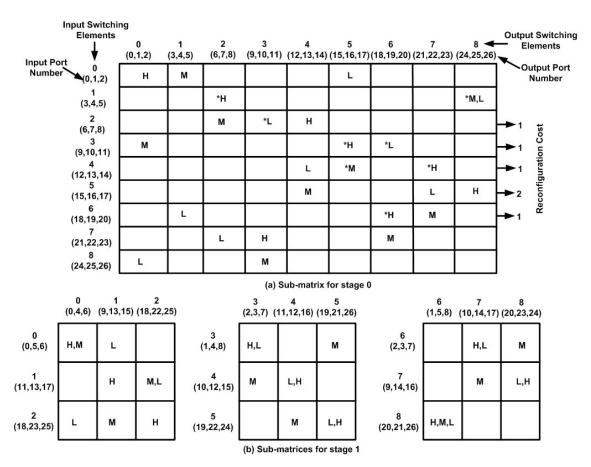

| 6.1  | Sub-matrices format for a $16 \times 16$ Beneš Network                               | 120   |

| 6.2  | One circuit with length 11, where gray boxes represents NULL value                   | e.121 |

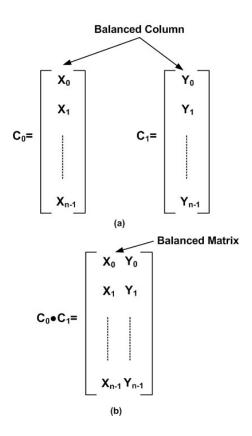

| 6.3  | (a) Balanced Columns. (b) Balanced Matrix                                            | 123   |

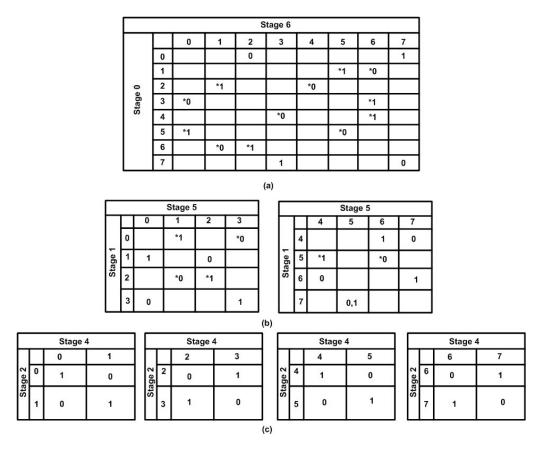

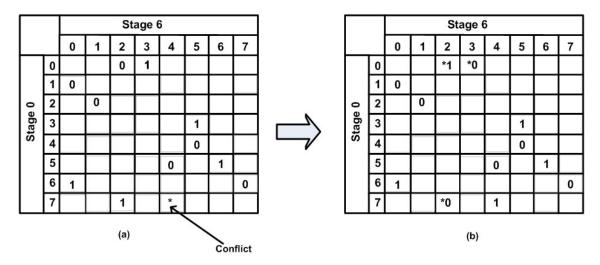

| 6.4  | Sub-matrices status after execution of the algorithm                                                 |

|------|------------------------------------------------------------------------------------------------------|

| 6.5  | Balanced matrices                                                                                    |

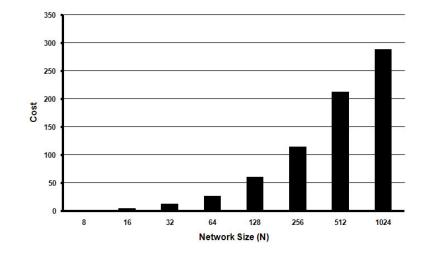

| 6.6  | Routing tags and status matrix for a given permutation                                               |

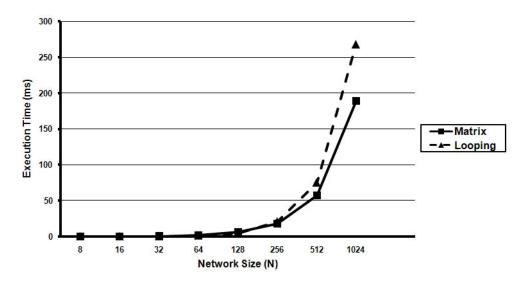

| 6.7  | Reconfiguration cost                                                                                 |

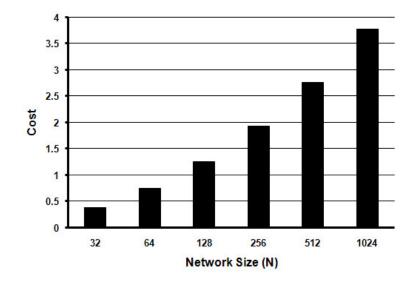

| 6.8  | Execution time for Looping and Matrix based algorithm 131                                            |

| 6.9  | Reconfiguration cost per input for different sizes of network 132                                    |

| 6.10 | Matrix status for permutation $P_{0:15} = (5\ 7\ 1\ x\ 2\ x\ 13\ 10\ x\ 11\ 9\ 12\ 15\ 0\ 4\ 8)$ 133 |

| 6.11 | Routing tag matrix for stage 0                                                                       |

| 6.12 | Space dilated Optical Beneš network                                                                  |

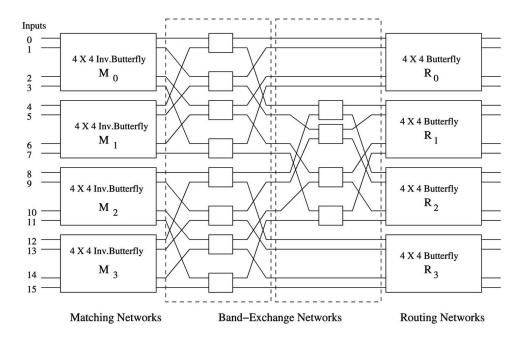

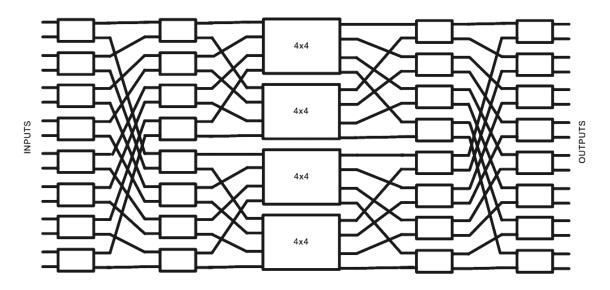

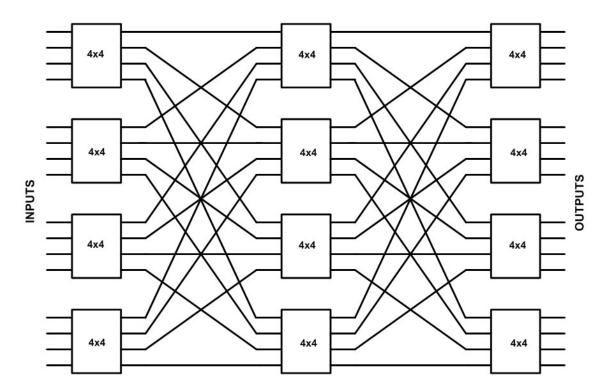

| 6.13 | A $16 \times 16$ symmetric network built with $4 \times 4$ switching elements . 141                  |

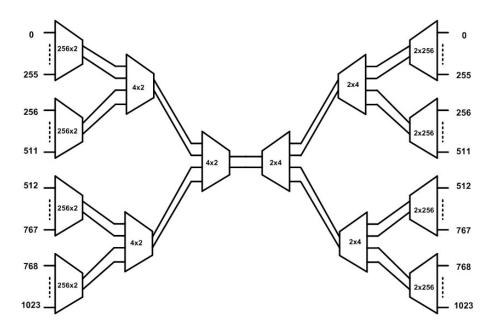

| 6.14 | A $27 \times 27$ symmetric network build with $3 \times 3$ switching elements 144                    |

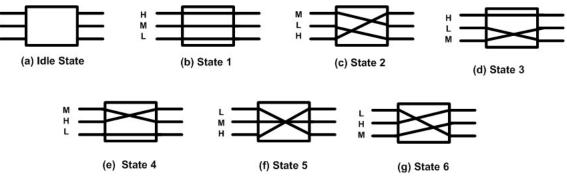

| 6.15 | Different states of a $3 \times 3$ switching elements $\ldots \ldots \ldots \ldots \ldots 145$       |

| 6.16 | Execution of algorithm                                                                               |

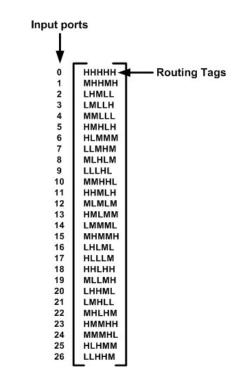

| 6.17 | The Routing tags obtained for the permutation $P_{0:26}$                                             |

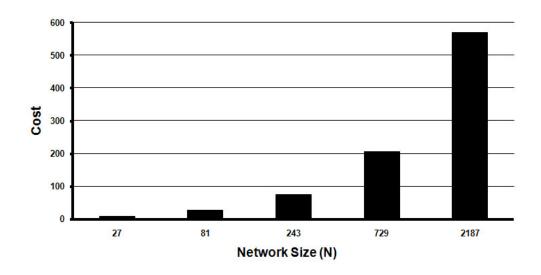

| 6.18 | Maximum reconfiguration cost for different sizes of network 149                                      |

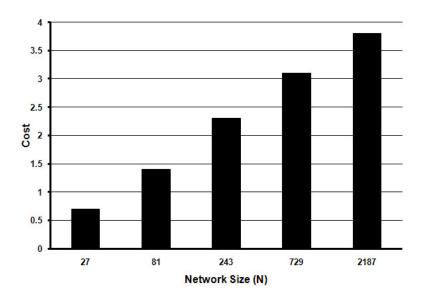

| 6.19 | Reconfiguration cost per input for different size of networks 149                                    |

# LIST OF TABLES

| 3.1 | Number of crosspoints for crossbar and 3-stage Clos networks               | 34   |

|-----|----------------------------------------------------------------------------|------|

| 3.2 | Summary of Routing Algorithm Complexities                                  | 60   |

| 3.3 | Complexity of different switching fabrics.                                 | 62   |

| 4.1 | Path map for input-output request.                                         | 71   |

| 4.2 | Path map for input-output requests after reswitching                       | 75   |

| 4.3 | Worst case chain length.                                                   | 76   |

| 4.4 | Crosspoints requirement per input for various size of networks             | 83   |

| 6.1 | Comparison of network depths                                               | 142  |

| 6.2 | Crosspoint count for networks with heterogenous switching element          | s143 |

| 6.3 | Crosspoint for networks using $2 \times 2$ switching elements              | 144  |

| 6.4 | Crosspoint count for networks for $3 \times 3$ switching elements $\ldots$ | 145  |

|     |                                                                            |      |

# LIST OF ALGORITHMS

| 1  | : Algorithm Looping                                                                                                           | 89 |

|----|-------------------------------------------------------------------------------------------------------------------------------|----|

| 2  | : UPDATEPERM $(k)$                                                                                                            | 90 |

| 3  | : $\operatorname{ROUTELOOP}(i, k)$                                                                                            | 91 |

| 4  | : Algorithm Adaptive                                                                                                          | 94 |

| 5  | : FORWARD $(i_k, k)$                                                                                                          | 95 |

| 6  | : BITFRD $(i_k, M(i_k))$                                                                                                      | 96 |

| 7  | $: CONFLICTFRD(i_k) \ldots \ldots$ | 97 |

| 8  | : REVERSE $(O_k, k)$                                                                                                          | 98 |

| 9  | : BITREV $(O_k, M(O_k))$                                                                                                      | 99 |

| 10 | : CONFLICTREV $(O_k, k)$                                                                                                      | 00 |

| 11 | : Algorithm Matrix                                                                                                            | 24 |

| 12 | : ROUTING(i)                                                                                                                  | 24 |

| 13 | : CONFLICTROW( $R', C', B_1, i$ )                                                                                             | 26 |

| 14 | : CONFLICTCOLUMN $(R', C', B_2, i)$                                                                                           | 26 |

# **CHAPTER 1**

# INTRODUCTION

The telecommunication standardization sector of ITU (International Telecommunications Union) defines switching as:

"The establishing, on demand, of an individual connection from a desired input to a desired output within a set of inputs and outputs for as long as is required for the transfer of information".

In its early days switching only involved connecting two communicating parties for telephone service. In recent days switching devices are required to handle much more than voice service. Switches must support high speed data and video communication, LAN to LAN communication, large file transfers and cable TV transmissions. A recent report<sup>1</sup> shows that file sharing consumes 25% of the global internet traffic and video (such as streaming video, Flash, and Internet TV) consumes 26% percent. Over one-third of the top 50 sites by volume are video sites. VoIP services such as Skype traffic grew by over  $40\%^2$ . It is estimated that around 70% or more of broadband bandwidth is consumed by downloads

<sup>&</sup>lt;sup>1</sup>http://gigaom.com/2010/10/26/why-broadband-changes-everything/

<sup>&</sup>lt;sup>2</sup>http://technews.tmcnet.com/voip-software/topics/voip-software/articles/132217-skype-grows-global-traffic-40-percent-2010.htm

of music, games, video, and other content<sup>3</sup>.Considering the increasing demand it is not possible to connect all the users with direct communication links as the cost grows exponentially. Hence various switch and switching mechanisms are in place to reduce the communication cost and increase the reliability of communication.

## 1.1 Motivation

Switching network architectures in use in recent communication networks may be catagorised as blocking or nonblocking. Nonblocking networks can be further classified into three different classes, *strict sense nonblocking* networks, *wide sense nonblocking* networks and *rearrangeable nonblocking* networks. Among these classes, rearrangeable nonblocking networks have the best scaling properties and are the subject of this thesis.

The properties of symmetric rearrangeable networks have been studied extensively in the literature, initially in the context of possible applications in telecommunication and subsequently for use in high-performance computing. The latter community has explored the use of parallel routing algorithms for such networks since they expected them to be deployed in support of parallel computing systems. New applications for such networks recently emerged for which these routing algorithms are unsuitable. The need for automatic deployment of digital subscriber line (DSL) technologies requires a capability for *analog* switching of perhaps thousands of subscriber loops. Secondly, increasing chip density is giving rise to Network on Chip (NoS) and System on Chip (SoC) solutions where the switching requirements are such as to make fully-connected or crossbar solution inefficient. Report<sup>4</sup> shows that big telecommunication companies are moving towards the use of NoC applications. Parallel routing solutions are unsuitable in

<sup>&</sup>lt;sup>3</sup>http://www.cisco.com/en/US/prod/collateral/ps7045/ps6129/ps6133/ps6150/prod-white-paper0900aecd8023500d.html

<sup>&</sup>lt;sup>4</sup>http://www.arteris.com/customers.php

such devices. This thesis explores the optimal design of multistage switching systems for analog and on-chip applications.

Possible blocking in a rearrangeable network is overcome by rearranging the state of the network. For time slatted operations this can be achieved in between the time slots, but for analog communication this will lead to disruption of the ongoing transmission. To overcome this issue use of extra bypass paths has been illustrated in the literature. The proposed extra paths in the network that act as bypass paths in an event of state change in the network. This type of rearrange-able network is called a repackable network. This thesis investigates the design of large scale repackable networks that require minimum hardware cost when compared to the existing proposals in literature.

Suboptimal algorithms for symmetric rearrangeable networks suffer from high blocking probabilities as the network size increases. At the same time optimal algorithms suffer from being less scalable as they require complex computation that increases with the size of the network. There is a need for an algorithm that can provide low blocking probability with low computational complexity. This thesis investigates the possibilities of constructing a feasible algorithm that meets these criteria and scales better than existing proposals.

Many optimal or deterministic routing algorithms reported in the literature are designed for full permutation, in other words, all inputs request an output. Also algorithms designed for  $2 \times 2$  switching elements cannot be scaled to work for other symmetric rearrangeable networks built with larger switching elements. This thesis studies a new routing algorithm that can address these issues. Further, an investigation is focused to determine the possibilities of designing symmetric rearrangeable networks built with larger switching elements.

# **1.2** Thesis Contribution

### 1.2.1 Problem Statement

The focus of this thesis can be categorized in two broad classes:

**Architecture:** The contribution on the architectural domain of the rearrangeable networks can be categorized into two subclasses:

- To study the large scale repackable topology and the design of a minimum cost repackable network;

- To design new symmetric rearrangeable networks built with switching elements having more than two input output ports and without compromising the zero blocking probability.

**Routing:** Contribution on the routing algorithm domain of the rearrangeable networks can be categorized into two subclasses:

- To design a new suboptimal routing algorithm that can provide lower blocking probabilities and faster execution time than that of the other deterministic routing methods;

- To design a new deterministic parallel routing algorithm that works for partial permutations both in electrical and optical domain.

### 1.2.2 Solutions

A repackable network offers performance potentially indistinguishable from that of a strictly non blocking network, in that a free path through the repackable network is always available, provided that sufficient time has elapsed since the last connection request for the network to the repacked (i.e. to be reconfigured so that a free path is available between any pair of idle inlet and outlet). Therefore, as a solution extra bypass paths have been used to build these network using rearrangeable networks as base networks. The minimum hardware cost has been achieved by using the minimum number of bypass links in the innermost stage of these networks.

The purpose of designing a suboptimal routing algorithm is to reduce the required computational processing overhead. The processing required to implement existing routing methods limits their scalability. Thus, the new method proposed herein considers good scalability properties and can route a partial permutation.

A new deterministic algorithm is designed in this thesis that works for partial permutations. Most available algorithms only work when all the input-output pairs are active, or when dummy requests are set for inactive input-output pairs. The algorithm proposed in this thesis successfully determines the routing paths without the need for dummy requests to fill out partial permutations. A modification of the new method is carried out to make it work in the parallel domain. With ever increasing demand of optical domain communications, routing algorithms need to be feasible to map into the optical domain. The new method also works in generating semi permutation for planar optical rearrangeable networks. With only minor modifications this method generates semi permutations that ensures crosstalk free routing in optical domain.

The modification of rearrangeable network topology addresses the issue of reducing network depth by using larger switching elements and at the same time realising all possible permutations and also reduces the required hardware cost. The routing decision on networks using these larger switching elements is always very challenging, as binary decision making is no longer valid. The deterministic algorithm proposed in this thesis has been modified for routing on these networks.

#### 1.2.3 Methodology

The solutions to the problems stated above have been validated by simulation for various sizes of network. In the simulator the traffic load is uniformly distributed across the network inputs and outputs, for various loads of occupancy of the network. The simulation results obtained have been compared with those of other routing algorithms. All the simulators have been tested in an Intel(R) Core(TM) 2 Quad 2.40 GHz CPU computer with a memory of 8GB.

Hardware complexity is an important issue in deploying any switching system. Crosspoint count has been used as a measurement of hardware complexity in this thesis. Hence the relative cost of using various switching element sizes has been investigated.

## **1.3 Summary of Contributions**

The contributions presented in this research are listed below:

- I did a detailed study of symmetric rearrangeable networks in this thesis. Various design proposals have been studied and are shown to be derived from Beneš based networks. A literature review has been presented on routing algorithms for symmetric rearrangeable network using both serial and parallel processing domains. The reason for choosing rearrangeable networks as a topic for this research has also being discussed.

- A new repackable topology has been proposed in this thesis. The new proposal has a reduced hardware cost compared to existing proposals reported in the literature.

- A suboptimal routing algorithm, termed the hybrid routing algorithm has been proposed. This new method achieves quick routing by trading off blocking probability against execution time. Simulation studies have been carried out to compare its performance with that of other similar methods.

The proposed new method gives a faster execution time than the looping algorithm and a better blocking performance than random routing. Mathematical complexity analysis shows that the overall complexity of the routing algorithm is  $O(N\log N)$  using a uni-processor system, where N is the number of inputs. The method does not fully support parallel implementation, but work in two inner subnetworks can be divided among four processors to reduce the execution time of the algorithm.

- A new deterministic routing algorithm has been proposed in this thesis. This method is designed to work for partial permutations without the need for dummy requests. It is always desirable to minimise the required mathematical processing associated with any algorithm. The network stages are abstracted as a set of sub-matrices to generate the conflict free routing tags. This method has better execution time than that of other existing methods. The time complexity for routing a partial permutation ( $\overline{m} < N$ ), where  $\overline{m}$  is the number of connections to route, has a better upper bound than other similar methods. Also when routing a full permutation its time complexity matches that of other proposals reported in the literature. This proposed algorithm also works in optical Beneš networks having planar topologies with necessary modifications.

- Rearrangeable networks built with large switching elements have been designed in this thesis. In the network depth is reduced without compromising the zero blocking probability by using switching elements of larger size than the 2 × 2. A new routing algorithm for this modified class of networks has been proposed in this thesis as binary decision making is no longer valid for these networks.

## **1.4** Outline of the Thesis

This thesis is organised as follows:

- **Chapter 2** An overview of available switching methods is presented, followed by a brief description of various transmission techniques. This chapter describes general network structures used in communication. Two broad classes of networks are highlighted. One is the class of self routing blocking networks and the other is the class of nonblocking networks. Three different types of nonblocking networks are also been discussed in this chapter

- **Chapter 3** Details of rearrangeable networks are given in this chapter, with a focus on popular rearrangeable networks. Different constructions of Clos networks are presented. This chapter also describes 2 × 2 symmetric rearrangeable networks, also known as Beneš networks. A detailed study of networks derived from Beneš networks are presented with their permutation realisability characteristics. Overviews of Beneš network routing algorithms, both in serial and parallel domain, are discussed in this chapter. A discussion is given showing the time complexity of the algorithms proposed in the literature for this class of networks.

- **Chapter 4** Repackable topologies which allow rearrangement without disturbing existing communication links, are studied in this chapter. A new repackable structure is designed that requires fewer crosspoints than that of the other proposals reported in the literature.

- **Chapter 5** This chapter presents a new routing algorithm termed as, hybrid routing algorithm for rearrangeable networks. Its performance has been compared to that of existing algorithms using simulation results. A mathematical complexity analysis has been executed. The analysis shows that, even in the worst case situation, the hybrid routing algorithm is bounded by the

upper limit reported in the literature. The simulation results show that this method has better performance metric than deterministic and other suboptimal algorithms, hence making it a better choice for SoC and NoC applications.

- **Chapter 6** A new routing algorithm with zero probability of blocking has been designed in this chapter. This method uses a matrix based abstraction for generating the routing tags, rather than using a complex mathematical model to determine the switching element settings. It has been shown in this chapter that the new algorithm is capable of routing requests for partial permutations. A complexity analysis shows that for serial implementation this algorithm matches the scalability in time of the state of the art. For parallel implementation and partial permutations this algorithm has complexities lower than that of other comparable methods. The designed algorithm in this chapter also works in the optical domain after minor modification. This chapter also addresses the issue of designing a symmetric rearrangeable network with larger switching elements has been extended to work for modified such symmetric rearrangeable networks.

- **Chapter 7** This chapter summarises the overall thesis and explores suggestions for possible future work arising from this research.

# **CHAPTER 2**

# SWITCHING TECHNIQUES

**S** witching and multiplexing techniques play a vital role for the effective utilization of the communication channels. Multiplexing techniques are divided into two categories: Frequency Division Multiplexing (FDM) and Time Division Multiplexing (TDM). Similarly, switching techniques are divided into two broad classes: Packet Switching and Circuit Switching. This chapter will provide an overview of various multiplexing techniques followed by common switching techniques that are in current use in communications systems.

## 2.1 Multiplexing

Multiplexing is the method of sharing a common medium by two or more communication channels. This makes better use of the available bandwidth of the common medium, that to dedicate that medium for a single channel. In communication systems, transmission mediums such as fibre, coaxial or microwave have been shared by multiple channels for transmitting data simultaneously [2]. Fig. 2.1 illustrates the principle of multiplexing.

Figure 2.1: General multiplexing technique.

FREQUENCY

Figure 2.2: Frequency division multiplexing.

### 2.1.1 Frequency Division Multiplexing

Frequency division multiplexing (FDM) [3–5] is the oldest form of multiplexing technique for communication systems. Utilization of the entire bandwidth of communication link is carried out in this technique by modulating multiple signals into different career frequencies. In that way more than one signal(each with a bandwidth less than the link bandwidth) can be transmitted at the same time using a single communication link. This multiplexing works in the analog domain even if the individual signals are digital. An example of an FDM system is broadcast FM radio. Each FM station receives its own frequency band for transmission within the VHF FM band. There are multiple FM channels that broadcast their transmissions at the same time without interference. Fig. 2.2 illustrates the principle of dividing total bandwidth *F* among multiple signals  $f_1 \dots f_n$ .

FREQUENCY

Figure 2.3: Time division multiplexing.

### 2.1.2 Time Division Multiplexing

Time division multiplexing (TDM) [6, 7] allows each signal to use the entire bandwidth of the transmission link for a short duration. In this way, TDM allows all the signals to use the entire channel capacity in turn. There are two kinds of TDM commonly used: Synchronous Time Division Multiplexing and Statistical Time Division Multiplexing. In a synchronous system, the system can be under used because the connected sources are active most of the time but they are not transmitting any data. Statistical TDM dynamically allocates the transmission link on demand. Statistical TDM can make better use of the transmission link than synchronous TDM, since bandwidth is not reserved for possible idle sources. Statistical TDM is associated with packet switching as discussed in 2.2.2. Fig. 2.3 illustrates a synchronous TDM link where time slots  $T_1 \dots T_n$  use the full bandwidth in turn.

### 2.1.3 Wavelength Division Multiplexing

Communication in the optical domain offers increased bandwidth. The equivalent of FDM in the optical domain is termed as wavelength division multiplexing

Figure 2.4: (Dense)Wavelength division multiplexing.

(WDM) [8, 9]. In WDM transmission , multiple optical rays of different wavelengths are transmitted through an optical link [10–12]. It was first demonstrated in Bell Labs in 1997 [13]. Their range of the transmitted wavelengths are in the nanometer range. This method creates a number of virtual fibres inside a single fibre, which can transmit light of different wavelengths.

With the growth of new high bandwidth consumer applications and the increasing demand in the use of Internet over the last decade, standard WDM dose not provide enough capacities. Current communication demands requires the use of Dense Wavelength division Multiplexing (DWDM) [14, 15]. DWDM allows more virtual optical fibres inside a single optical fiber than standard WDM, leaving small gaps between the virtual paths [16]. A common DWDM system uses two fibers, one as a transmission link and other one as a receiving link with amplifiers in between those cables. Fig. 2.4 shows the general block diagram of a (D)WDM system where  $\lambda_1 \dots \lambda_n$  are signals of different wavelengths.

## 2.2 Switching

To transmit data from source to destination, an effective and efficient switching mechanism is required [17]. There are two broad classes of switching: Circuit Switching [18, 19] and Packet Switching [20–22].

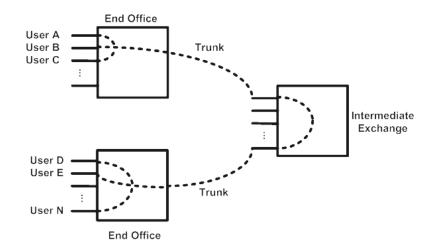

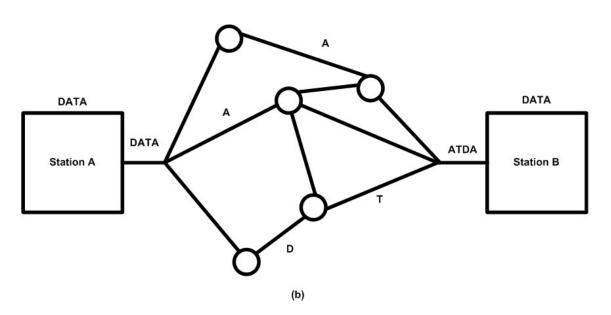

### 2.2.1 Circuit Switching

The basic concept of circuit switching [23, 24] is the establishment of dedicated communication paths from source to destination or in the reverse direction. The conventional telephone system is a good example of circuit switching. Once the calling party is connected to the called party, a circuit is established between the two parties. Until one of the parties hangs up , the circuit is occupied by that call. Fig. 2.5 shows the general concept of circuit switching. Circuit switching allows each channel to use fixed and dedicated bandwidth for the duration to the connection. A circuit connection has three phases:

- **Circuit Establishment:** Before starting actual communication between parties, an end-to-end circuit needs to be established. This process checks the availability of a suitable path as well as the status of the calling party. If any one of these two is unavailable or busy, the circuit cannot be established.

- **Transmission of Data:** After the establishment of the connecting path between the calling and called parties, it is possible to exchange information between the two parties.

- **Circuit Disconnect:** Once the period of information exchange has ended, the connection is terminated, so that other parties can use the released resources.

Circuit switching can be of two different types: Space Division Switching [25– 27] and Time Division Switching [17, 28]. Space division switching basically means establishing the actual physical paths between source and destination. This is achieved by setting collection of crosspoints in active state which are connected by connecting links. These crosspoints remain dedicated for the communication till the duration of the communication. Fig. 2.6 shows space division switching inside a switching Network.

Time division switching (TDS) brakes incoming low speed signals into pieces and creates a frame combining multiple pieces from the incoming singals and

Figure 2.5: Circuit switching.