# EXAMINATION OF SOLDER BUMP REFLOW PROCESS AND COPPER METALLISATION PROCESS INDUCED STRESS DISTRIBUTION IN SILICON SUBSTRATES USING SYNCHROTRON X-RAY TOPOGRAPHY, MICRO-RAMAN SPECTROSCOPY AND FINITE ELEMENT MODELLING

# JARUJIT KANATHARANA

# DOCTOR OF PHILOSOPHY IN ELECTRONIC ENGINEERING

SUPERVISED BY PROFESSOR PATRICK MCNALLY

SCHOOL OF ELECTRONIC ENGINEERING

DUBLIN CITY UNIVERSITY

**DECEMBER 2002**

Jarujit Kanatharana

I hereby certify that this material, which I now submit for assessment on the

programme of study leading to the award of Doctor of Philosophy is entirely my own

work and has not been taken from the work of others save and to the extent that such

work has been cited and acknowledged within the text of my work.

Signed: \_\_\_\_\_\_ (Candidate)

ID No.:

99145081

Date: \_\_\_09 JULY 2003

# **ABSTRACT**

Due to the fact that semiconductor devices have decreased significantly in geometry and increased enormously in electronic design complication, flip-chip packaging technology was launched to increase input/output (I/O) count, improve electrical performance, reduce packaging size, and to be cost effective. The Intel®Pentium®III microprocessor uses the popular ball grid array (BGA) packaging technique. The ball grid array (BGA) is one of the most common flip-chip packaging techniques used for microprocessor applications. However, mechanical stresses induced by the flip-chip process are a major concern for the reliability of such devices.

In addition, Copper (Cu) is becoming the interconnect metal of choice and is rapidly replacing Aluminium alloys (Al/Cu) in the Integrated Circuit (IC) industry. However, mechanical reliability issues, such as those related to thermal strain are also a major concern.

The aim of this thesis is to employ the application of white beam synchrotron x-ray topography (WBSXRT), micro-Raman spectroscopy (MRS) and Finite Element Modeling (FEM) to investigate the spatial extent of strain fields imposed on the underlying silicon substrate for microelectronic packaging of Intel<sup>®</sup>Pentium<sup>®</sup>III microprocessors due to the lead-tin solder bump process for BGA packaging, and to evaluate and compare stress distributions in Si wafers due to the electroless Cu interconnect process with varying geometrical line width in IC processing and compare with the sputtered Cu interconnect technique.

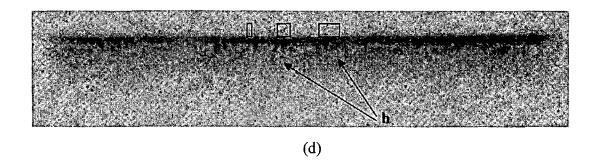

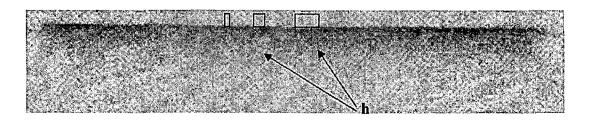

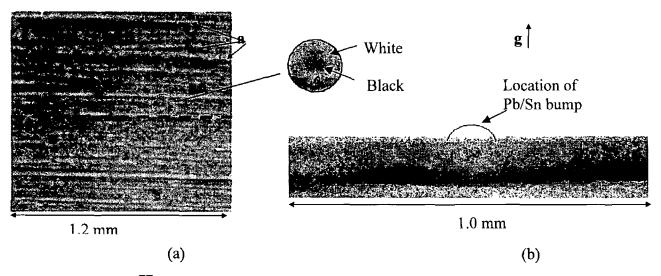

In the case of the lead-tin solder bump process, large area and section back-reflection SXRT images were taken before and after a simulation of the reflow process at 350°C in atmosphere. The effects of strain imposed by the overlying bump structures in these x-ray topographs have been observed principally via orientational contrast. The estimated magnitudes of stress,  $|\tau_{xy}|$ , imposed on the underlying silicon were

calculated to be of the order of 100 MPa. A simulation of the orientational contrast at the edge of bump was performed based on the kinematical theory of x-ray diffraction. The degree of lattice distortion is well fitted to the topographs of the *post*-reflow sample. The spatial strain in the underlying silicon was relieved dramatically after the lead bumps were removed from the wafer, which confirms that the solder bump formation is indeed a major source of strain in the underlying Si.

Micro-Raman Spectroscopy (MRS) is used to confirm the strain fields in the Si due to the reflow process. For *pre*-reflowed samples, an approximate uniaxial compressive stress ( $\sigma_{xx}$ ) of 200 MPa is developed near the edge of the under bump metallisation (UBM). However, a tensile stress ( $\sigma_{xx}$ ) up to ~300 MPa is found for *post*-reflowed samples.

Two-dimensional (2-D) plane strain Finite Element Modelling (FEM) has also been performed. The magnitudes and spatial distribution of the stresses after the reflow process are in good agreement with the SXRT and MRS results.

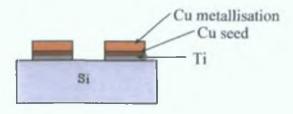

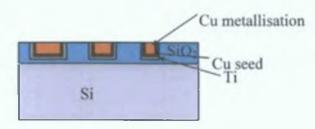

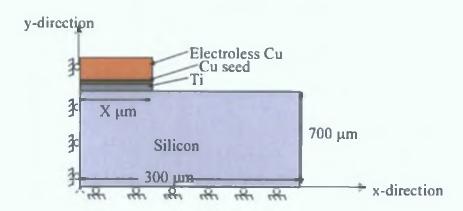

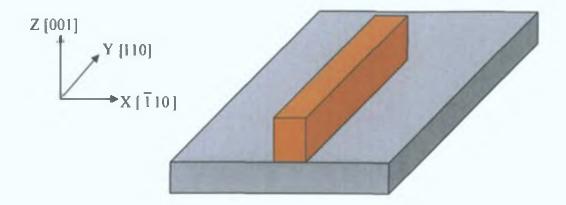

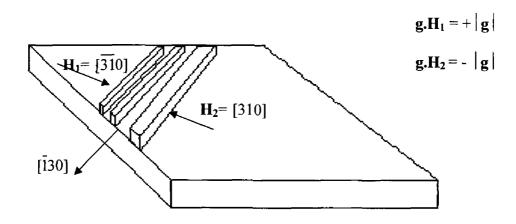

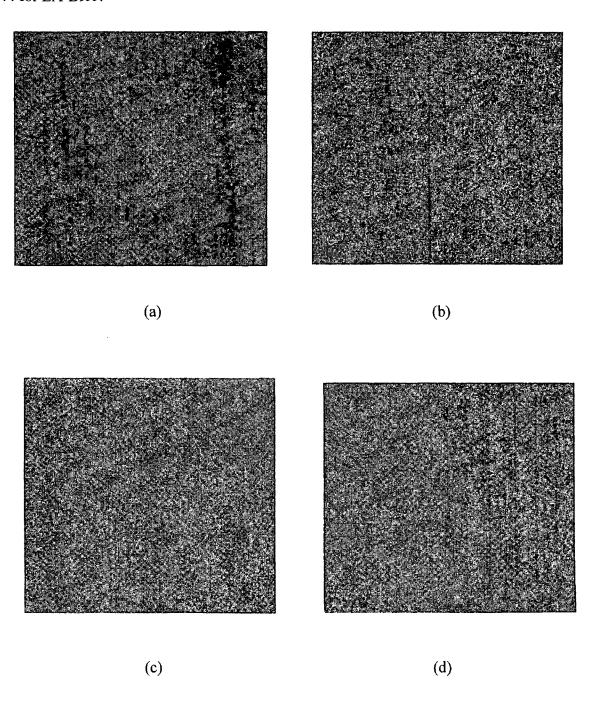

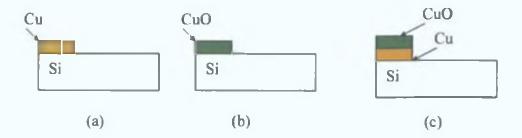

In case of the Cu metallization, 100 nm of Ti is used as a barrier layer and 20 nm of sputtered Cu is used as a seed layer. Electroless and sputtered Cu were subsequently deposited on patterned Si wafers with 4, 6, 8, 10, 20, 40, 60 and 100 µm line widths using a lift-off patterning and single damascene pattern.

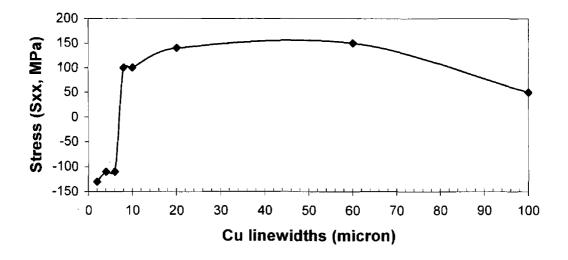

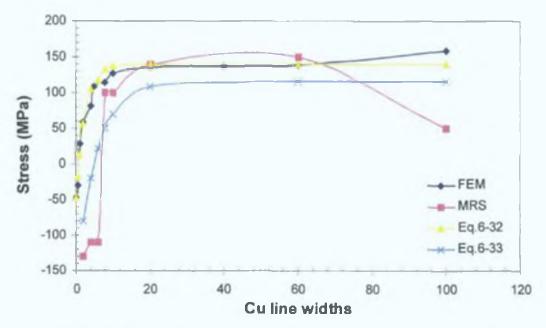

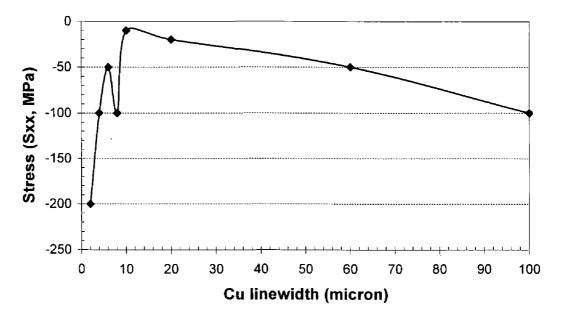

The presence of distinct orientational contrast observed in section topographs suggests that the strain fields in the Si substrate reach values as high as ca. 100 MPa nears the metal edge. The stress magnitudes in the underlying Si as a function of individual line widths were measured using MRS. Compressive stresses of  $\sim$ 100 MPa were found in the Si wafer near the line edges when the width is less than 10  $\mu$ m. The stresses changed to tensile with a magnitude of the order of 100 MPa at metal widths of 10-60  $\mu$ m and decreased to  $\sim$ 50 MPa for 100  $\mu$ m widths. The FEM analysis confirmed this tendency.

Large area back-reflection WBSXRT revealed that strain fields in the Si due to the Cu metallisation were relieved when the sample was heated to 100°C. Subsequently, the stress increases again when the sample was heated up to 400°C.

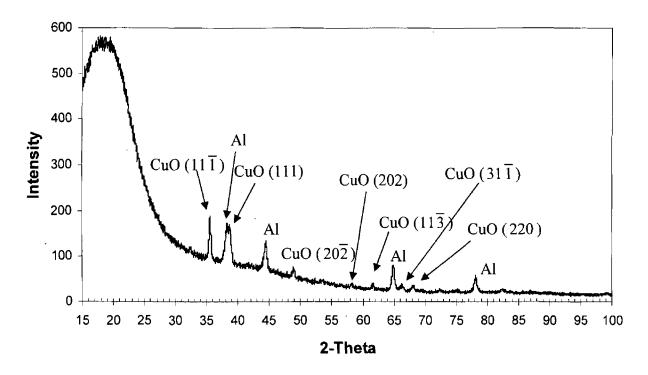

When the samples are returned to room temperature, the MRS data confirms that the strain in the Si near the metal edges become more compressive than in the unannealed case. X-ray diffraction (XRD) data confirms the generation of new material phases after the heat treatment.

## **ACKNOWLEDGEMENTS**

First and foremost, I would like to thank my supervisor, Dr. Patrick McNally, for giving me the great opportunity to work on this project. I genuinely appreciate his support and guidance throughout my study.

I wish to thank Dr. Juan Pérez-Camacho who supported me on this project from Intel Ireland site, as his help was a great asset.

I would like to thank Optoelectronics Laboratory, Helsinki University of Technology, Finland, Prof. Turkka Tuomi for his kind advice and Juha Riikenen for all X-Ray Diffraction (XRD) works.

I would like to thank our collaborators, Dr. David McNeill and especially Brian Toh at Queen's University Belfast (QUB) Northern Ireland for their assistance in the metal deposition, sputtered copper metallization and Atomic Force Microscopic (AFM) measurement.

My thanks also go to the technicians and all other academic and non-academic staff at the School of Electronic Engineering.

I wish to thank T. Wroblewski at beam line F-1 in HASYLAB Germany for all the SXRT works throughout my study.

My special thanks go to my family in Thailand who have been supporting me throughout my time in Ireland and also Mr. Nathapong Suthiwongsunthorn for his encouragement and support. In addition, I also want to thank all my friends in Ireland, i.e. Weng Li-Chuan, Theresa Collins, Emira Dautbegovic, Orla Duffnero, etc. and in Thailand.

This work was supported by the TMR-Contract ERBFMGECT950059 of the European Community.

At last, I would like to thank to the Intel Ireland Academic Relations Programme and Enter for contributions throughout my postgraduate support.

# **TABLE OF CONTENTS**

|          |                                                  | Pages |

|----------|--------------------------------------------------|-------|

| Abstra   | ct                                               | ii    |

| Ackno    | wledgement                                       | v     |

| Table o  | of Contents                                      | vii   |

| Table o  | of Figures                                       | xiii  |

| Table of | of Tables                                        | xxix  |

| List of  | Abbreviations                                    | XXX   |

| СНАР     | TER 1 INTRODUCTION                               |       |

| 1.1      | Backgrounds                                      | 1     |

| 1.2      | Objectives of this Project                       | 5     |

| 1.3      | Outlines of this Thesis                          | 6     |

| СНАР     | TER 2 SYNCHROTRON X-RAY TOPOGRAPHY (SXRT)        |       |

| 2.1      | Synchrotron Radiation Source                     | 7     |

|          | 2.1.1 Synchrotron Radiation (SR)                 | 7     |

|          | 2.1.1.1 Synchrotron Radiation Component          | 10    |

|          | 2.1.1.2 Emission Patterns                        | 12    |

|          | 2.1.1.3 Synchrotron Radiation: Advantage for XRT | 15    |

| 2.2      | X-ray Topography                                 | 16    |

|          | 2.2.1 Theories                                   | 16    |

|          | 2.2.2 Kinematical Theory                         | 18    |

|          | 2.2.3 Dynamical Theory                           | 19    |

|          | 2.2.4 Techniques                                 | 43    |

| 2.3      | SXRT Interpretation and Stress Analysis          | 50    |

| СНАР     | TER 3 MECHANICAL STRAIN MODELS                   |       |

| 3.1      | Stress-Strain Relationship                       | 57    |

| Jarujit | Kanath | arana |

|---------|--------|-------|

|---------|--------|-------|

| 3.2 | Finite | Element Modelling (FEM)                            | 59         |

|-----|--------|----------------------------------------------------|------------|

|     | 3.2.1  | Plane Stress and Plane Strain                      | <b>6</b> 0 |

| 3.3 | Exam   | ple of Models                                      | 62         |

|     | 3.3.1  | FEM of flip-chip process induced stress in         | 62         |

|     |        | a silicon substrate                                |            |

|     | 3.3.2  | FEM of Cu Metallisation Induced Stress in Si       | 65         |

|     |        | Substrate in IC Processing                         |            |

| СНА | PTER 4 | 4 MICRO-RAMAN SPECTROSCOPY (MRS)                   |            |

| 4.1 | The R  | aman Scattering Mechanism                          | 67         |

| 4.2 | Electr | omagnetic Radiation and Classical Light Scattering | 71         |

| 4.3 | Rama   | n Scattering in Semiconductors                     | 76         |

| 4.4 | Stress | Measurement using Micro-Raman Spectroscopy         | 77         |

|     | 4.4.1  | Uniaxial Stress Model                              | 80         |

|     | 4.4.2  | Line Force Model                                   | 83         |

| 4.5 | Micro  | -Raman Spectroscopic Instrumentation               | 88         |

|     | 4.5.1  | Laser                                              | 89         |

|     | 4.5.2  | Sample System                                      | 92         |

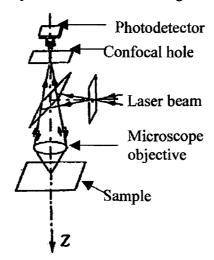

|     | 4.5.3  | Confocal Hole                                      | 93         |

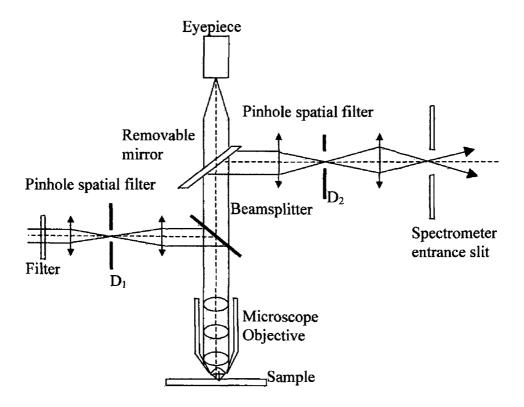

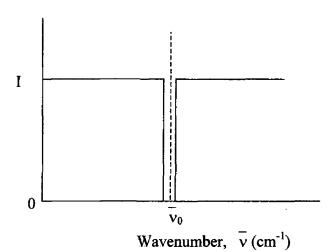

|     | 4.5.4  | Filtering System                                   | 94         |

|     | 4.5.5  | Spectrometer                                       | 95         |

|     | 4.5.6  | Photoelectric Detector                             | 96         |

| СНА | PTER S | S SOLDER BUMP REFLOW PROCESS INDUCED               | STRESS     |

|     |        | DISTRIBUTION IN SILICON SUBSTRATES                 |            |

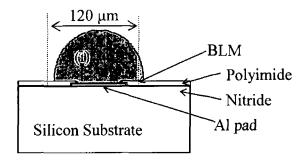

| 5.1 | Flip C | Chip Technology                                    | 100        |

|     | 5.1.1  | Under Bump Metallisation (UBM)                     | 100        |

|     | 5.     | 1.1.1 Electroplating UBM                           | 101        |

|     | 5.     | 1.1.2 Electroless UBM                              | 103        |

|     | 5.1.2  | UBM Design Guidelines                              | 104        |

|     | 5.1.3   | Solde               | r Bumps                                                      | 105   |

|-----|---------|---------------------|--------------------------------------------------------------|-------|

|     | 5.1.4   | Bump                | oing Process                                                 | 106   |

|     | 5.      | 1.4.1               | Evaporation Process                                          | 106   |

|     | 5.      | 1.4.2               | Electroplating Process                                       | 108   |

|     | 5.1     | 1.4.3               | Wire Bumping Process                                         | 109   |

|     | 5.      | 1.4.4               | Screen Printing Process                                      | 109   |

| 5.2 | Solder  | bump                | Ball Grid Array (BGA) Applications                           | 110   |

|     | for Int | el <sup>®</sup> Pen | tium <sup>®</sup> III                                        |       |

| 5.3 | Exper   | imental             | Details                                                      | 110   |

|     | 5.3.1   | Samp                | le Details                                                   | 111   |

|     | 5.3.2   | Synch               | rotron X-Ray Topographic Measurement                         | 112   |

|     | 5.3.3   | Finite              | Element Modelling                                            | 113   |

|     | 5.3.4   | Micro               | -Raman Spectroscopic Measurement                             | 115   |

| 5.4 | Result  | s and D             | Discussions                                                  | 120   |

|     | 5.4.1   | Synch               | rotron X-ray Topography                                      | 120   |

|     | 5.4     | <b>4</b> .1.1       | Stress Distribution in Si as a Function of Various           | 120   |

|     |         |                     | Metal Etching Times                                          |       |

|     | 5.4     | 4.1.2               | Stress Distributions in Si due to Pb/Sn Solder Bump          | o 127 |

|     |         |                     | Reflow Rrocess                                               |       |

|     | 5.4     | 1.1.3               | Major Source of Stress Distribution in the Silicon substrate | 135   |

|     | 5.4.2   | Finite              | Element Modelling                                            | 139   |

|     | 5.4.3   | Micro               | -Raman Spectroscopy                                          | 148   |

|     | 5.4.4   | X-Ray               | y Diffraction and Transmission Microscopy                    | 154   |

|     | 5.4.5   | A Sin               | nulation of BRST of Post-Reflowed Process Sample             | 155   |

|     | 5.4     | 4.5.1               | An Analysis of the extinction contrast                       | 155   |

|     | 5.4     | 1.5.2               | An Analysis of the orientational contrast                    | 163   |

| 5.5 | Concl   | usions              |                                                              | 160   |

# CHAPTER 6 COPPER METALLIZATION PROCESS INDUCED STRESS IN SILICON SUBSTRATES USED IN IC PROCESSING

| 6.1 | Coppe  | er Meta  | allisation in IC Processing                                 | 171    |

|-----|--------|----------|-------------------------------------------------------------|--------|

|     | 6.1.1  | Dual     | Damascene Patterning                                        | 179    |

|     | 6.1.2  | Depo     | sition of Copper                                            | 181    |

|     | 6.     | 1.2.1    | Physical Vapour Deposition (PVD)                            | 181    |

|     | 6.     | 1.2.2    | Electrochemical Deposition (ECD)                            | 184    |

|     | 6.1.3  | Mech     | no-Electrochemical Effects                                  | 191    |

| 6.2 | Exper  | imenta   | l Details                                                   | 194    |

|     | 6.2.1  | Samp     | ole details                                                 | 194    |

|     | 6.2.2  | Expe     | rimental Details of Synchrotron X-Ray Topography            | 197    |

|     | 6.2.3  | Expe     | rimental Details of Finite Element Modelling                | 199    |

|     | 6.2.4  | Expe     | rimental Details of Micro-Raman Spectroscopic               | 200    |

|     | ,      | measi    | urement                                                     |        |

| 6.3 | Result | ts and I | Discussions                                                 | 202    |

|     | 6.3.1  | Syncl    | hrotron X-ray Topography                                    | 202    |

|     | 6.3    | 3.1.1    | Electroless Cu metallisation and lattice curvature          | 203    |

|     | 6.3    | 3.1.2    | Comparison of Electroless and Sputtered Cu<br>metallisation | 207    |

|     | 6.3    | 3.1.3    | Temperature Dependence of the Electroless and               | 227    |

|     |        |          | Sputtered Cu Metallisation Processing Induced               |        |

|     |        |          | Strain Fields in Si Substrate                               |        |

|     | 6.3    | 3.1.4    | Geometry Line Width and Cu thickness Dependen               | ce 229 |

|     |        |          | of the Electroless Cu Metallisation Process Induce          | d      |

|     |        |          | Strain Fields in Si Substrate                               |        |

|     | 6.3.2  | Finite   | e Element Modelling                                         | 250    |

|     | 6.3    | 3.2.1    | Influence of Cu line widths on strain field in Si           | 250    |

|     | 6.3    | 3.2.2    | Simulation of the Cu Metallisation due to                   | 257    |

|     |        |          | the Heating Effect                                          |        |

|     | 6.3.3  | Micro    | o-Raman Spectroscopy                                        | 259    |

|     | 6.3    | 3.3.1    | Comparison of Electroless and Sputtered Cu                  | 260    |

|             |                   | metallisation                                        |              |

|-------------|-------------------|------------------------------------------------------|--------------|

|             | 6.3.3.2           | Influence of Cu line widths on strain field in Si    | 263          |

|             | 6.3.3.3           | Influence of Cu Line width on the Stress             | 265          |

|             |                   | Distributions in Si wafers                           |              |

|             | 6.3.1.4           | Effect of Annealing Process on Stress Distribution   | ns 272       |

|             |                   | in Si Substrate due to the Electroless Cu Metallisa  | ation        |

|             | 6.3.4 X-          | Ray Diffraction                                      | 277          |

| 6.4         | Conclusion        | ns                                                   | 284          |

| СНА         | PTER 7 CO         | ONCLUSIONS AND FUTURE WORKS FOR THIS                 | S PROJECT    |

| 7.1         | Solder B          | ump Reflow Process Induced Stress Distribution in    | 286          |

|             | Silicon Su        | ubstrates                                            |              |

|             | 7.1.1 Su          | mmary                                                | 286          |

|             | 7.1.2 Fu          | ture Plans                                           | 287          |

| 7.2         | Copper me         | etallisation Process Induced Stress Distribution in  | 288          |

|             | Silicon Su        | bstrates                                             |              |

|             | 7.2.1 Su          | mmary                                                | 288          |

|             | 7.2.2 Fu          | ture Plans                                           | 290          |

| REF         | ERENCES           |                                                      | 292          |

| APPI        | E <b>NDIX:</b> A. | Publications                                         |              |

| <b>A</b> 1: | Investigati       | ion of Mechanical Stresses in Underlying Silicon due | to Lead-Tir  |

|             | Solder Bu         | umps via Synchrotron X-Ray Topography and Fi         | nite Elemen  |

|             | Analysis, 1       | MRS Spring Meeting, Mat. Res. Soc. Symp. Proc. Vol   | . 682E, N5.7 |

| A2:         | Evaluation        | n of Mechanical Stresses in Silicon Substrates due   | to Lead-Tir  |

Modeling, Microelectronic Engineering, Vol. 65, 2003, pp. 209-221.

Solder Bumps via Synchrotron X-Ray Topography and Finite Element

- A3: Examination of Mechanical Stresses in Silicon Substrates due to Lead-Tin Solder Bumps via Micro-Raman Spectroscopy and Finite Element Modelling, Will be published in Semiconductor Science and Technology.

- A4: White Beam Synchrotron X-Ray Topography Studies of Pb/Sn Ball Grid Array Induced Strain in Si Substrate, Hamburger Synchrotronstrahlungslabor HASYLAB am Deutschen Elektronen-Synchrotron DESY, User Meeting, 2000, http://www-hasylab.desy.de/science/annual reports/2000 report/.

- A5: White Beam Synchrotron X-Ray Topography Studies of Copper interconnect Induced Strain Si processing in Substrate, Hamburger Synchrotronstrahlungslabor **HASYLAB** am Deutschen Elektronen-Synchrotron DESY, User Meeting, 2001, http://www-hasylab.desy.de/ science/ annual reports/ 2001 report/.

- A6: Mapping of Mechanical Stresses in Silicon Substrates due to Lead-Tin Solder Bump Reflow Process via Synchrotron X-Ray Topography and Finite Element Modeling, will be published in Journal of Applied Physics: D.

- A7: Estimation of Mechanical Stresses in Silicon Substrate due to Lead-Tin Solder Bumps via Synchrotron X-Ray Topography, Micro-Raman Spectroscopy and Finite Element Modeling, waiting for review in IEEE Transactions in Electronic Devices.

# **TABLE OF FIGURES**

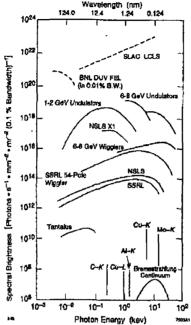

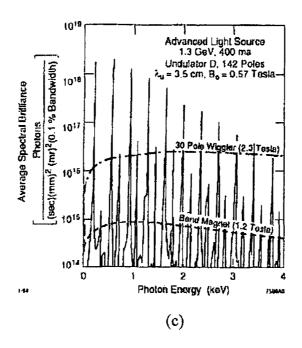

| Figure 2-1  | Spectral brightness from various radiation sources.                                        | 8  |

|-------------|--------------------------------------------------------------------------------------------|----|

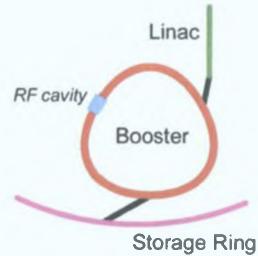

| Figure 2- 2 | The general synchrotron source system.                                                     | 11 |

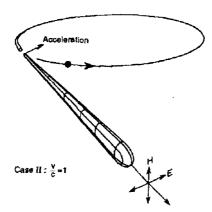

| Figure 2-3  | Emission pattern of the radiation when the electron/                                       | 13 |

|             | positron speed approaches the speed of light.                                              |    |

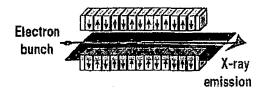

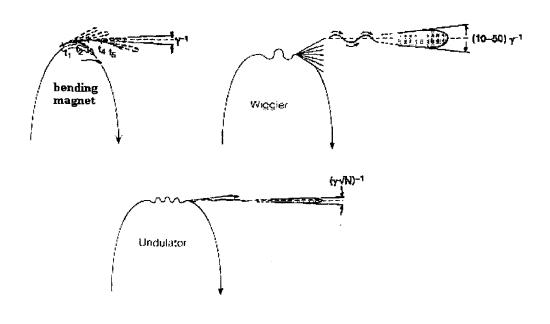

| Figure 2- 4 | (a) The alternating magnetic pole system used to generate                                  | 16 |

|             | wiggler and undulator radiation, (b) Radiation patterns                                    |    |

|             | of bending magnet (white beam), wiggler and undulator,                                     |    |

|             | and (c) Emission spectra of bending magnet (white beam),                                   |    |

|             | wiggler and undulator.                                                                     |    |

| Figure 2-5  | X-ray diffraction for rectangular grid case.                                               | 17 |

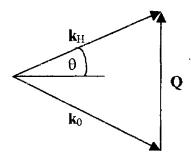

| Figure 2- 6 | The vector relationship between the incident vector $k_0$ ,                                | 19 |

|             | the scattered beam vector k <sub>H</sub> and the scattering vector Q.                      |    |

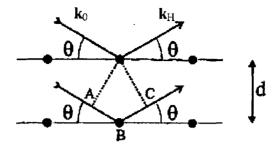

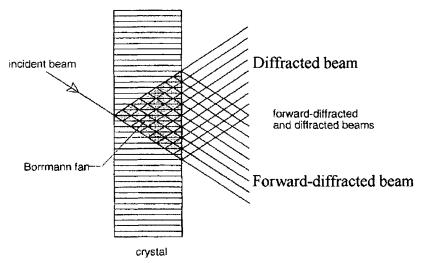

| Figure 2-7  | The diffraction and re-diffraction of an X-ray beam                                        | 20 |

|             | from a set of reflecting planes. The triangle bounded                                      |    |

|             | by the incident beam and diffracted beam from the                                          |    |

|             | entry surface is called the Borrmann fan.                                                  |    |

| Figure 2-8  | Boundary condition for wavevectors at the entrance                                         | 25 |

|             | surface.                                                                                   |    |

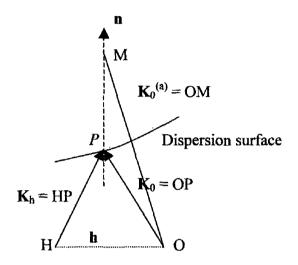

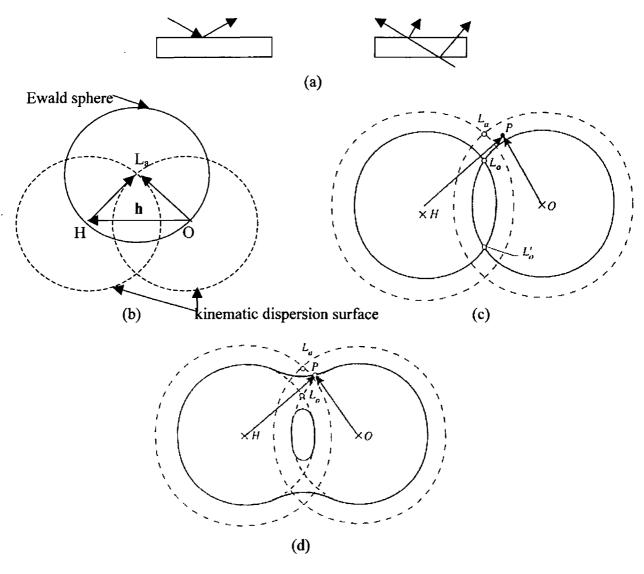

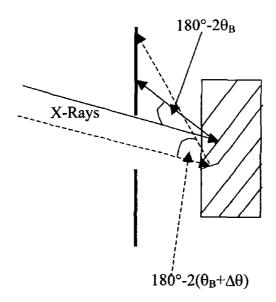

| Figure 2- 9 | Diffraction according to the geometrical theory,                                           | 27 |

|             | Direct space, Bragg geometry (left) and Laue                                               |    |

|             | geometry (right); (b) Reciprocal space; OH = h: reciprocal                                 |    |

|             | lattice vector, L <sub>a</sub> = Laue point; OL <sub>a</sub> = incident wave               |    |

|             | $(\overline{OL_a} = k)$ and $HL_a = reflected$ wave $(\overline{HL_a} = k)$ ; (c)Influence |    |

|             | of the refraction index where $L_0$ = Lorentz point,                                       |    |

| •           | $\overline{OL_0} = \overline{HL_0} = nk$ , OP = refracted wave and HP = reflected          |    |

|             | wave and $L_0' = Lorentz$ point corresponding to the                                       |    |

|             | reciprocal lattice vector HO = -h; (d) Interaction of the                                  |    |

|              | refracted (OP) and reflected (HP) waves. The solid line                        |    |

|--------------|--------------------------------------------------------------------------------|----|

|              | is called the dispersion surface and P is the tiepoint.                        |    |

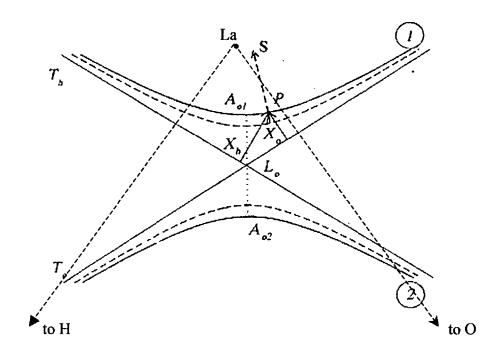

| Figure 2- 10 | Intersection of the dispersion surface with the plane                          | 29 |

|              | of incidence. Full hyperbola: polarization normal to                           |    |

|              | the plane of incidence (c=1). Dashed hyperbola:                                |    |

|              | polarization parallel to the plane of incidence (c= $\cos 2\theta_B$ ).        |    |

|              | S = Poynting vector and P = tiepoint of a Bloch wave                           |    |

|              | or wavefield.                                                                  |    |

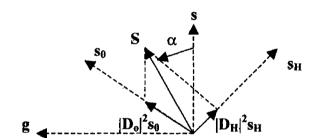

| Figure 2- 11 | Poynting vector, S, of a wavefield where s <sub>0</sub> and s <sub>H</sub> are | 33 |

|              | unit vectors in the incident and reflected directions,                         |    |

|              | respectively, s is a unit vector parallel to the lattice plane,                |    |

|              | g is a unit vector parallel to the reciprocal lattice vector                   |    |

|              | and $\alpha$ is an angle between the propagation direction                     |    |

|              | and the lattice planes.                                                        |    |

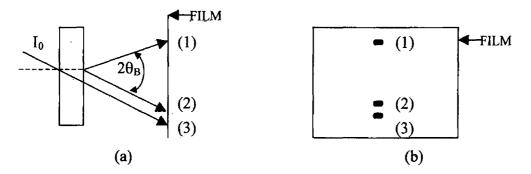

| Figure 2- 12 | Geometry of the beams when anomalous transmission                              | 34 |

|              | occurs. (a) Ray diagram to describe spots on the film.                         |    |

|              | most of the energy resides in the diffracted beam                              |    |

|              | spot (1) and forward diffracted beam spot (2).                                 |    |

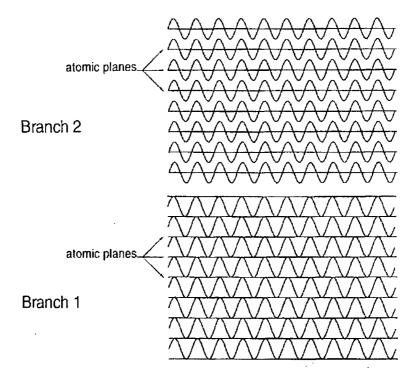

| Figure 2- 13 | Standing waves in anomalous transmission geometry.                             | 35 |

|              | The nodes of the wavefield from Branch 2 of the                                |    |

|              | dispersion surface lie on the atomic planes and thus                           |    |

|              | encounter low absorption. Branch 1 wavefields, on the                          |    |

|              | other hand, are heavily absorbed.                                              |    |

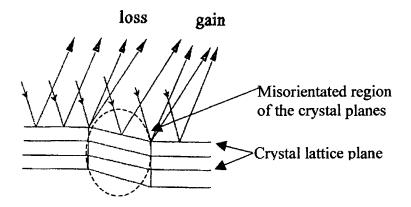

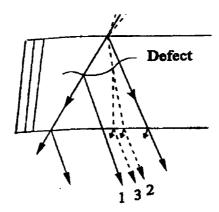

| Figure 2- 14 | The origin of the orientational contrast mechanism                             | 37 |

|              | for white beam radiation.                                                      |    |

| Figure 2- 15 | The orientational contrast mechanism in cases                                  | 38 |

|              | of severe lattice distortion.                                                  |    |

| Figure 2- 16 | Generation of the extinction contrast image where the                          | 39 |

|              | strain gradient is high. 1 is the direct image, 2 is                           |    |

|              | the dynamical image and 3 is the intermediary image.                           |    |

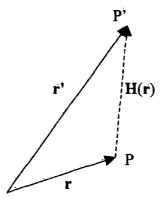

| Figure 2- 17 | Deformation of a crystal, where h(r) is a deformation                          | 40 |

|              | vector.                                                                        |    |

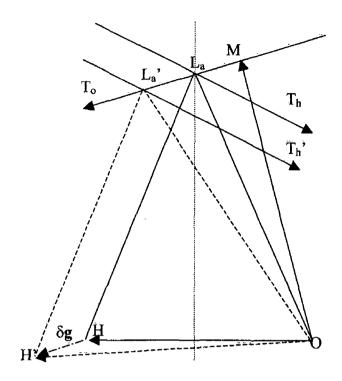

| Figure 2- 18 | Modification of the reciprocal lattice due to the                               | 42 |

|--------------|---------------------------------------------------------------------------------|----|

|              | deformation of the crystal, where La is Laue point                              |    |

|              | before deformation, La' is Laue point after deformation,                        |    |

|              | δg is the variation of the reciprocal lattice vector.                           |    |

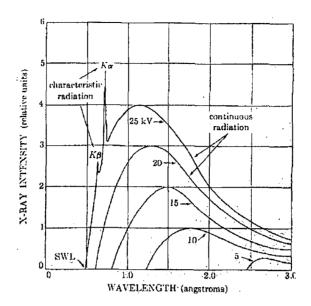

| Figure 2- 19 | X-ray spectrum of a molybdenum anode target as a                                | 44 |

|              | function of applied voltage for an x-ray tube.                                  |    |

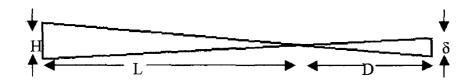

| Figure 2- 20 | The spatial resolution limit set by the projected source                        | 45 |

|              | height normal to the incident beam.                                             |    |

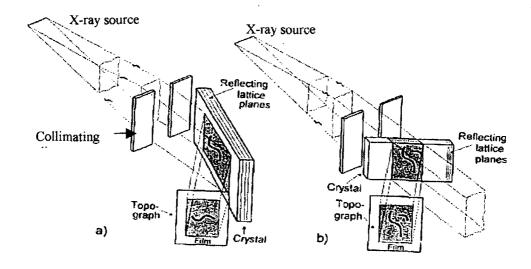

| Figure 2- 21 | Berg-Barrett technique in reflection and transmission                           | 46 |

|              | with film normal to the diffracted beam.                                        |    |

| Figure 2- 22 | The experiment set-up for projection x-ray topography.                          | 47 |

|              | Sample and film are scanned across the beam. Note that                          |    |

|              | scanning is not employed for the section topography set-up                      | ). |

| Figure 2- 23 | Back-reflection Topography.                                                     | 48 |

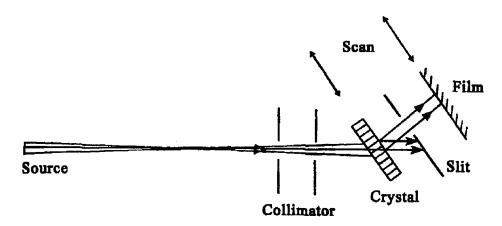

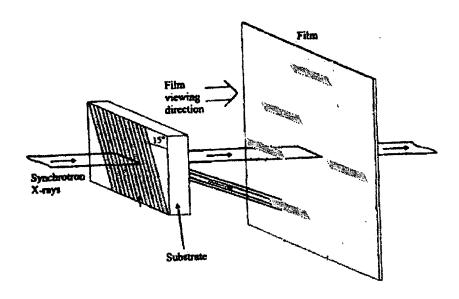

| Figure 2- 24 | Back reflection section topography set-up.                                      | 49 |

| Figure 2- 25 | Large area transmission geometry for x-ray topography.                          | 49 |

| Figure 2- 26 | Transmission section topography.                                                | 50 |

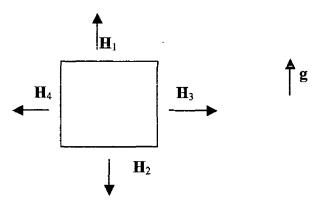

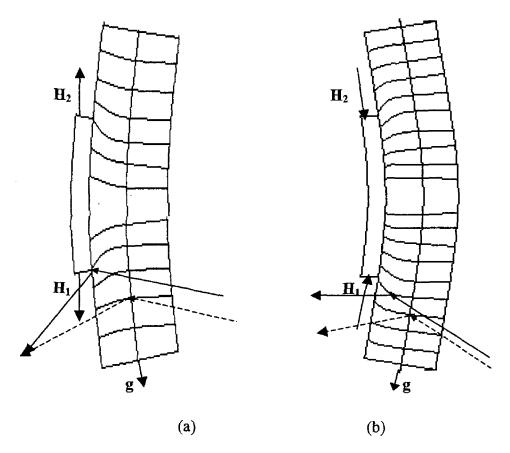

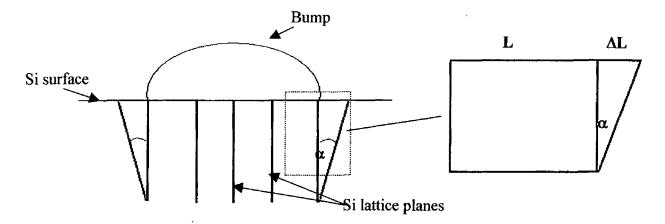

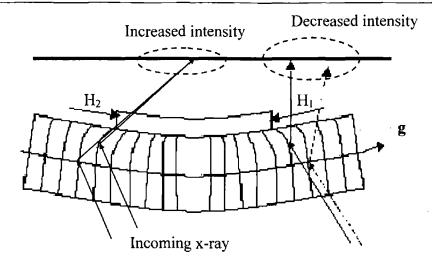

| Figure 2- 27 | The lattice displacement (H <sub>i</sub> ) of Si lattice planes, due            | 51 |

|              | to a square overlayer. The imposed strain in the Si pushes                      |    |

|              | away from the edges of this overlayer (i.e. Si is in                            |    |

|              | compression) as indicated by the displacement vectors H <sub>i</sub> .          |    |

|              | For the sake of this discussion, the direction of the diffraction               | on |

|              | vector, g, is shown                                                             |    |

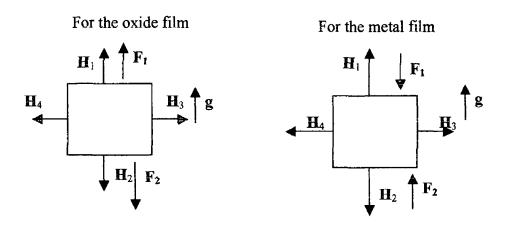

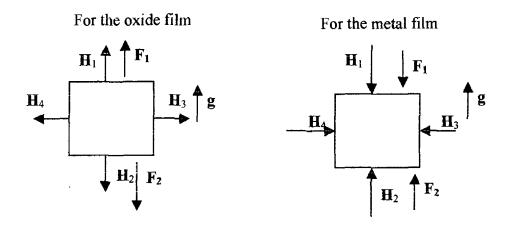

| Figure 2- 28 | The force (F <sub>i</sub> ) and g.H <sub>i</sub> relation of Meieran and Blech. | 52 |

| Figure 2- 29 | An alternative and easier explanation for x-ray                                 | 53 |

|              | topographic contrast around a strained structure.                               |    |

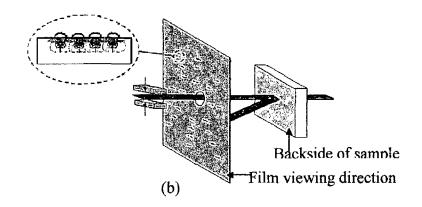

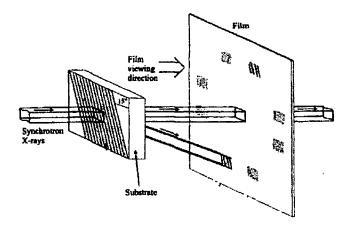

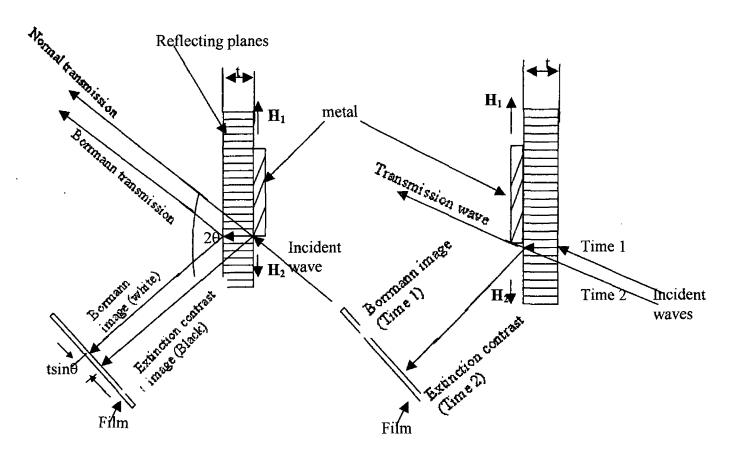

| Figure 2- 30 | Two set-ups for extinction contrast topography:                                 | 54 |

|              | the metal layer faced the x-ray source and                                      |    |

|              | (b) the metal layer faced the recorded film.                                    |    |

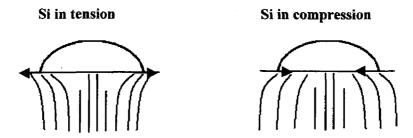

| Figure 2- 31 | Strain directions in Si substrate.                                              | 55 |

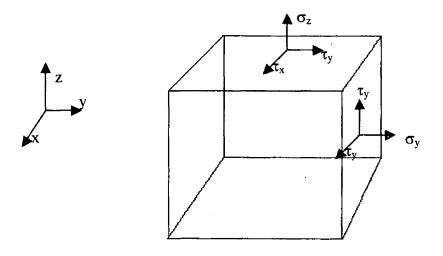

| Figure 3- 1  | The cubic element.                                                              | 58 |

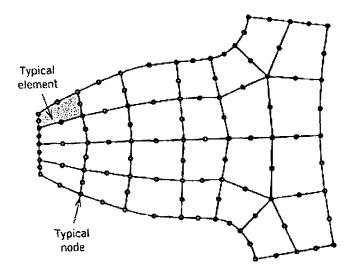

| Figure 3- 2  | Two-dimensional model of a gear tooth. It is noted                      | 59 |

|--------------|-------------------------------------------------------------------------|----|

|              | that all nodes and elements are in the plane of the paper.              |    |

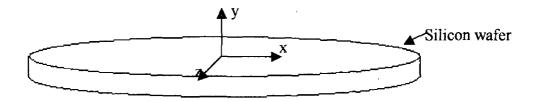

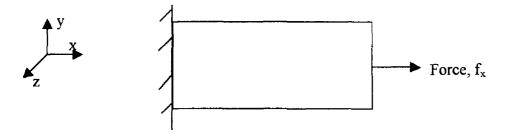

| Figure 3-3   | The general geometry of the plane model                                 | 60 |

|              | for semiconductor applications.                                         |    |

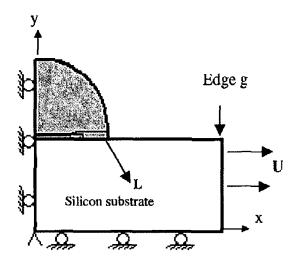

| Figure 3- 4  | The geometry for plane stress and strain analysis.                      | 60 |

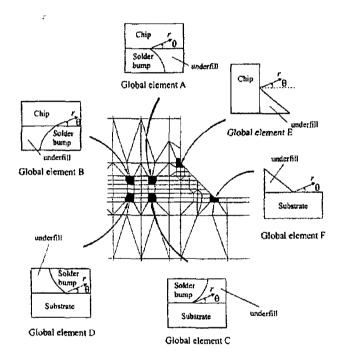

| Figure 3-5   | Locations of global elements as part of the local                       | 63 |

|              | finite element representation in the presence of underfill.             |    |

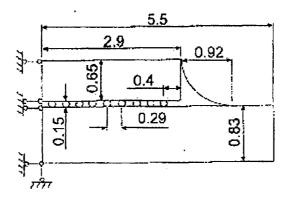

| Figure 3- 6  | The geometry and boundary conditions of flip-chip for                   | 64 |

|              | the FEM study. It is noted that the scale is in mm.                     |    |

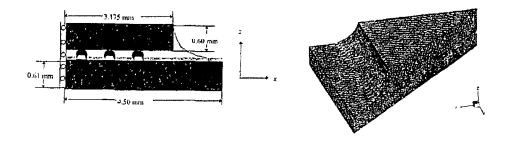

| Figure 3- 7  | Geometry, dimensions and boundary conditions for                        | 65 |

|              | the 2-D and 3-D FEM study.                                              |    |

|              |                                                                         |    |

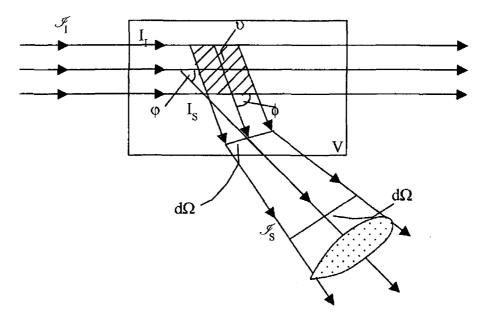

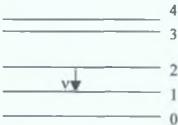

| Figure 4- 1  | Idealised scattering experiment.                                        | 69 |

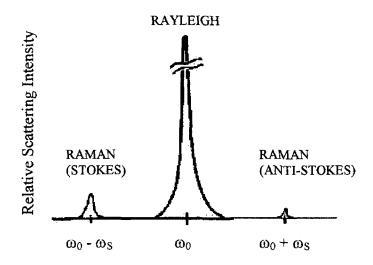

| Figure 4- 2  | Molecular vibrations in the sample at frequency $\omega_S$ .            | 70 |

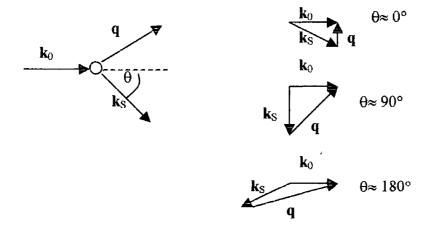

| Figure 4- 3  | The scattering process and their geometries                             | 71 |

|              | given Eq. 4-2 and Eq. 4-3, $\mathbf{q} = \mathbf{k}_0 - \mathbf{k}_S$ . |    |

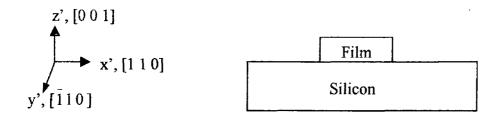

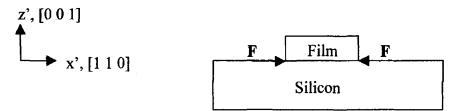

| Figure 4- 4  | The direction of the sample along the cross section of                  | 80 |

|              | the sample. It is noted that $\sigma_{11}$ ' is the uniaxial stress     |    |

|              | along the x'-axis.                                                      |    |

| Figure 4- 5  | The direction coordinates of the sample along its                       | 84 |

|              | cross section, where F is the force at the edge of the film.            |    |

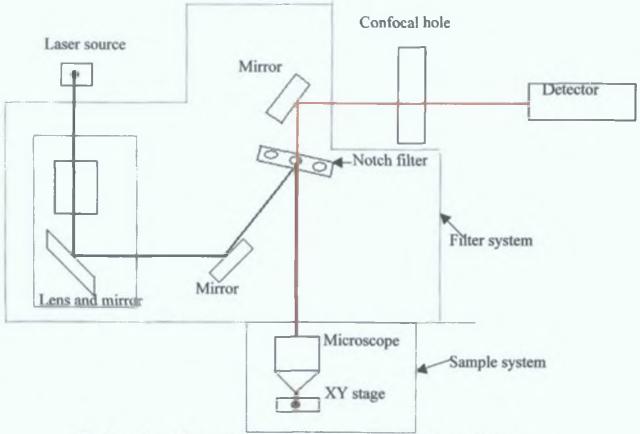

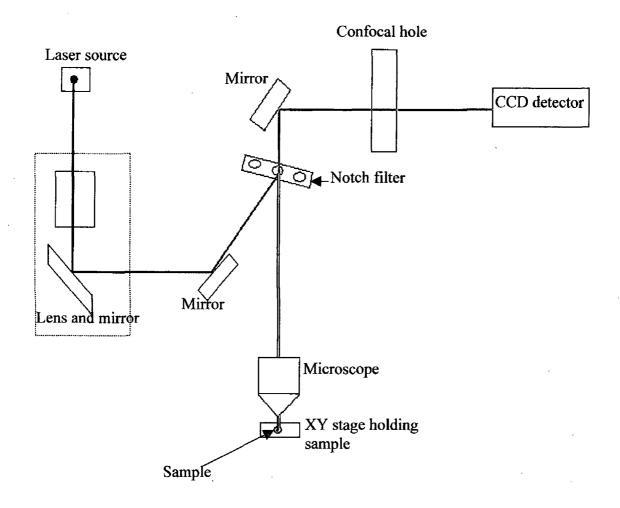

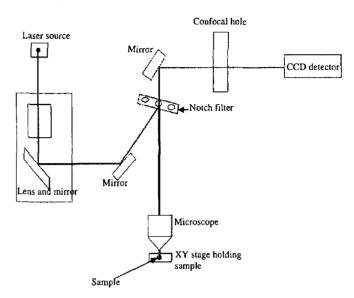

| Figure 4- 6  | The experimental micro-Raman spectroscopy system.                       | 88 |

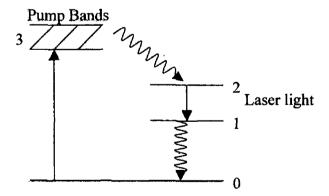

| Figure 4- 7  | Diagram of energy levels for a generic atom.                            | 89 |

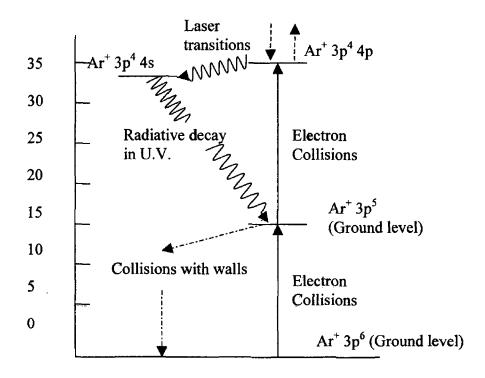

| Figure 4-8   | A diagram represents a four-level laser system.                         | 90 |

|              | Level 3 is normally broad for a solid and sharp                         |    |

|              | for a gas.                                                              |    |

| Figure 4-9   | Configurations related to laser action in the                           | 91 |

|              | Ar <sup>+</sup> laser.                                                  |    |

| Figure 4- 10 | The sample system in micro-Raman spectroscopy.                          | 92 |

| Figure 4- 11 | Basic diagram of the micro-Raman spectrometer                           | 93 |

|              | equipped with the confocal diaphragms.                                  |    |

| Figure 4- 12 | The spectral response of an ideal notch filter.                            | 95  |

|--------------|----------------------------------------------------------------------------|-----|

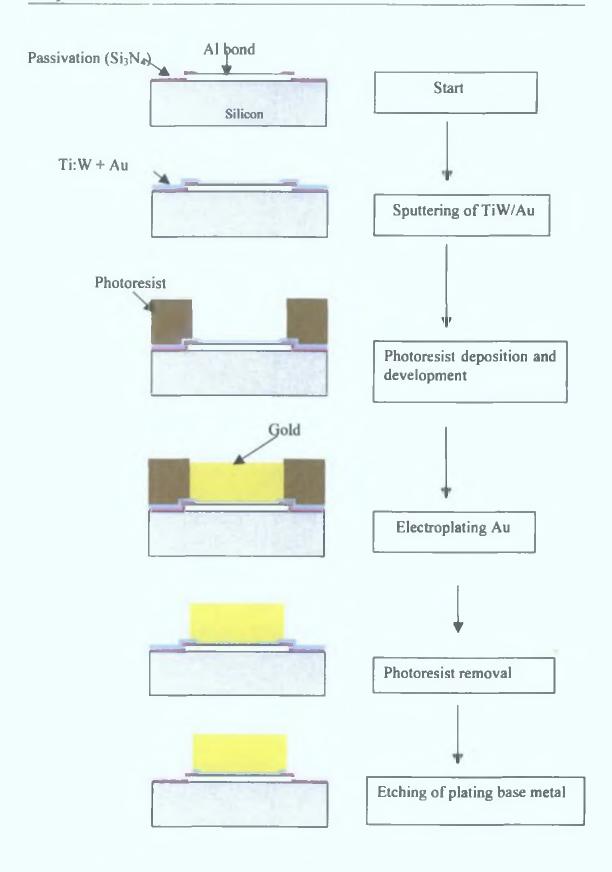

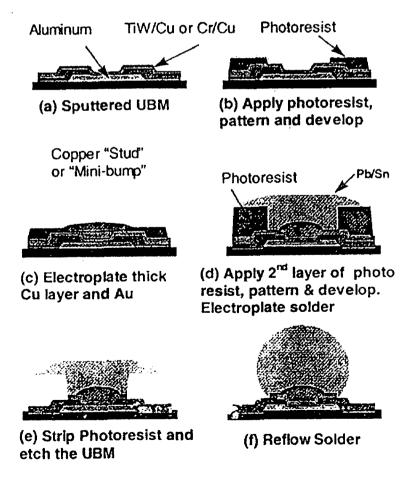

| Figure 5- 1  | Schematic process flow for electroplated gold bumps.                       | 102 |

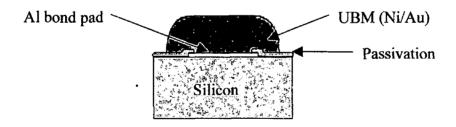

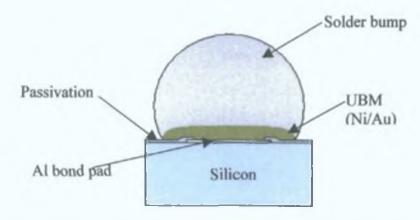

| Figure 5- 2  | Cross section of electroless Ni/Au on Al bond pads.                        | 103 |

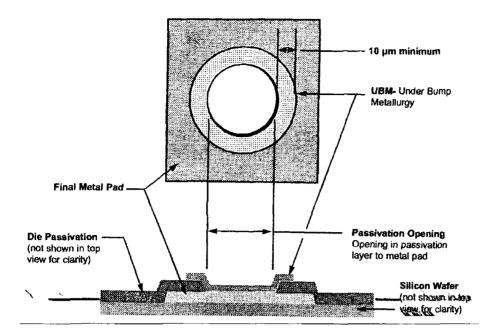

| Figure 5- 3  | Bond pad design and UBM dimension requirement.                             | 105 |

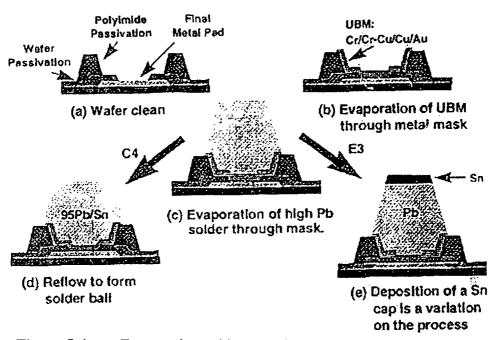

| Figure 5- 4  | Evaporating solder bumping process.                                        | 107 |

| Figure 5- 5  | Electroplating UBM and solder bumping process.                             | 108 |

| Figure 5- 6  | Solder paste printed onto silicon die.                                     | 109 |

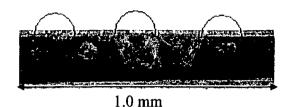

| Figure 5- 7  | Cross section of solder bump after solder reflow process.                  | 110 |

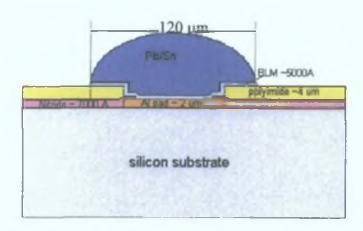

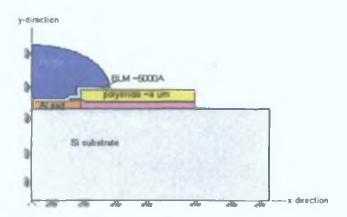

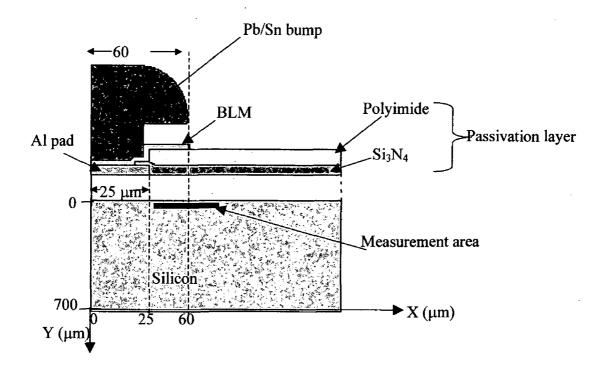

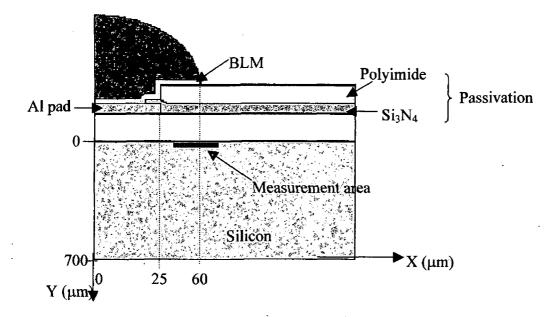

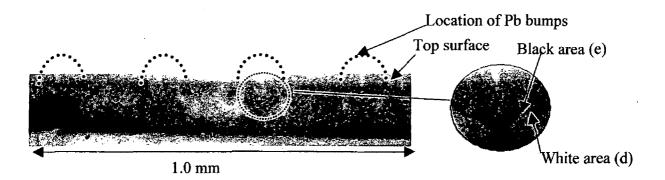

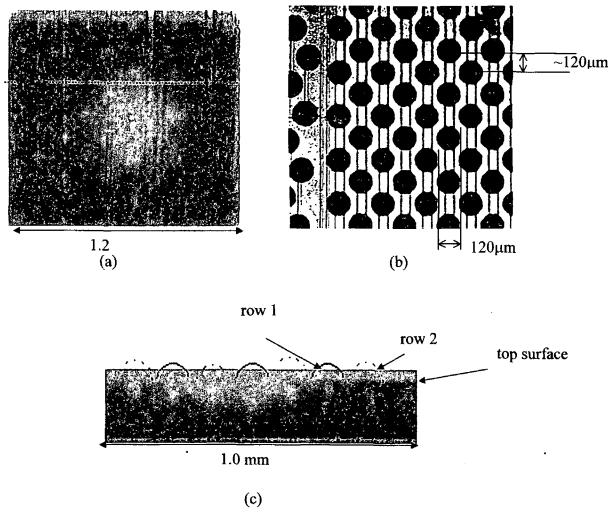

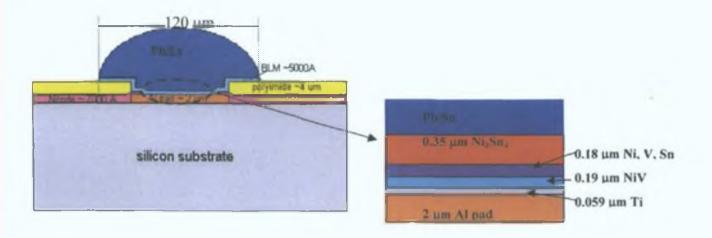

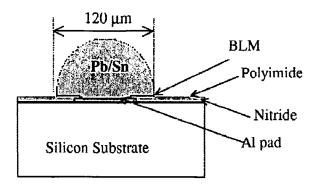

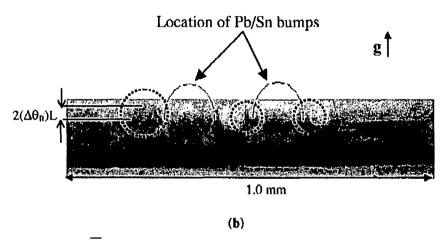

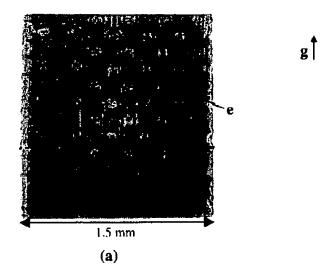

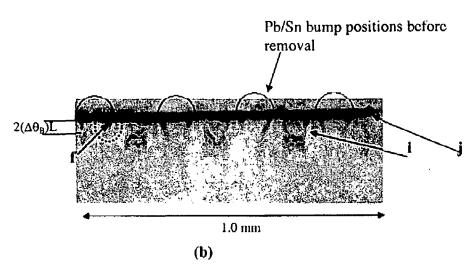

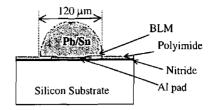

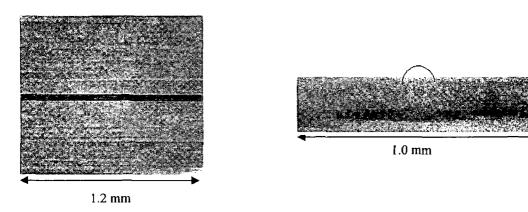

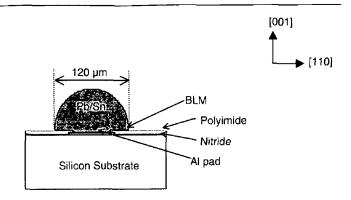

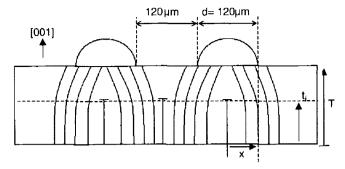

| Figure 5-8   | Geometry and dimensions of Pb/Sn solder bump sample.                       | 111 |

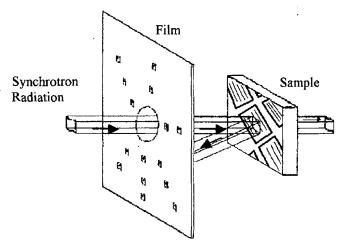

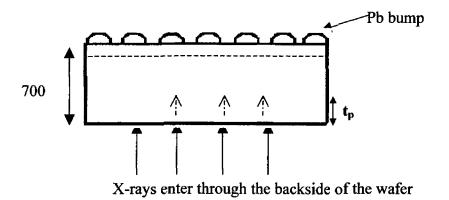

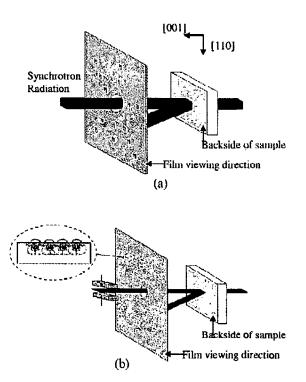

| Figure 5- 9  | An overview of the x-ray topography set-up for the                         | 113 |

|              | BGA samples.                                                               |     |

| Figure 5- 10 | Geometry and boundary conditions for the                                   | 114 |

|              | post-reflowed sample model.                                                |     |

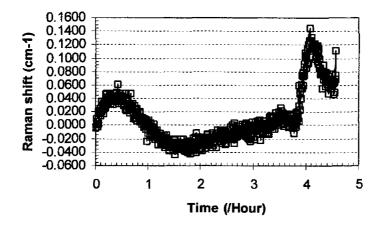

| Figure 5- 11 | The micro-Raman spectroscopy system set-up.                                | 116 |

| Figure 5- 12 | The resolution of micro-Raman system with                                  | 117 |

|              | Ar+ laser.                                                                 |     |

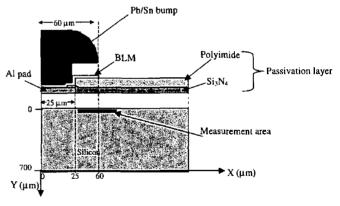

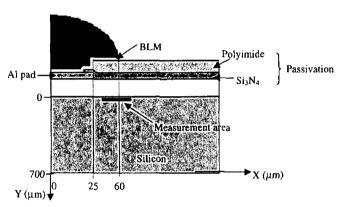

| Figure 5- 13 | Geometry and dimensions of the pre-reflowed                                | 118 |

|              | process sample. Note: the solid area represents the                        |     |

|              | measurement area via X-Y mapping. The positions                            |     |

|              | $X=25~\mu m$ and 60 $\mu m$ are the edges of the metal pad                 |     |

|              | and of the Pb/Sn bump, respectively. The position                          |     |

|              | $Y = 0 \mu m$ is the interface between the Si and the                      |     |

|              | metal/passivation layers.                                                  |     |

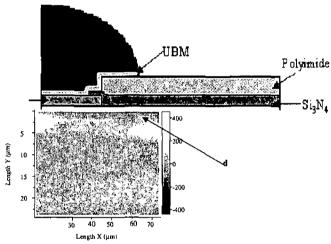

| Figure 5- 14 | The geometry and approximate dimensions of the                             | 119 |

|              | post-reflowed process sample.                                              |     |

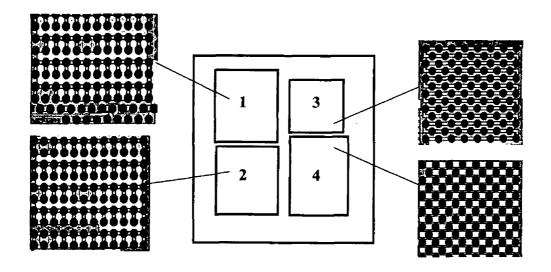

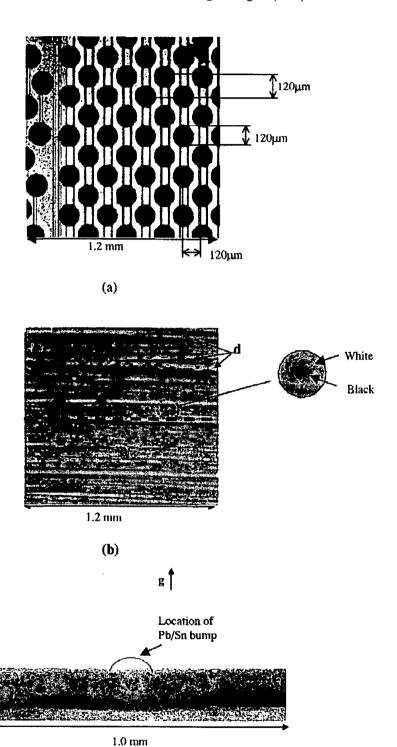

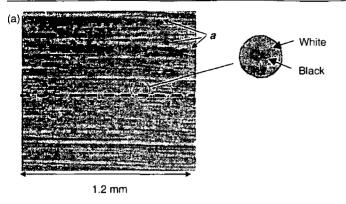

| Figure 5- 15 | Four small units in a die of sample wafer.                                 | 120 |

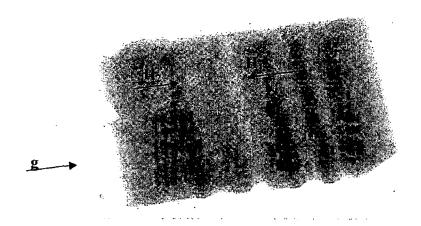

| Figure 5- 16 | $\overline{3}$ $\overline{3}$ 9 BRT of sample wafer number 445, 35 minutes | 121 |

| •            | etching time, at position A (ref # r25f3-2).                               |     |

| Figure 5- 17 | The curvature changes in Si lattice planes, which                          | 122 |

|              | give rise to the extinction contrast effect.                               |     |

| Figure 5- 18 | $\bar{3}\bar{3}9$ BRST of sample wafer number 445, 35 minutes                                       | 123   |

|--------------|-----------------------------------------------------------------------------------------------------|-------|

|              | etching time, at position A (ref # r24f7).                                                          |       |

| Figure 5- 19 | 3 3 9 topographs of sample wafer number 445 at                                                      | 124   |

|              | position B; (a) BRT (ref# r24f17) and (b) BRST (ref# r24f1                                          | 5-2). |

| Figure 5- 20 | $\bar{3}\bar{3}9$ Topographs of Pb/Sn solder bump wafer                                             | 125   |

|              | number 511, standard etching time of 10 minutes;                                                    |       |

|              | (a) BRT (ref# r25f4) and (b) BRST (ref# r24f28).                                                    |       |

| Figure 5- 21 | $\overline{2}$ $\overline{2}$ 8 Topographs and optical micrograph of sample                         | 126   |

|              | wafer number 511 at position B (a) BRT (ref# r24f22),                                               |       |

| ,            | its optical micrograph at the same position and                                                     |       |

|              | (c) BRST (ref# r24f21).                                                                             |       |

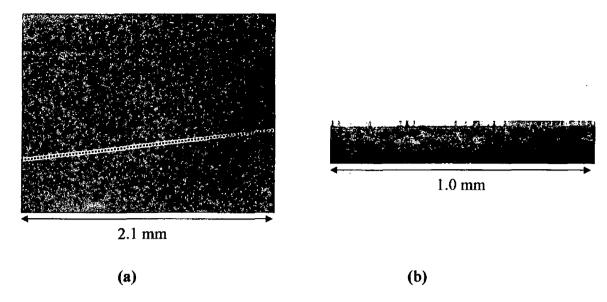

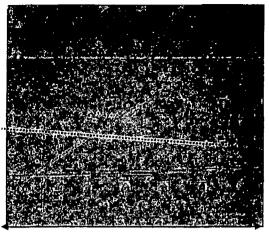

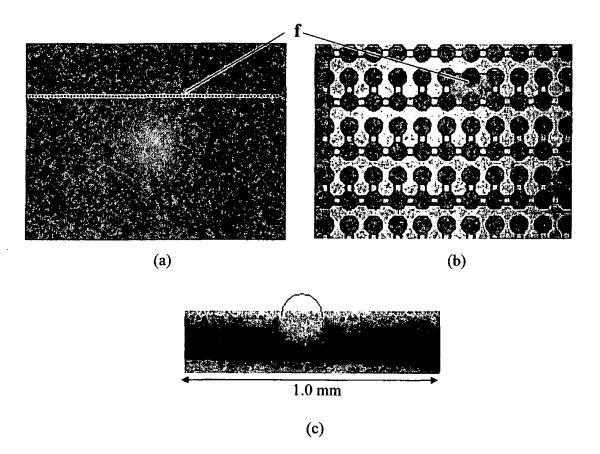

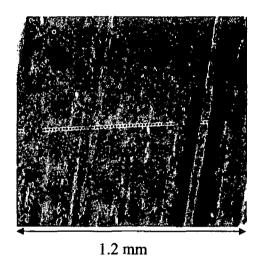

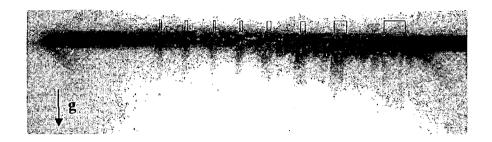

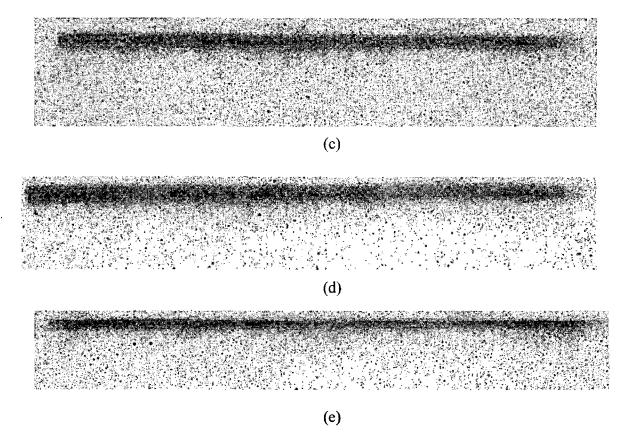

| Figure 5- 22 | Topographs of Pre-reflowed sample wafer number                                                      | 127   |

|              | 509 (15 minutes etching time): (a) $\overline{3}$ $\overline{3}$ 9 BRT (ref# r26f205                | -1)   |

|              | and (b) $\bar{3}\bar{3}9\text{BRST}$ (ref# r26f210-1).                                              |       |

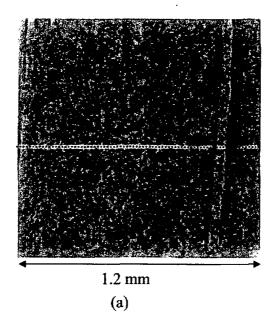

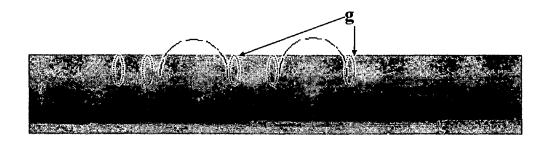

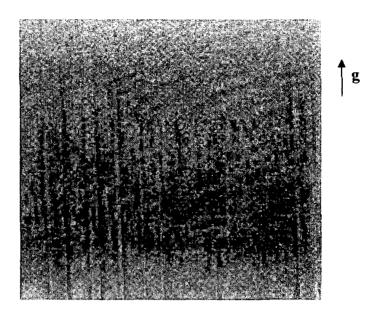

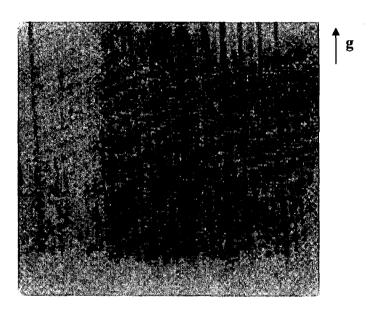

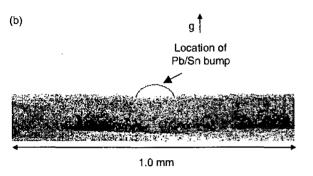

| Figure 5- 23 | (a) $\overline{3}$ $\overline{3}$ 9 BRT (ref# r26f211) and (b) $\overline{3}$ $\overline{3}$ 9 BRST | 128   |

|              | (ref# r26f214-1) images of post-reflowed sample number 5                                            | 09.   |

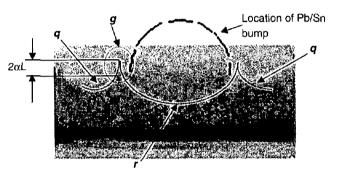

| Figure 5- 24 | The orientational contrast mechanism for the Pb/Sn                                                  | 129   |

|              | bump sample.                                                                                        |       |

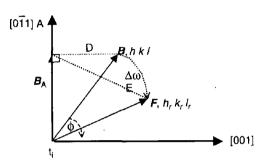

| Figure 5- 25 | Diagram shows the relationship of the misorientational                                              | 130   |

|              | contrast and shear strain.                                                                          |       |

| Figure 5- 26 | 3 3 9 BRT image of <i>Pre</i> -reflowed sample wafer                                                | 131   |

|              | number 424 (25 minutes etched, ref# r26f216).                                                       |       |

| Figure 5- 27 | 3 3 9 Topographs of <i>post</i> -reflowed sample wafer                                              | 132   |

|              | number 424 (25 minutes etched); (a) BRT (ref# r26f220)                                              |       |

|              | and (b) BRST (ref# r26f221).                                                                        |       |

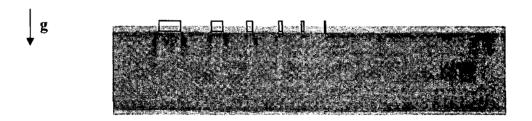

| Figure 5- 28 | Topographs of Pre-reflowed sample wafer number                                                      | 133   |

|              | 445 (35 minutes etching time); (a) $\bar{3}\bar{3}$ 9 BRT (ref# r26f3),                             |       |

|              | (b) optical micrograph of similar area and                                                          |       |

|              | (c) $\bar{3}\bar{3}9$ BRST (ref# r26f10).                                                           |       |

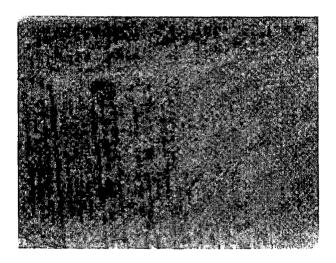

| Figure 5- 29 | Topographs of post-reflowed sample wafer number                                              | 134   |

|--------------|----------------------------------------------------------------------------------------------|-------|

|              | 445 (35 minutes etching time); (a) $\overline{3}$ $\overline{3}$ 9 BRT (ref# r26f11)         |       |

|              | and (b) $\bar{3}\bar{3}9\text{BRST}$ (ref# r26f10).                                          |       |

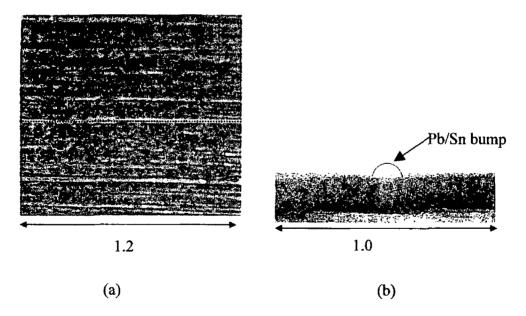

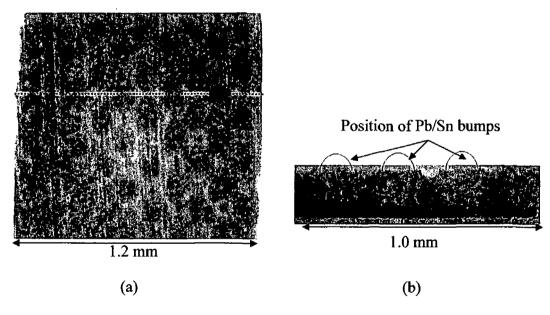

| Figure 5- 30 | (a) $\overline{2}$ $\overline{2}$ 8 BRT image of <i>Pre</i> -reflowed sample number          | 136   |

|              | 551, ref# r28f159-2, (b) an optical micrograph of the same                                   |       |

|              | area, and (c) $\overline{2}$ $\overline{2}$ 8 BRST image corresponding to the                |       |

|              | position of the dashed line, ref# r28f161-2.                                                 |       |

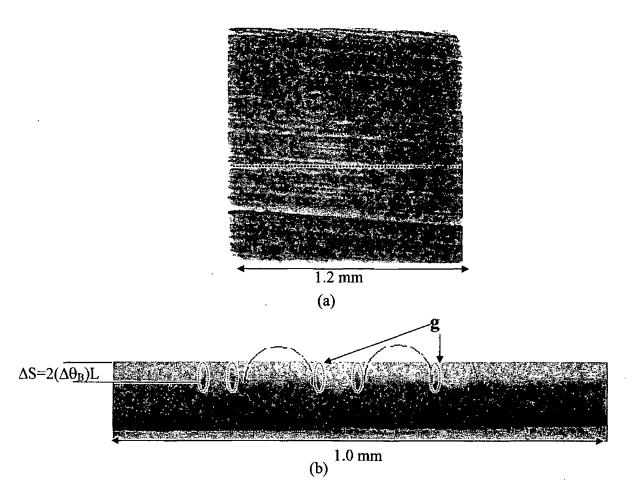

| Figure 5- 31 | (a) $\frac{1}{2}$ 8 BRT image of <i>post</i> -reflowed and etched back                       | 137   |

|              | sample wafer number 225 (ref# r28f166-3), (b) an optical                                     |       |

|              | micrograph of the same area, and (c) $\overline{2}$ $\overline{2}$ 8BRST image               |       |

|              | (ref# r28f168-2).                                                                            |       |

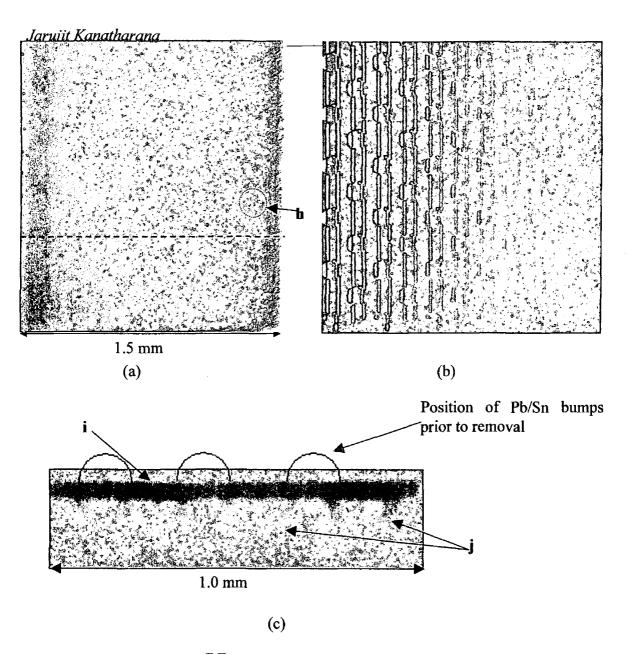

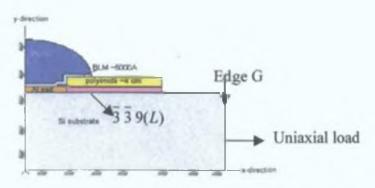

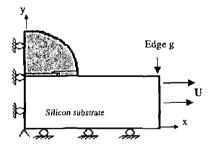

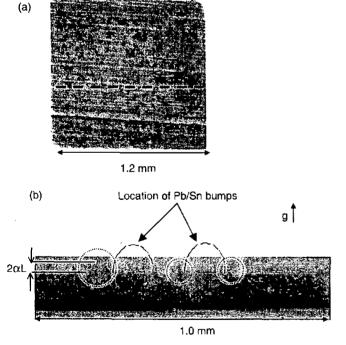

| Figure 5- 32 | The boundary and modelling condition for this study.                                         | 139   |

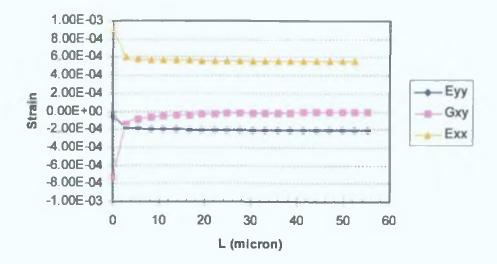

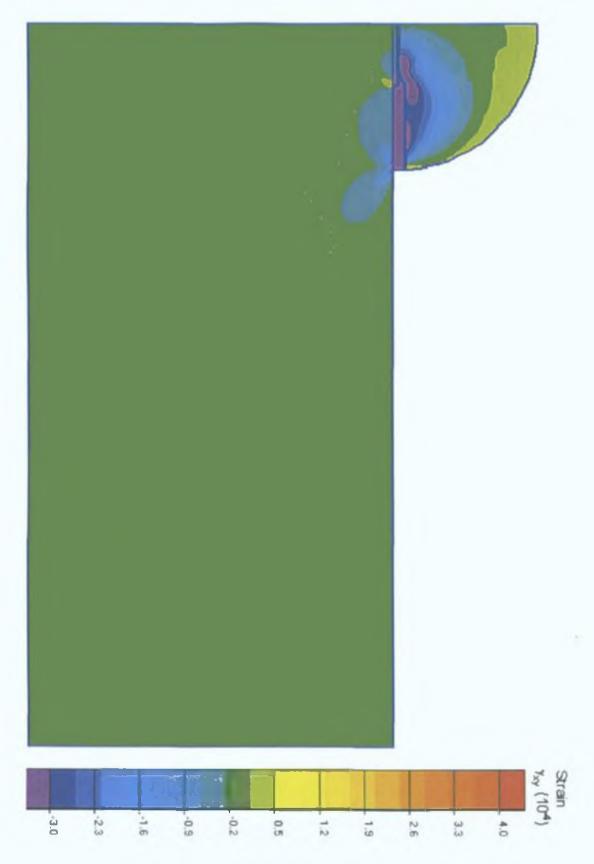

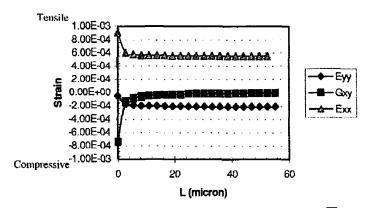

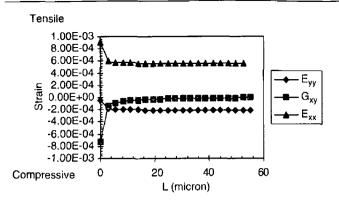

| Figure 5- 33 | Finite element simulation of tensile/compressive strain                                      | 140   |

|              | distribution in Si along the $\bar{3}\bar{3}9$ direction in the <i>post</i> -reflox          | ved   |

|              | sample simulated via uniaxial edge loading.                                                  |       |

|              | L = 0 indicates the position of the periphery of the                                         |       |

|              | Pb/Sn bump, Exx and Eyy = normal strains in x- and                                           |       |

|              | y- directions, and Gxy = shear strain.                                                       |       |

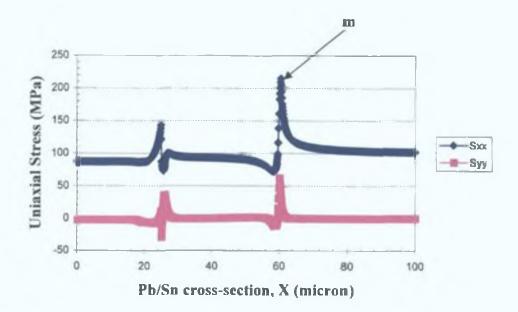

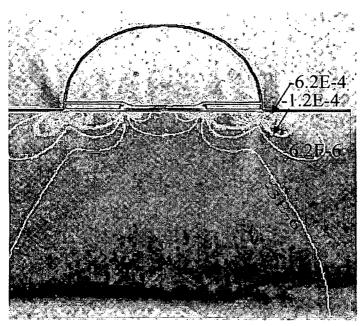

| Figure 5- 34 | The simulated normal stresses ( $S_{xx}$ and $S_{yy}$ , or $\sigma_{XX}$ and $\sigma_{YY}$ ) | ) 141 |

|              | in the Si wafer due to the Pb/Sn bump reflow process                                         |       |

|              | near the interface of the Si and metal/passivation                                           |       |

|              | layers due to the Pb/Sn bump reflow process.                                                 |       |

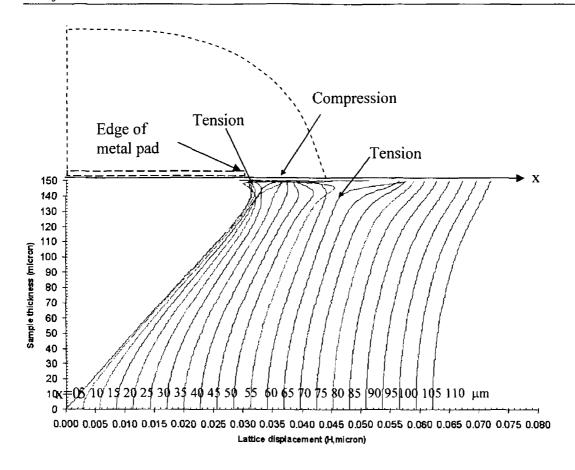

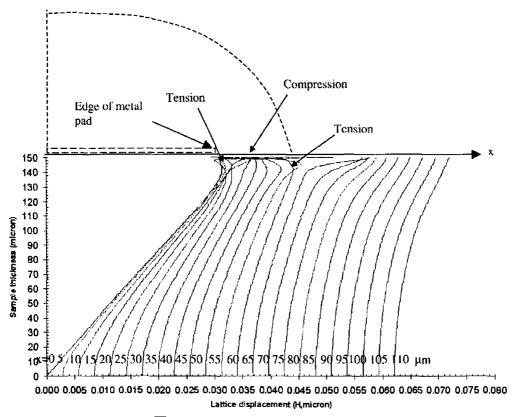

| Figure 5- 35 | The simulated displacement of the $\overline{3}$ $\overline{3}$ 9 lattice planes             | 142   |

|              | calculated for a selected region of the simulated Si under                                   |       |

|              | the periphery of the Pb/Sn bump.                                                             |       |

| Figure 5-36  | An overlay of the dimensions used in the FEM                                                 | 142   |

|              | simulation upon the $\overline{3}\overline{3}9$ BRST image of the left                       |       |

|              | hand side Pb/Sn bump of Fig. 5-23(b).                                                        |       |

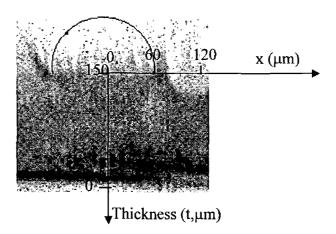

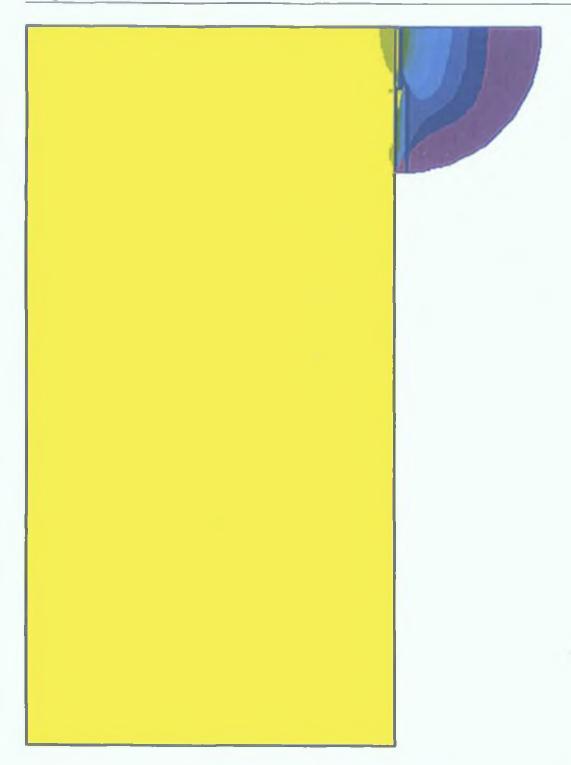

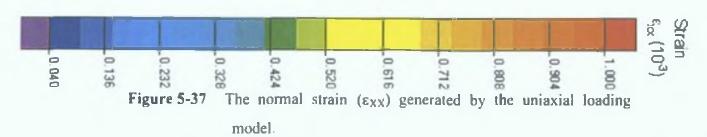

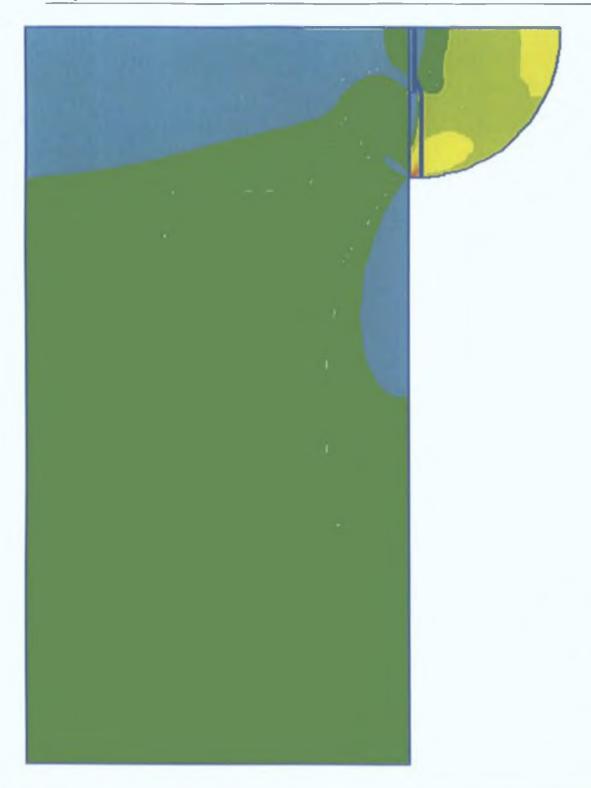

| Figure 5- 37 | The normal strain $(\varepsilon_{XX})$ generated by the uniaxial loading.                    | 143   |

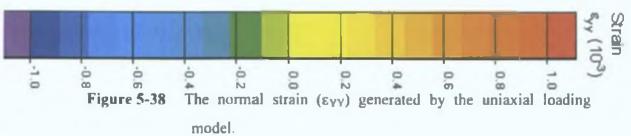

| Figure 5- 38 | The normal strain $(\epsilon_{YY})$ generated by the uniaxial loading.   | 144  |

|--------------|--------------------------------------------------------------------------|------|

| Figure 5- 39 | The shear strain $(\varepsilon_{XY})$ generated by the uniaxial loading. | 145  |

| Figure 5- 40 | The BRST of the post-reflowed sample (Fig. 3-23(b))                      | 146  |

|              | and shear strain contours calculated using the FEM simulat               | ion. |

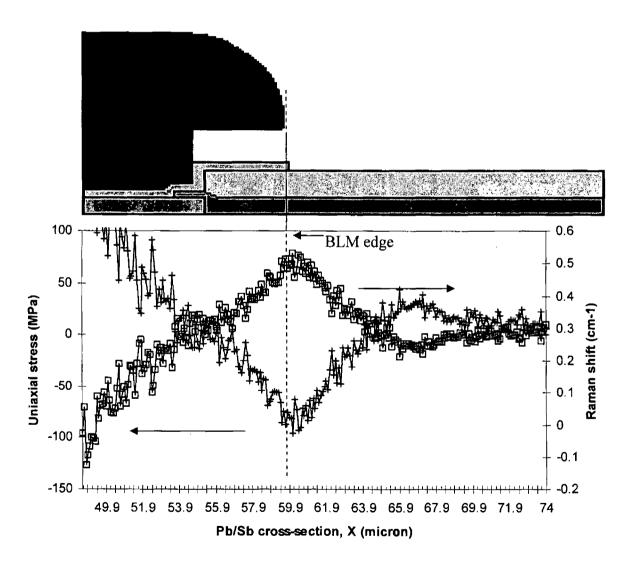

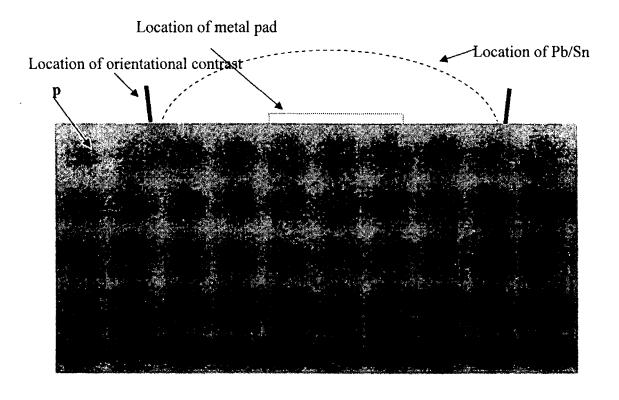

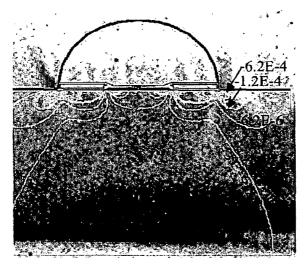

| Figure 5- 41 | The normal stress $(\sigma_{xx})$ and the Raman shift $(cm^{-1})$        | 148  |

|              | of the Pre- reflowed process sample (Ref#URS83a1).                       |      |

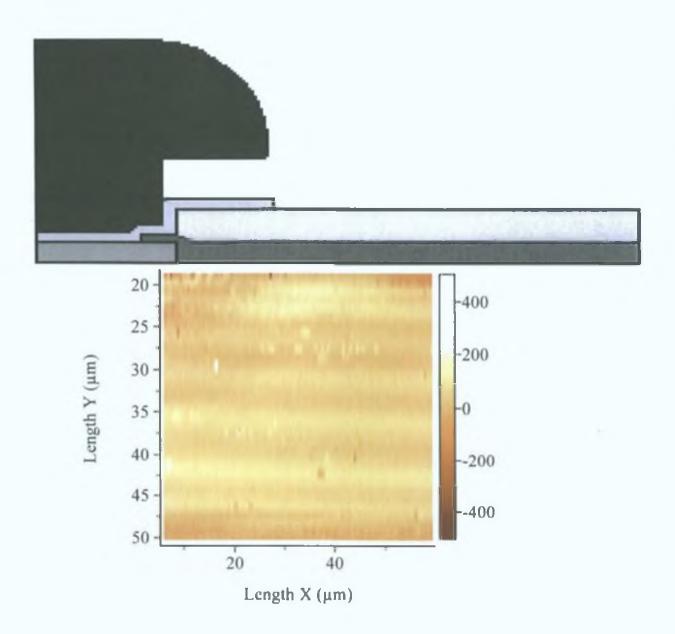

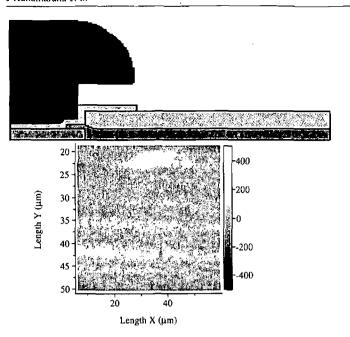

| Figure 5- 42 | The 2-D uniaxial stress of the Pre-reflowed process                      | 149  |

|              | sample. Note that the negative sign and positive sign refer              | to   |

|              | compressive and tensile stresses, respectively (Ref#URS90                | b).  |

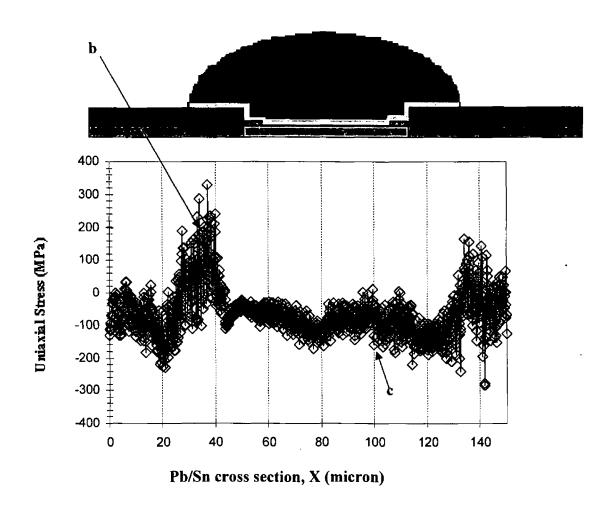

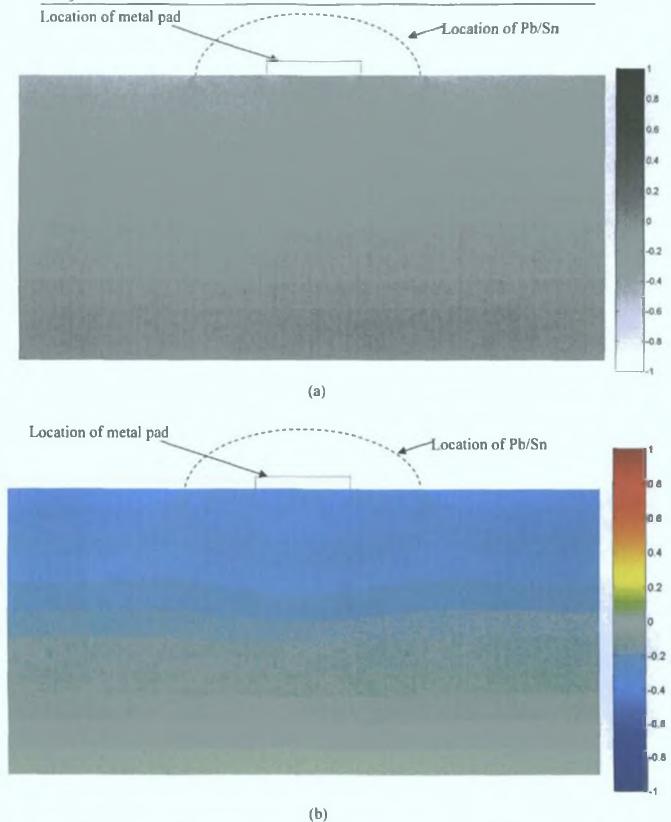

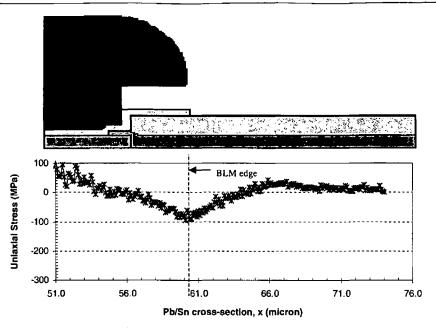

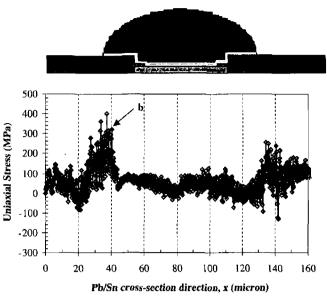

| Figure 5- 43 | The Raman shift and calculated uniaxial stress in the                    | 150  |

|              | post-reflowed process sample along the Pb/Sn bump                        |      |

|              | cross-section (X direction) (Ref#URS81a1).                               |      |

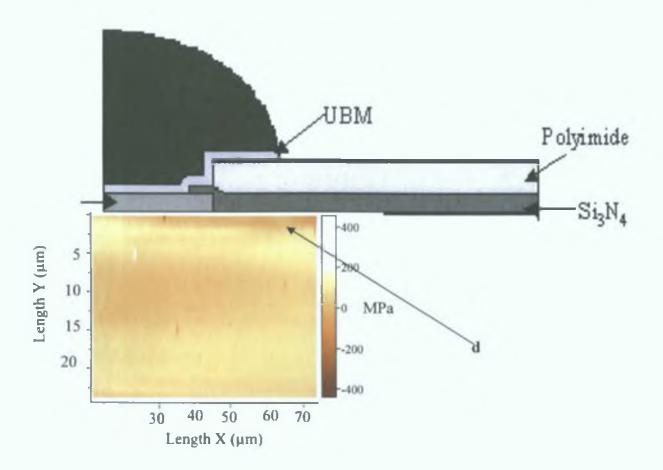

| Figure 5- 44 | The X-Y Raman mapping (2-D) of uniaxial stress                           | 151  |

|              | in the post-reflowed process sample (Ref# URS91a1).                      |      |

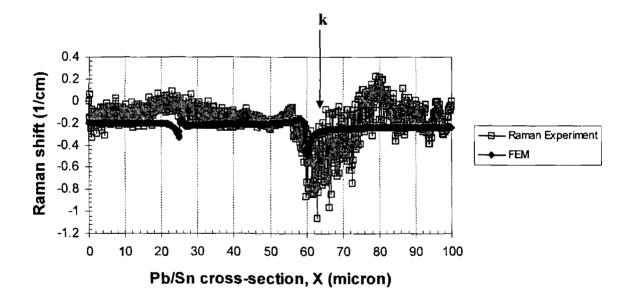

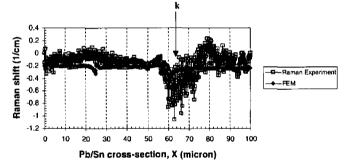

| Figure 5- 45 | Comparison of the Raman shift (cm-1) between                             | 152  |

|              | the micro-Raman experimental data and FEM data.                          |      |

| Figure 5- 46 | BRST image of the post-reflowed process sample                           | 155  |

|              | as a simulating prototype.                                               |      |

| Figure 5- 47 | A part of the BRST image of the post-reflowed process                    | 156  |

|              | sample (Fig. 5-47).                                                      |      |

| Figure 5- 48 | The simulation of g·H using the Meieran and Blech:                       | 158  |

|              | Black and white contrast, and (b) Blue and red                           |      |

|              | colours represent white and black contrasts, respectively.               |      |

| Figure 5- 49 | The BRST simulation of the cos (g.H) calculation:                        | 160  |

|              | black and white scale, and (b) colour scale represents                   |      |

|              | the black and white image.                                               |      |

| Figure 5- 50 | The plot of the strain gradients in terms of the effective               | 162  |

|              | misorientation in the reciprocal lattice.                                |      |

| Figure 5- 51 | The BRST image of the post-reflowed process sample.                      | 163  |

|              | The lines represent possible coutours of clearly                         |      |

|              | identifiable orientational contrast. Arrows q and r are                  |      |

|              | orientational contrast coutours/features outside the Pb/Sn               |      |

|              | bump and underneath the Pb/Sn bump, respectively.                                        |           |

|--------------|------------------------------------------------------------------------------------------|-----------|

| Figure 5- 52 | The dimensions of the Pb/Sn sample.                                                      | 164       |

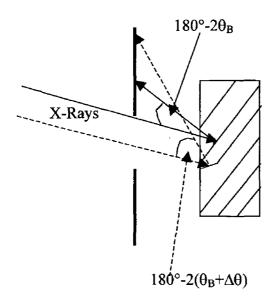

| Figure 5- 53 | The direction and orientation of the lattice plane                                       | 165       |

|              | for the orientational simulation.                                                        |           |

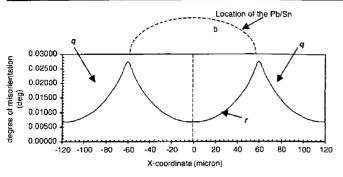

| Figure 5- 54 | The simulation of the principal orientational contrast                                   | 166       |

|              | distortional features in the BRST image of the post-reflower                             | ed sample |

| Figure 5- 55 | A calculation, based on the FEM simulation,                                              | 167       |

|              | of the misorientation $\Delta\theta(x)$ of the $\overline{3}\overline{3}9$ planes in the |           |

| ,            | Si substrate of the post-reflowed process sample                                         |           |

|              | due to the reflow process.                                                               |           |

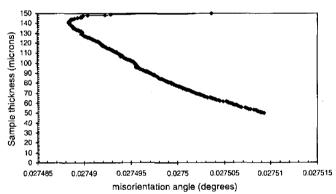

| Figure 5- 56 | The misorientation of the $(\overline{3}\ \overline{3}\ 9)$ Si lattice plane at          | 168       |

|              | the edge of the Pb/Sn bump ( $X = 60 \mu m$ ), as a function of                          |           |

|              | depth into the Si, due to the reflow process.                                            |           |

| Figure 6- 1  | (a) conductor and (b) capacitor.                                                         | 172       |

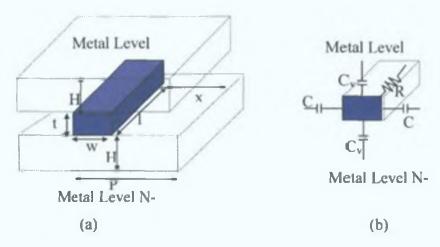

| Figure 6- 2  | (a) dimension and (b) electrical representations                                         | 173       |

|              | of 3 layers of metal in multilevel interconnect device.                                  |           |

|              | The metal line in level N is separated from the metal line                               |           |

|              | in level N+1 and N-1 by the ILD with thickness H. It is                                  |           |

|              | noted that $t = $ thickness, $w = $ width and $l = $ length of the                       |           |

|              | metal line in level N. P is the metal pitch and the spacing                              |           |

|              | between adjacent lines is x. For the electrical representation                           | n,        |

|              | the capacitance of the ILD layer is composed of a lateral                                |           |

|              | capacitance associated with the adjacent lines in the same                               |           |

|              | level and a vertical capacitance associated with the metal                               |           |

|              | lines in levels N+1 and N-1.                                                             |           |

| Figure 6-3   | RC constant versus line width for a 2.0 μm AlCu pitch.                                   | 175       |

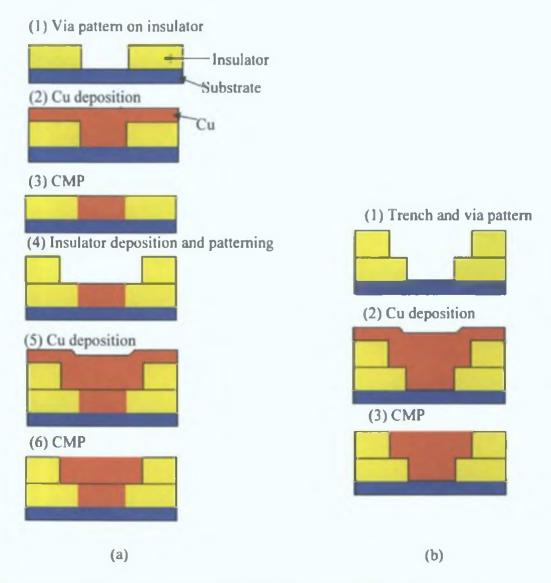

| Figure 6- 4  | (a) Single Damascene and (b) Dual Damascene                                              | 180       |

|              | process outline.                                                                         |           |

| Figure 6-5   | The lift-off pattern process.                                                            | 194       |

| Figure 6- 6  | The damascene pattern process.                                                           | 195       |

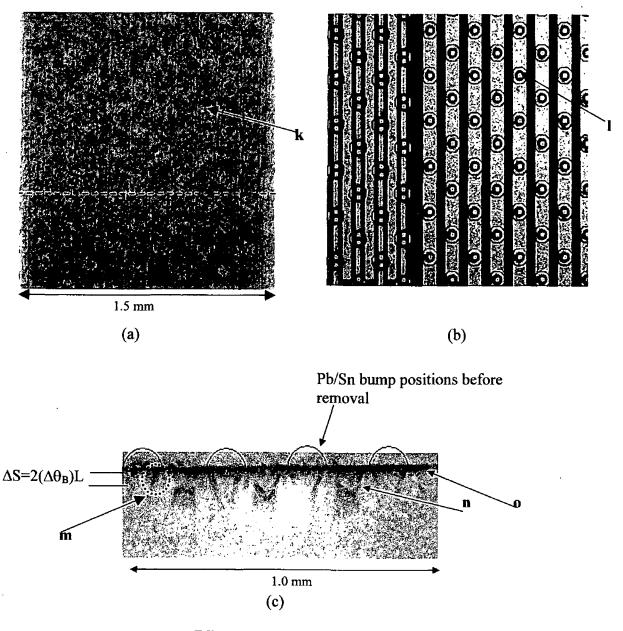

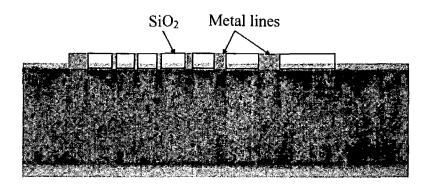

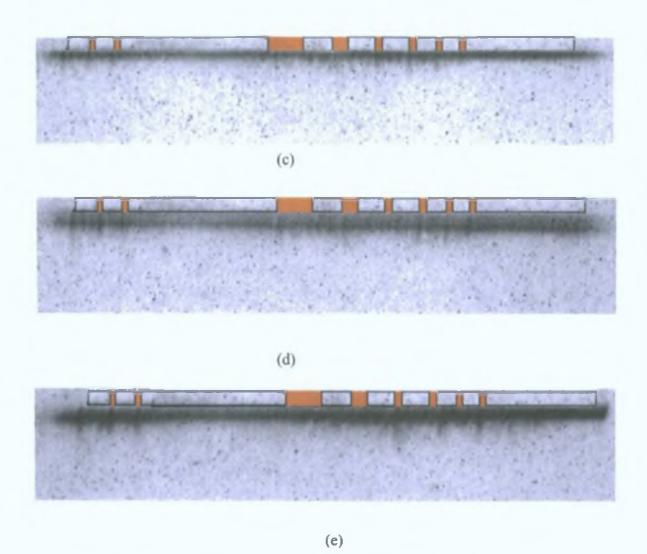

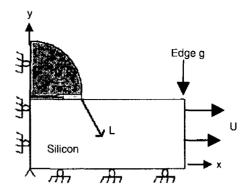

| Figure 6-7   | Geometry and boundary conditions for the post-Cu                             | 199 |

|--------------|------------------------------------------------------------------------------|-----|

|              | metallisation sample model.                                                  |     |

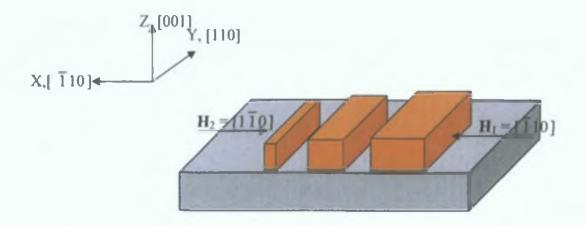

| Figure 6-8   | The geometry and orientation of the Cu lines for                             | 201 |

|              | MRS measurement.                                                             |     |

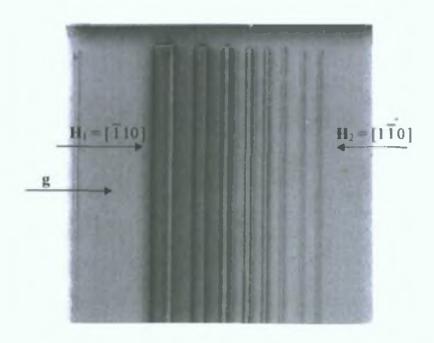

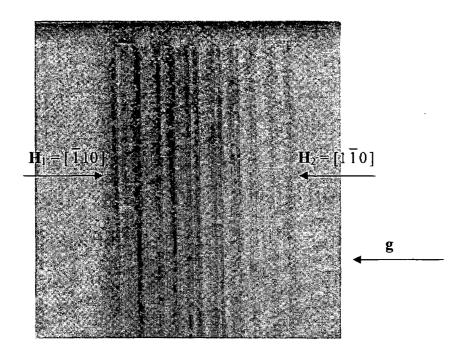

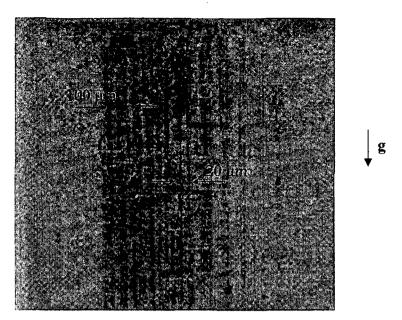

| Figure 6- 9  | Direction of the electroless Cu metallisation.                               | 203 |

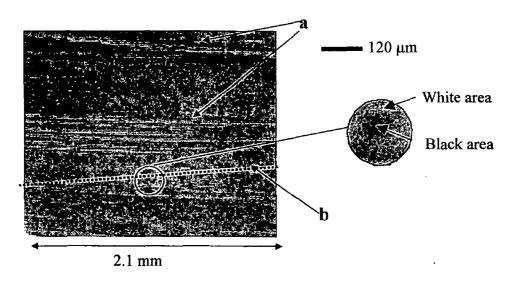

| Figure 6- 10 | The LAT image from 300 nm electroless                                        | 204 |

|              | Cu/ 30 nm Au/ 20 nm Cr/ Si.                                                  |     |

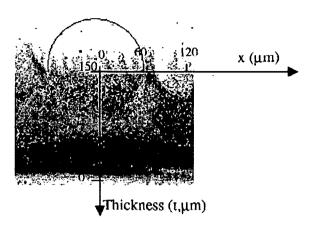

| Figure 6- 11 | Strain in silicon wafer cross section.                                       | 205 |

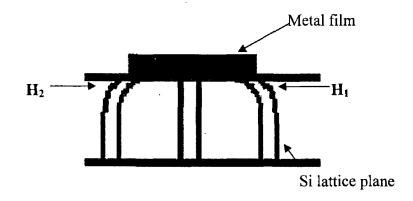

| Figure 6- 12 | Metal places the Si in compression warping the lattice                       | 205 |

|              | lanes near the metal edges as shown. H <sub>1</sub> and H <sub>2</sub> point |     |

|              | along the direction of distortion of the Si lattice as shown.                |     |

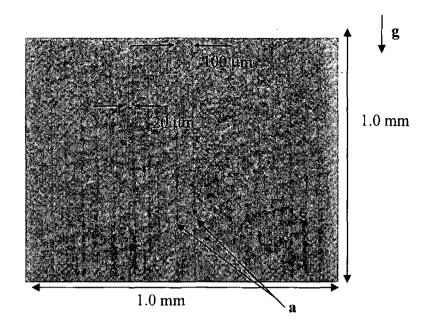

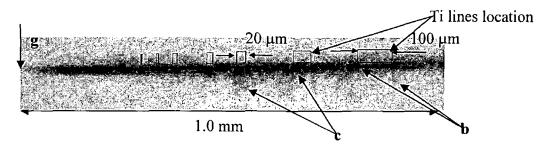

| Figure 6- 13 | The orientation of the Cu metal lines on the Si sample                       | 206 |

| •            | (S#100).                                                                     |     |

| Figure 6- 14 | LA-BRT image of the Cu metallisation sample taken                            | 206 |

|              | from 228 reflection (Ref#R30F328-10).                                        |     |

| Figure 6- 15 | LA-BRT image of the Cu metallisation sample taken                            | 207 |

|              | from 228 reflection (Ref#R30F328-11).                                        |     |

| Figure 6- 16 | LA-BRT image of 100 nm thick Ti on Si wafer without                          | 209 |

|              | photoresist removal (B1, 2a: ref#R30F67-1).                                  |     |

| Figure 6- 17 | BRST image of 100 nm thick Ti lines on Si wafer                              | 210 |

|              | (B1,2a: ref#R30F70-1).                                                       |     |

| Figure 6- 18 | LA-BRT of 20 nm Cu seed layer/ 100 nm Ti lines on Si                         | 211 |

|              | wafer (wfr.D4P3d: ref#R30F354-2).                                            |     |

| Figure 6- 19 | BRST image of 20 nm Cu seed layer/100 nm Ti lines                            | 211 |

|              | on Si wafer (wfr.D4P3d:ref#R30F358-4).                                       |     |

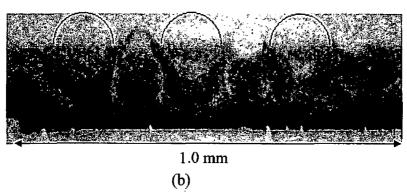

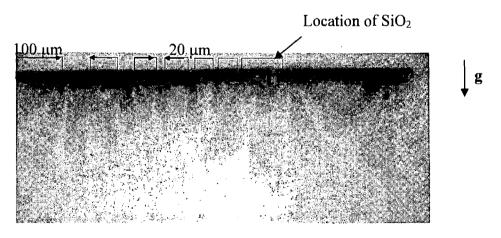

| Figure 6- 20 | LA-BRT image of 300 nm electroless Cu/20 nm Cu seed/                         | 212 |

|              | 100 nm Ti lines on Si wafer (wfr.D4P3d1: ref#R30F315-2)                      |     |

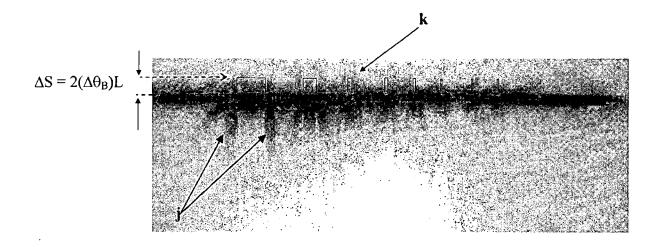

| Figure 6- 21 | BRST image of 300 nm electroless Cu/20 nm Cu seed/                           | 213 |

|              | 100 nm Ti lines on Si wafer (wfr.D4P3d1: ref#R30F318-3)                      | ٠.  |

| Figure 6- 22 | LA-BRT image of 300 nm sputtered Cu/ 20 nm Cu                                | 213 |

|              | seed Cu/ 100 nm Ti on Si wafer (wfr. B1,                                     |     |

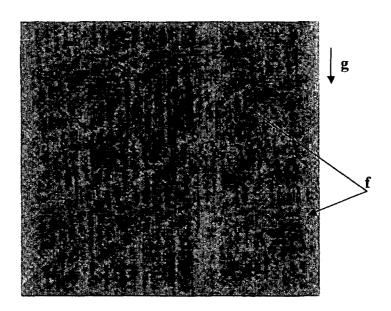

|              | 4F: ref# R30f352-1).                                                         |     |

| Figure 6- 23 | BRST image of 300 nm sputtered Cu/ 20 nm Cu seed Cu/        | 214 |

|--------------|-------------------------------------------------------------|-----|

|              | 100 nm Ti on Si wafer (wfr. B1, 4F: ref# R30f353-6).        |     |

| Figure 6- 24 | LAT image of 20 nm seed Cu/ 100 nm Ti on Si wafer           | 215 |

|              | (wfr.D4P3d: ref# R30F359-1)                                 |     |

| Figure 6- 25 | ST image of 20 nm seed Cu/ 100 nm Ti on Si wafer            | 215 |

|              | (wfr.D4P3d: ref#R30F365-2).                                 |     |

| Figure 6- 26 | LAT image of 300 nm electroless Cu/ 20 nm seed Cu/          | 216 |

|              | 100 nm Ti on Si wafer (wfrD4P3d1: ref#R30F325-1).           |     |

| Figure 6- 27 | ST image of 300 nm electroless Cu/ 20 nm seed Cu/           | 216 |

|              | 100 nm Ti on Si wafer (wfrD4P3d1: ref#R30F327-2).           |     |

| Figure 6- 28 | LAT image of 300 nm sputtered Cu/ 20 nm Cu seed/            | 217 |

|              | 100 nm Ti lines on Si wafer (wfr. B1, 4F: ref#R30F341-1).   |     |

| Figure 6- 29 | ST image of 300 nm sputtered Cu/ 20 nm Cu seed/             | 218 |

|              | 100 nm Ti lines on Si wafer (wfr.B1,4F: ref#R30F344-2).     |     |

| Figure 6- 30 | LA-BRT image of RIE etching on SiO <sub>2</sub> on Si wafer | 219 |

|              | (wfr.DCU12: ref#R30F406-5).                                 |     |

| Figure 6- 31 | BRST image of RIE etching on SiO <sub>2</sub> on Si wafer   | 219 |

|              | (wfr. DCU12: ref#R30f409-2).                                |     |

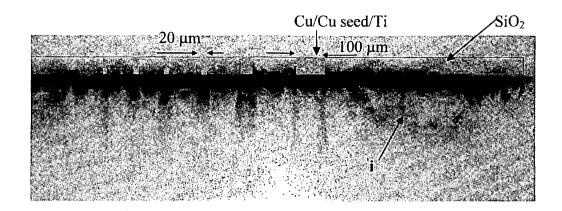

| Figure 6- 32 | LA-BRT image of 300 nm electroless Cu/ 20 nm Cu seed/       | 220 |

|              | 100 nm Ti on damascene pattern after CMP process            |     |

|              | (wfr.DCU2: ref#R30F378-2).                                  |     |

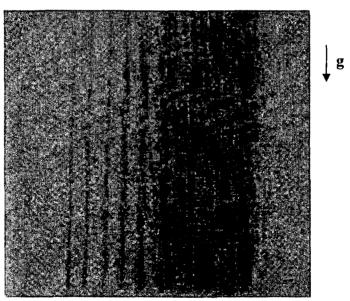

| Figure 6-33  | BRST image of 300 nm electroless Cu/ 20 nm Cu seed/         | 221 |

|              | 100 nm Ti on damascene pattern after CMP process            |     |

|              | (wfr. DCU2: ref#R30F382-4).                                 |     |

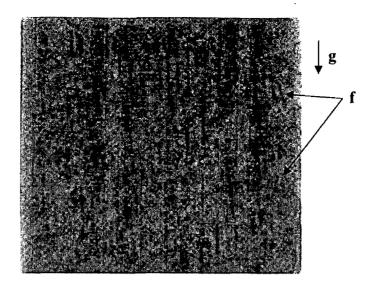

| Figure 6- 34 | LA-BRT image of 300 nm sputtered Cu/ 20 nm Cu seed/         | 222 |

|              | 100 nm Ti on damascene pattern after CMP process            |     |

|              | (wfrDCU10: ref#R30F366-2).                                  |     |

| Figure 6-35  | BRST image of 300 nm sputtered Cu/ 20 nm Cu seed/           | 222 |

|              | 100 nm Ti on damascene pattern after CMP process            |     |

|              | (wfrDCU10: ref#R30F370-4).                                  |     |

| Figure 6- 36 | LAT image of RIE etched on SiO <sub>2</sub> on Si wafer     | 223 |

|              | (wfr. DCU12; ref#R30F405-1).                                |     |

| Figure 6-37  | ST image of RIE etched on SiO <sub>2</sub> on Si wafer         | 224    |

|--------------|----------------------------------------------------------------|--------|

|              | (wfr. DCU12: ref#R30F411-2).                                   |        |

| Figure 6-38  | LAT image of 300 nm electroless Cu/ 20 nm Cu seed/             | 225    |

|              | 100 nm Ti on damascene pattern (wfr. DCU2: ref# r36f121        | l).    |

| Figure 6- 39 | ST image of 300 nm electroless Cu/ 20 nm Cu seed/              | 225    |

|              | 100 nm Ti on damascene pattern (wfr. DCU2: ref# r30f392        | 2-1).  |

| Figure 6- 40 | LAT of 300 nm electroless Cu/ 20 nm Cu seed/                   | 226    |

|              | 100 nm Ti on damascene pattern (wfr.DCU10: ref#R30F37          | 71-1). |

| Figure 6- 41 | LAT of 300 nm electroless Cu/ 20 nm Cu seed/                   | 227    |

|              | 100 nm Ti on damascene pattern (wfrDCU10: ref#R30F37           | 7a-2). |

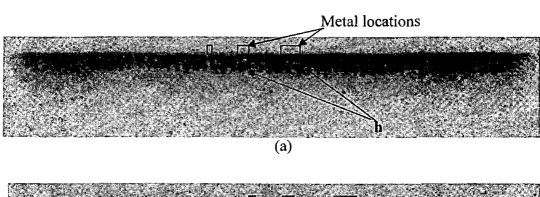

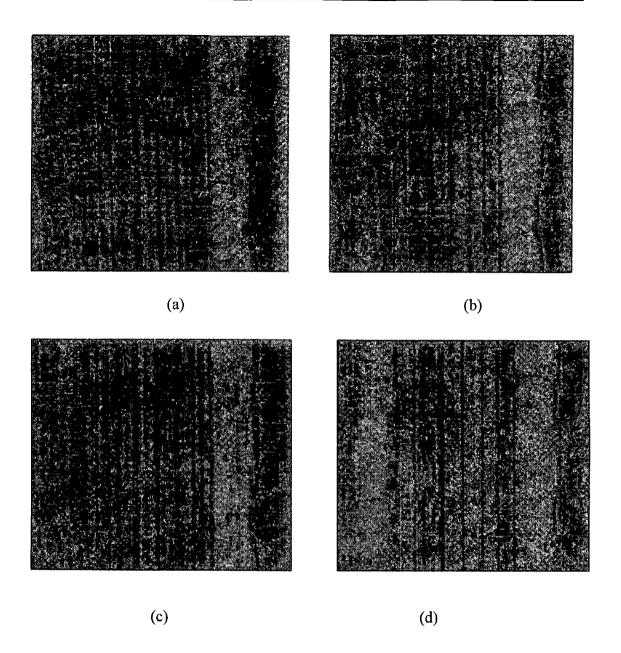

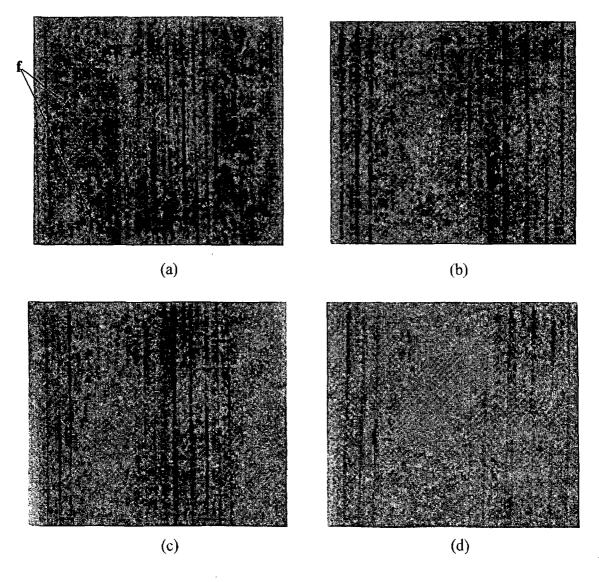

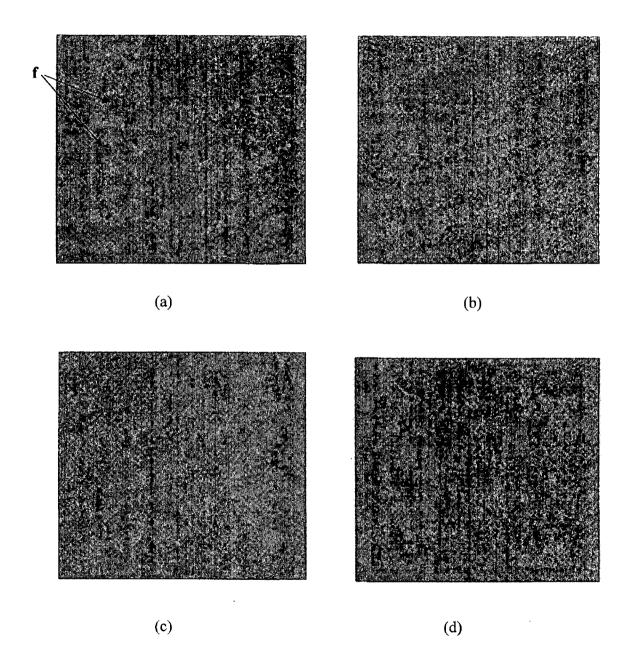

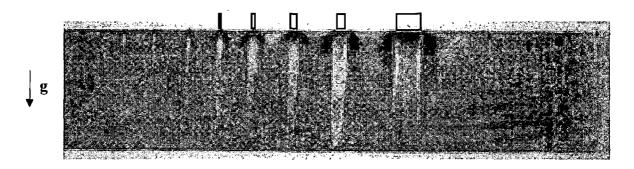

| Figure 6- 42 | BRT images for <i>Pre</i> -metallisation step (20 nm Cu seed/  | 229    |

|              | 100 nm Ti on Si wafer) at (a) RT, (b) 100 °C, (c) 200°C,       |        |

|              | 300°C and (e) 400°C (wfr. D4P3D: ref # r36f38, r36f40,         |        |

|              | r36f42, r36f44 and r36f46).                                    |        |

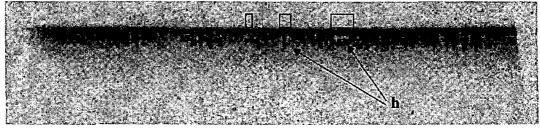

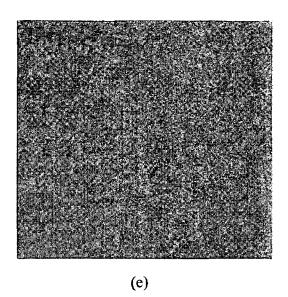

| Figure 6-43  | BRST images for <i>Pre</i> -metallisation step (20 nm Cu seed/ | 230    |

|              | 100 nm Ti on Si wafer) at (a) RT, (b) 100 °C, (c) 200°C,       |        |

|              | 300°C and (e) 400°C (wfr. D4P3D: ref # r36f39, r36f41,         |        |

|              | r36f43, r36f45 and r36f47).                                    |        |

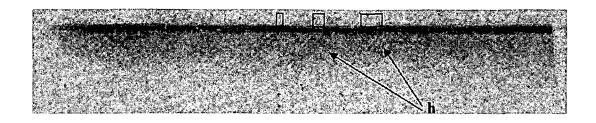

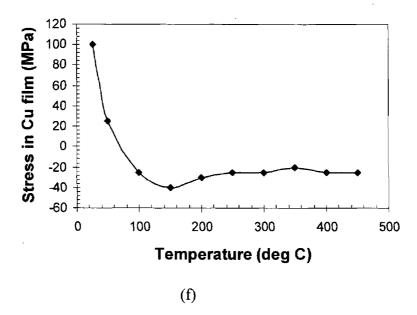

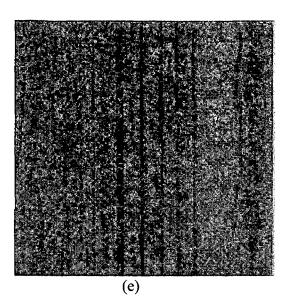

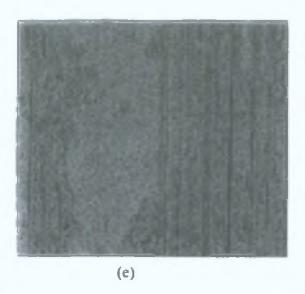

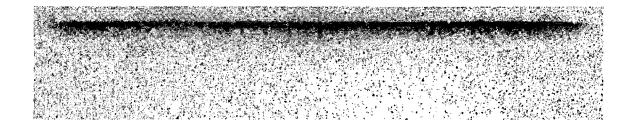

| Figure 6- 44 | LA-BRT images for <i>Post</i> -metallisation step (300 nm      | 232    |

|              | electroless Cu/ 20 nm Cu seed/ 100 nm Ti on Si wafer)          |        |

|              | at (a) RT, (b) 100 °C, (c) 200 °C, (d) 300 °C, (e) 400 °C      |        |

|              | (wfr. D4P3D: ref # r36f5-1, r36f9, r36f11, r36f13              |        |

|              | and r36f15) and (f) the stress in Cu film from Reidel et al.   |        |

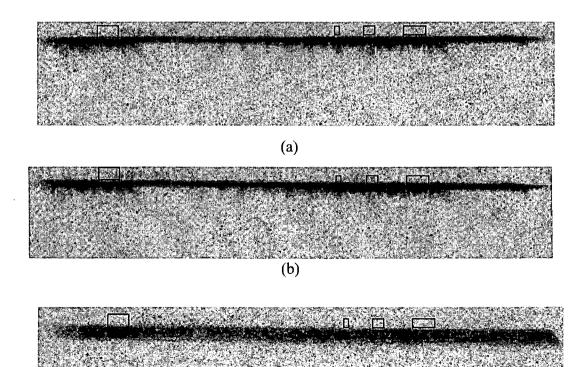

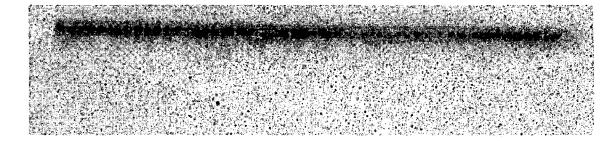

| Figure 6- 45 | LA-BRT images of Post-metallisation                            | 235    |

|              | (300 nm sputtered Cu/ 20 nm Cu seed/ 100 nm Ti on              |        |

|              | Si wafer) at temperature (a) RT, (b) 100°C, (c) 200°C,         |        |

|              | 300°C and (e) 400°C (wfr. B1,4F: ref # r36f18, r36f20,         |        |

|              | r36f22, r36f24 and r36f26).                                    |        |

| Figure 6- 46 | BRST images of the Post-metallisation sample                   | 236    |

|              | (300 nm sputtered Cu/ 20 nm Cu seed/ 100 nm Ti on Si wa        | fer)   |

|              | at (a) RT, (b) 100°C, (c) 200°C and (d) 300°C (wfr. B1,4F      | :      |

|              | ref # r36f19, r36f21, r36f23 and r36f25).                           |       |

|--------------|---------------------------------------------------------------------|-------|

| Figure 6- 47 | LA-BRT of the <i>Pre</i> -Cu metallisation sample                   | 238   |

|              | (SiO <sub>2</sub> pattern on Si wafer) at (a) RT, (b) 100, (c) 200, |       |

|              | 300 and (e) 400 °C (wfr.DCU12: ref#r36f83, r36f85,                  |       |

|              | r36f87, r36f89 and r36f91).                                         |       |

| Figure 6- 48 | BRST images of the Pre-Cu metallisation sample                      | 239   |

|              | (SiO <sub>2</sub> pattern on Si wafer) at (a) RT, (b) 100, (c) 200, |       |

|              | 300 and (e) 400°C (wfr.DCU12: ref#r36f84, r36f86,                   |       |

|              | r36f88, r36f90 and r36f92).                                         |       |

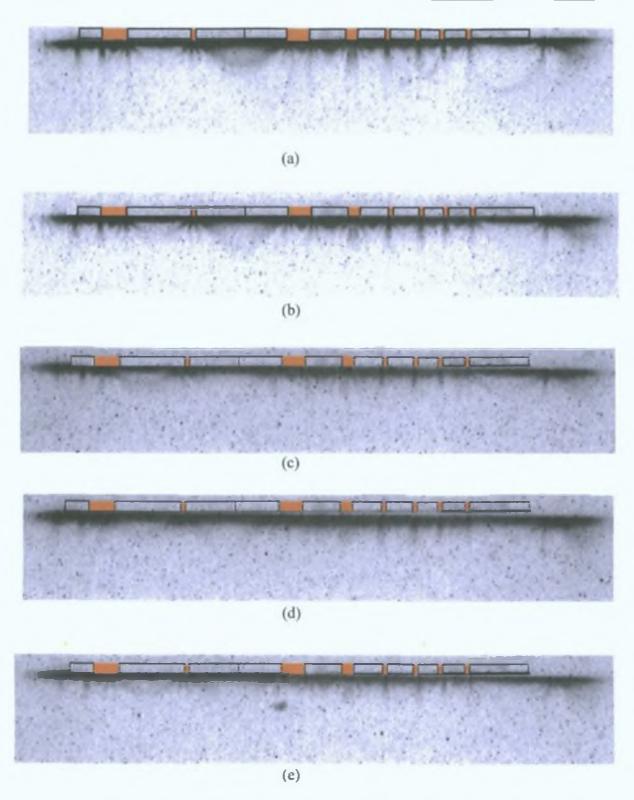

| Figure 6- 49 | LA-BRT images of the Post-Cu metallisation sample                   | 241   |

|              | (300 nm electroless Cu/ 20 nm Cu seed/ 100 nm Ti                    |       |

|              | on damascene patterned Si wafer) at (a) RT, (b) 100, (c) 20         | 0,    |

|              | 300 and (e) 400°C (wfr.DCU2: ref#r36f95, r36f97, r36f99,            | ,     |

|              | r36f101 and r36f103).                                               |       |

| Figure 6- 50 | BRST images of the Post-Cu metallisation sample                     | 242   |

|              | (300 nm electroless Cu/ 20 nm Cu seed/ 100 nm Ti on                 |       |

|              | damascene patterned Si wafer) at (a) RT, (b) 100, (c) 200,          |       |

|              | (d) 300 and (e) 400°C (wfr.DCU2: ref#r36f95, r36f97, r36f           | f99,  |

|              | r36f101 and r36f103).                                               |       |

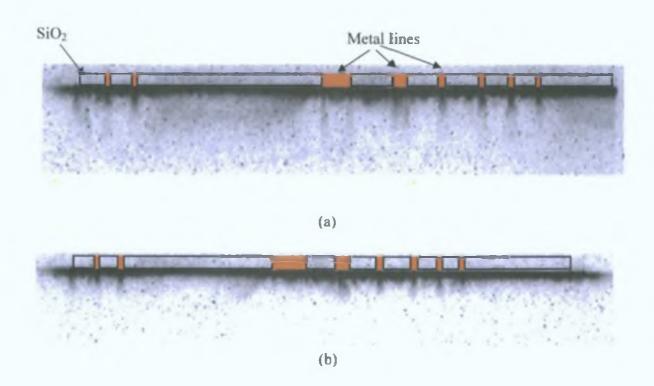

| Figure 6- 51 | LA-BRT images of the Post-Cu metallisation sample                   | 244   |

|              | (300 nm sputtered Cu/ 20 nm Cu seed/ 100 nm Ti on                   |       |

|              | damascene patterned Si wafer) at (a) RT, (b) 100, (c) 200,          |       |

|              | (d) 300 and (e) 400°C (wfr.DCU10: ref#r36f73, r36f75, r36           | 6f77, |

|              | r36f79 and r36f81).                                                 |       |

| Figure 6- 52 | BRST images of the Post-Cu metallisation sample                     | 245   |

|              | (300 nm sputtered Cu/ 20 nm Cu seed/ 100 nm Ti on                   |       |

|              | damascene patterned Si wafer) at (a) RT, (b) 100, (c) 200,          |       |

|              | (d) 300 and (e) 400°C (wfr. DCU10: ref#r36f74, r36f76,              |       |

|              | r36f78, r36f80 and r36f82).                                         |       |

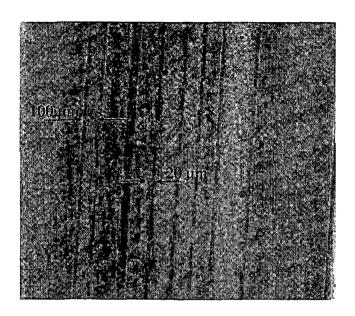

| Figure 6- 53 | LA-BRT of 500nm Post-electroless Cu metallisation/                  | 246   |

|              | 20 nm Cu seed/ 100 nm Ti on Si using lift-off pattern               |       |

|              | (wfr. D4P3c: ref#R30F328-2).                                                       |     |

|--------------|------------------------------------------------------------------------------------|-----|

| Figure 6- 54 | BRST of 500nm Post-electroless Cu metallisation/                                   | 247 |

|              | 20 nm Cu seed/ 100 nm Ti on Si using lift-off pattern                              |     |

|              | (wfr. D4P3c: ref#R30F332-8).                                                       |     |

| Figure 6- 55 | LAT image of 500nm Post-electroless Cu metallisation/                              | 248 |

|              | 20 nm Cu seed/ 100 nm Ti on Si using lift-off pattern                              |     |

|              | (wfr. D4P3c: ref#R30F338-1).                                                       |     |

| Figure 6- 56 | ST image of 500nm Post-electroless Cu metallisation/                               | 249 |

|              | 20 nm Cu seed/ 100 nm Ti on Si using lift-off pattern                              |     |

|              | (wfr. D4P3c: ref#R30F337-2).                                                       |     |

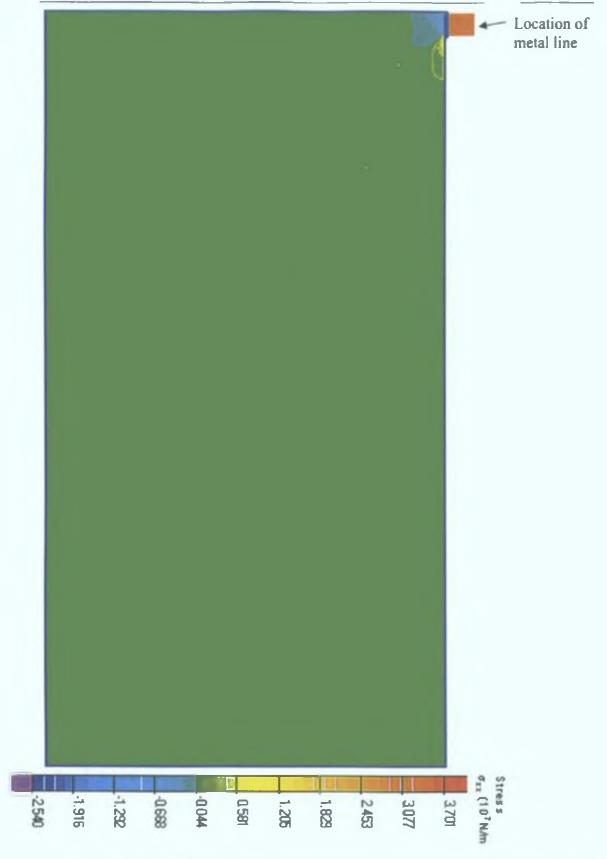

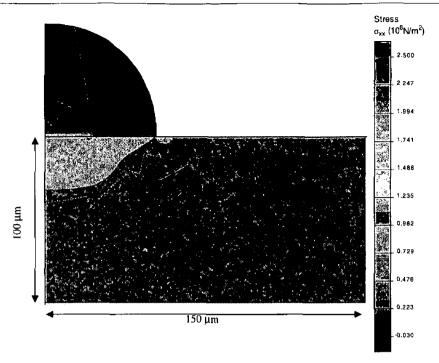

| Figure 6- 57 | FEM of the normal stress in the X-direction $(\sigma_{XX})$ for                    | 251 |

|              | the 20 µm wide Cu metallisation.                                                   |     |

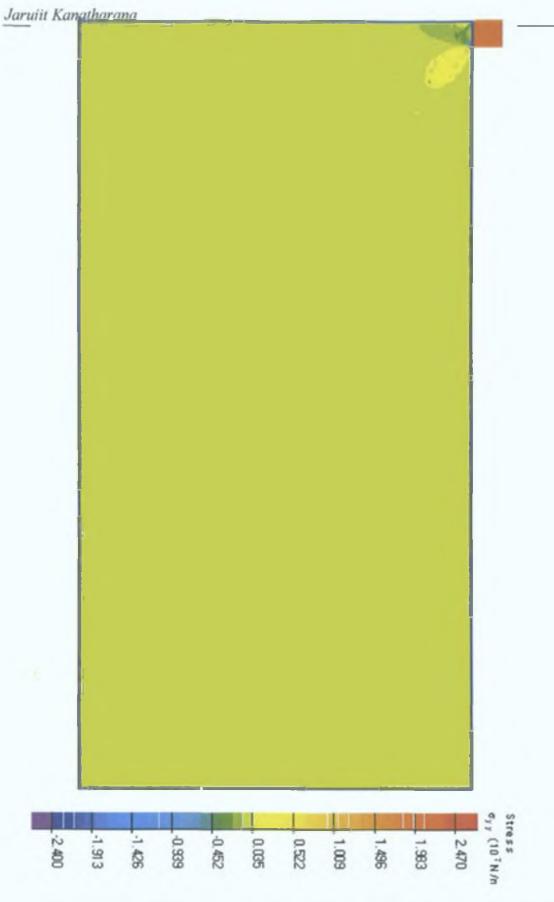

| Figure 6- 58 | FEM of the normal stress in the Y-direction $(\sigma_{yy})$ for                    | 252 |

|              | the 20 µm wide Cu metallisation                                                    |     |

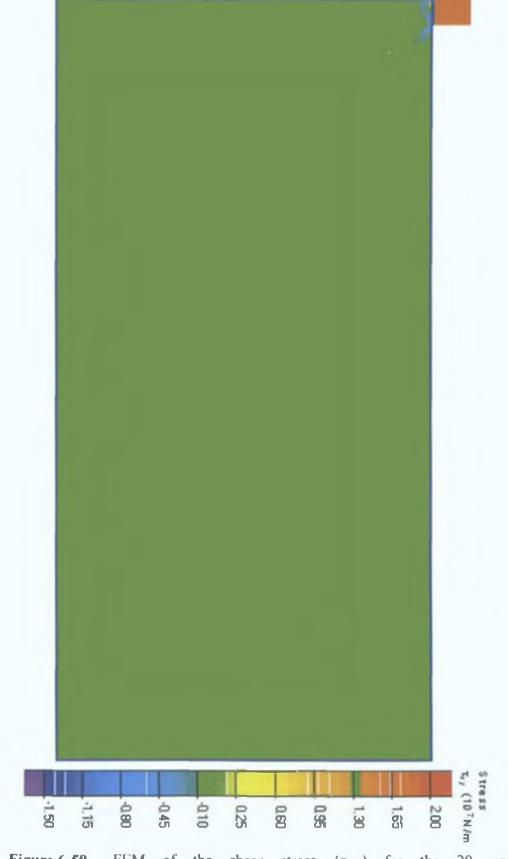

| Figure 6- 59 | FEM of the shear stress $(\tau_{XY})$ for the 20 $\mu m$ wide                      | 253 |

|              | Cu metallisation.                                                                  |     |

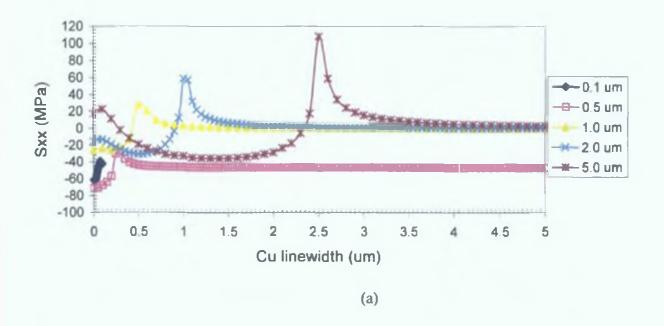

| Figure 6- 60 | The FEM simulation of the normal stress in the X                                   | 254 |

|              | direction ( $\sigma_{XX}$ ) along the Si/metal interface for copper                |     |

|              | line widths of 0.1, 0.5, 1.0, 2.0, 5.0, 10, 20, 40,                                |     |

|              | 60 and 100 μm. Note: positive and a negative signs                                 |     |

|              | represent tensile and compressive stresses, respectively.                          |     |

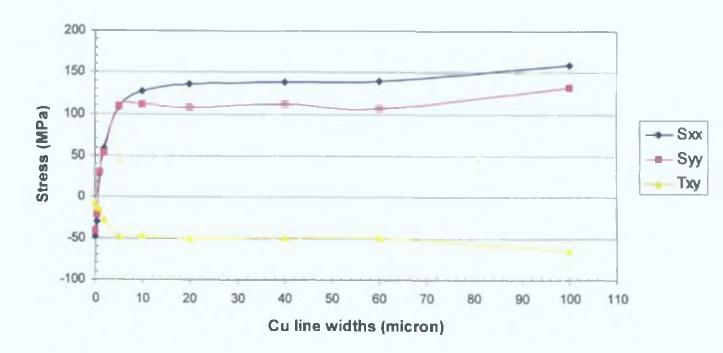

| Figure 6- 61 | The outcome of the FEM simulation of the relationship                              | 255 |

|              | between the normal stresses $(\sigma_{XX}, \sigma_{YY})$ and shear stress          |     |

|              | $(\tau_{XY})$ outside the edge of the metal lines as a function                    |     |

|              | of the copper line widths.                                                         |     |

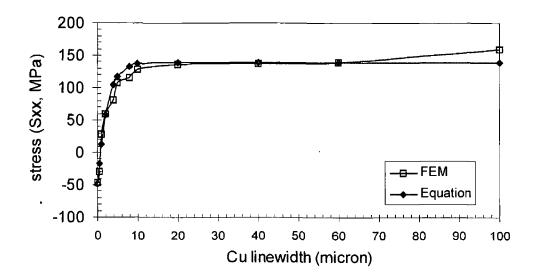

| Figure 6- 62 | A comparison of the normal stress in X direction $(\sigma_{XX})$                   | 256 |

|              | from FEM data and the equation as a function of the Cu                             |     |

|              | line widths.                                                                       |     |

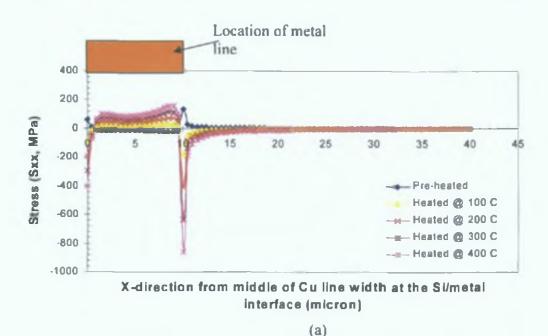

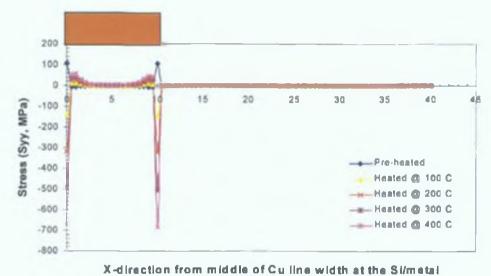

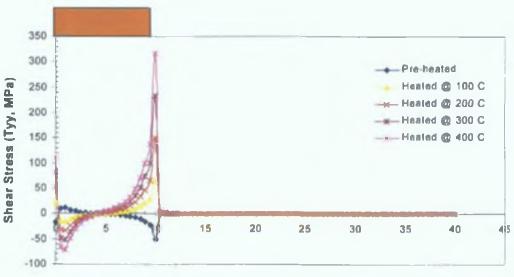

| Figure 6- 63 | The FEM simulation of the induced strains for                                      | 258 |

|              | the <i>Pre</i> - and <i>Post</i> - annealed copper metallisation (a) $\sigma_{XX}$ |     |

|              | $\sigma_{YY}$ and (c) $\tau_{XY}$ along the X-direction from the middle            |     |

|              | of the metal lines ( $X = 0 \mu m$ ) to the edge of the metal                      |     |

|--------------|------------------------------------------------------------------------------------|-----|

|              | (X= 10 $\mu$ m) at the Si/metal interface (Y= 150 $\mu$ m).                        |     |

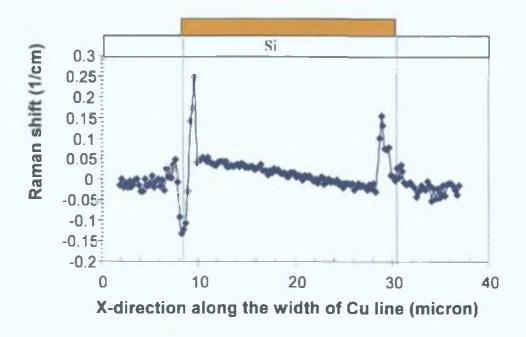

| Figure 6- 64 | (a) The Raman shift (cm <sup>-1</sup> ), and (b) the normal stress                 | 261 |

|              | $(\sigma_{XX},$ MPa) for the 20 $\mu m$ Cu line width $\textit{Pre-metallisation}$ |     |

|              | sample (ref# D4P3d).                                                               |     |

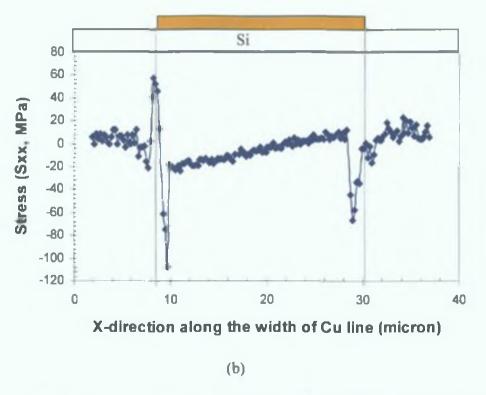

| Figure 6- 65 | (a) Raman shift (cm <sup>-1</sup> ) and (b) Stress ( $\sigma_{XX}$ , MPa) for      | 262 |

|              | the 20 µm Cu line width <i>Post</i> -Cu metallisation sample                       |     |

|              | (Ref# s-97).                                                                       |     |

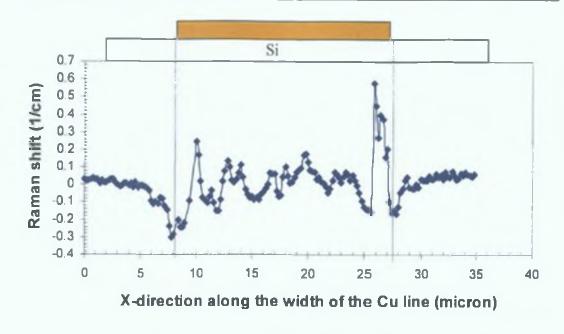

| Figure 6- 66 | (a) Raman shift (cm <sup>-1</sup> ) and (b) Stress, $\sigma_{XX}$ (MPa) of         | 264 |

|              | the 20 $\mu m$ line width sputtered Cu metallisation by lift-off                   |     |

|              | pattern (ref# B1-4F).                                                              |     |

| Figure 6- 67 | The normal stress $(\sigma_{XX})$ in the Si substrate due to                       | 266 |

|              | the 500 nm electroless Cu metallisation as a function of                           |     |

|              | Cu line widths (Pre-annealed sample).                                              |     |

| Figure 6- 68 | The relationship between the normal stresses ( $\sigma_{XX}$ , MPa)                | 267 |

|              | in the Si substrate calculated from the Raman shift and                            |     |

|              | the Cu line widths of the Pre-annealed sample.                                     |     |

| Figure 6- 69 | A comparison of the normal stress in X direction ( $\sigma_{XX}$ )                 | 268 |

|              | from experimental MRS data, the FEM simulation and                                 |     |

|              | the empirical estimations of Eq. 6-32 and Eq. 6-33.                                |     |

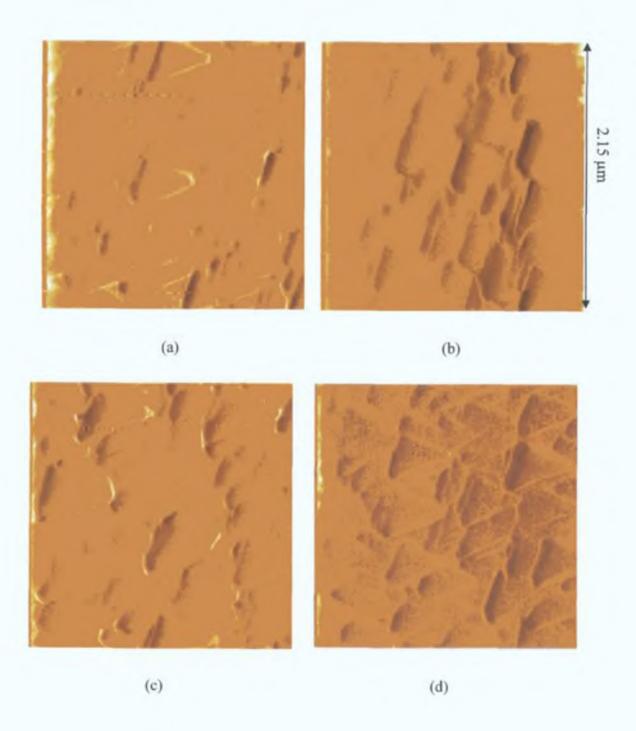

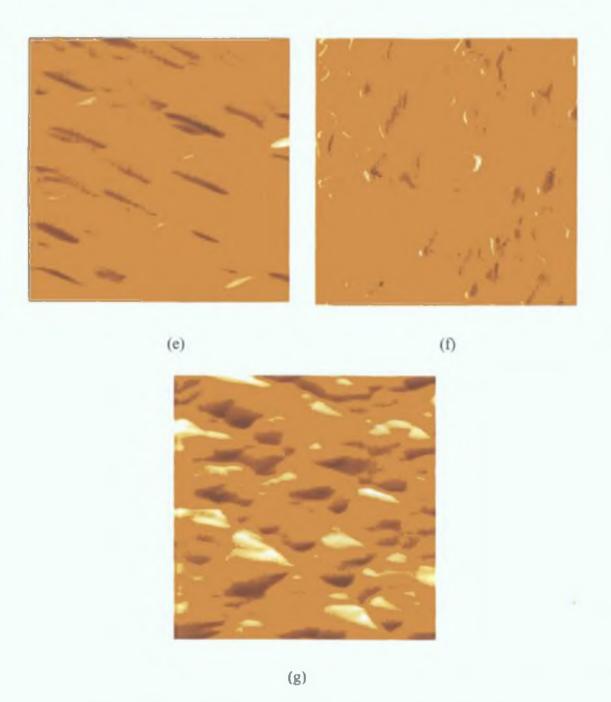

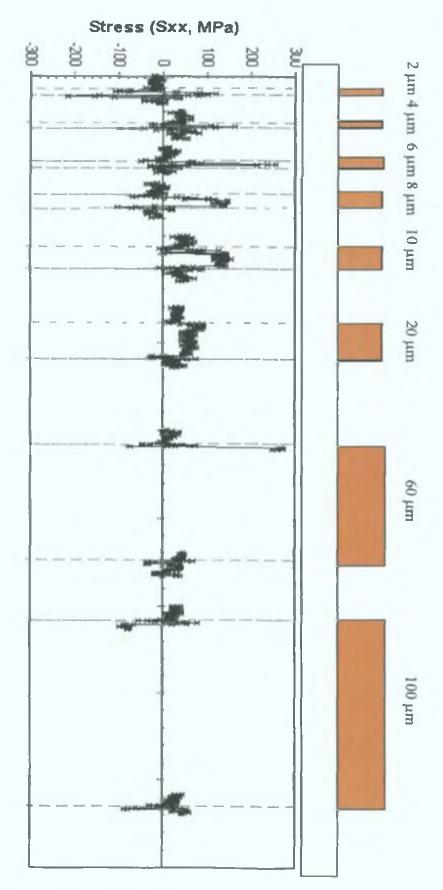

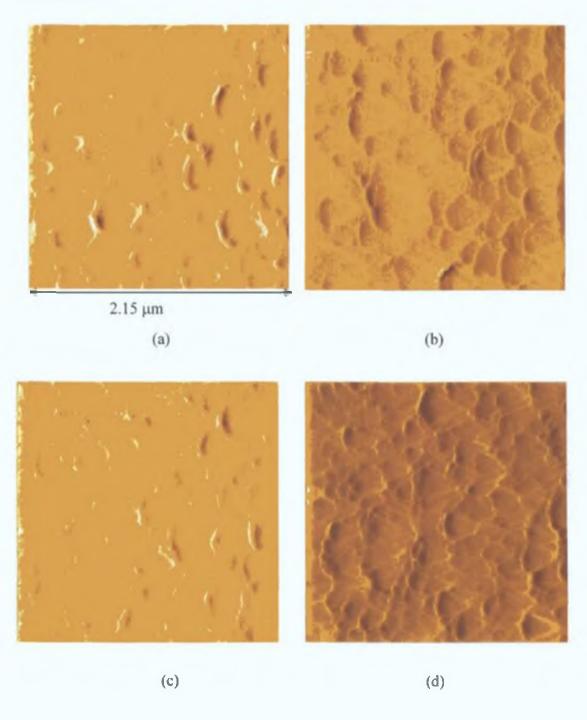

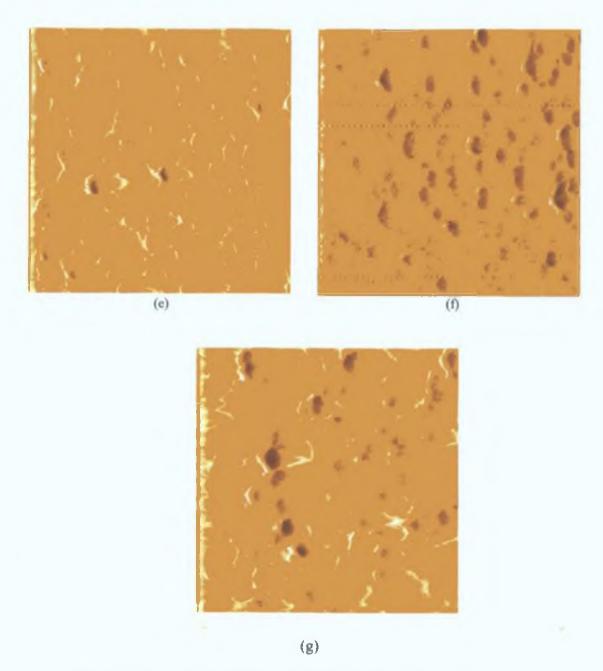

| Figure 6- 70 | AFM results of the electroless Cu as a function of                                 | 271 |

|              | the Cu line widths of (a) 2 μm, (b) 4 μm, (c) 8 μm,                                |     |

|              | (d) 10 $\mu$ m, (e) 20 $\mu$ m, (f) 60 $\mu$ m and (g) 100 $\mu$ m.                |     |

|              | Note: image dimensions: 2.15 μm x 2.15 μm.                                         |     |

| Figure 6- 71 | The normal stress $(\sigma_{XX})$ in the Si substrate due to                       | 273 |

|              | the 500 nm electroless Cu metallisation as a function of Cu                        |     |

|              | line widths after annealing at 400 °C (Post-annealed sample                        | e). |

| Figure 6- 72 | Relationship of the normal stress $(\sigma_{XX})$ in Si imposed due                | 274 |

|              | to the Cu metallisation with the annealing effect and the                          |     |

|              | Cu line width.                                           |     |

|--------------|----------------------------------------------------------|-----|

| Figure 6- 73 | The XRD pattern of the Pre-metallisation (20 nm Cu seed/ | 276 |

|              | 100 nm Ti/Si) sampled, which was annealed at 400 °C.     |     |

| Figure 6- 74 | The XRD pattern of the Post-electroless,                 | 278 |

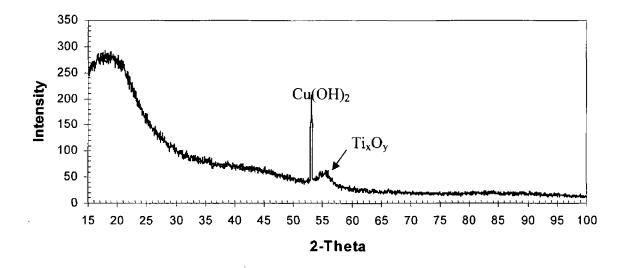

|              | Pre-annealed Cu metallisation sample.                    |     |

| Figure 6- 75 | The XRD pattern of the Post-electroless Cu metallisation | 279 |

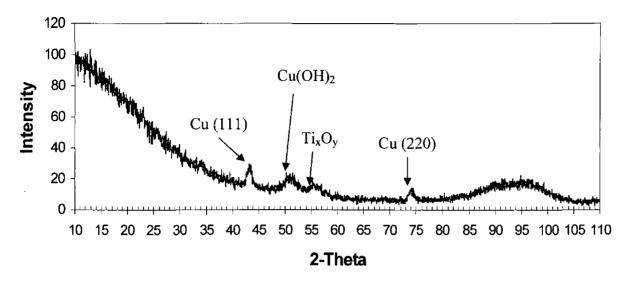

|              | sample, which was annealed at 400 °C.                    |     |

| Figure 6- 76 | The XRD pattern of the Post-sputtered, Pre-annealed Cu   | 280 |

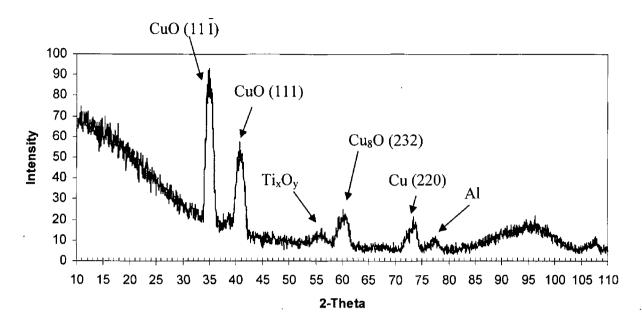

|              | metallisation sample.                                    |     |

| Figure 6- 77 | The XRD pattern of the Post-sputtered Cu metallisation   | 281 |

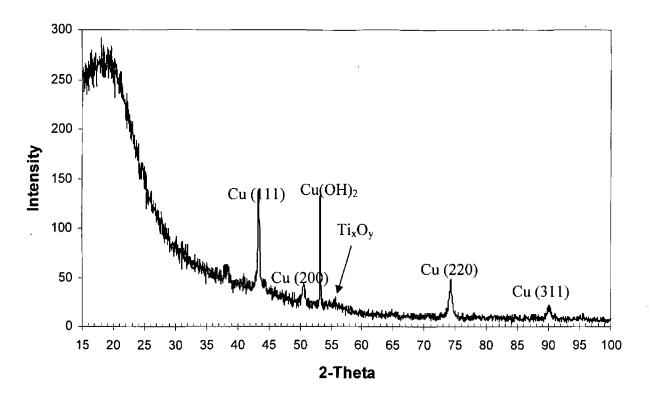

|              | sample after annealing at 400 °C.                        |     |

# TABLE OF TABLES

| <b>Table 2- 1</b> | Sychrotron Radiation Sources.                              | 10  |

|-------------------|------------------------------------------------------------|-----|

| Table 4- 1        | The structural, electronic and vibrational properties      | 78  |

|                   | of some cubic semiconductors at room temperature.          |     |

| Table 4- 2        | Examples of transitions and relative intensities for the   | 92  |

|                   | Ar+ laser lines.                                           |     |

| Table 5-1         | Material properties for finite element analysis.           | 115 |

| Table 6- 1        | The resistivity of metals used in electronic applications. | 176 |

| Table 6- 2        | Relationship between EM performance and Cu metal           | 178 |

|                   | grain size for CVD Cu (200), (111) and electroplated       |     |

|                   | (EP) Cu (111) films.                                       |     |

| Table 6-3         | Electroless Cu deposition rate and resistivity vs.         | 190 |

|                   | deposition bath factors.                                   |     |

| Table 6-4         | The electroless copper deposition solution component.      | 190 |

| Table 6-5         | Types of stress generated in the different metals.         | 193 |

| Table 6-6         | Electroless copper deposition solution components.         | 196 |

| Table 6-7         | Materials properties for finite element analysis.          | 200 |

# **List of Abbreviations**

| $m_0$                     | electron's rest mass                                                |

|---------------------------|---------------------------------------------------------------------|

| c                         | velocity of light                                                   |

| λ                         | x-ray radiation wavelength                                          |

| $\theta_B$                | Bragg angle                                                         |

| k                         | wavevector                                                          |

| $\mathbf{k}_0$            | wavevector outside the crystal in the direction of incident beam    |

| $\mathbf{k}_{\mathbf{H}}$ | wavevector outside the crystal in the direction of diffracted beam  |

| $\mathbf{K}_{0}$          | wavevector inside the crystal in the direction of incident beam     |

| K <sub>H</sub>            | wavevector inside the crystal in the direction of diffracted beam   |

| χ                         | electric susceptibility                                             |

| S                         | Poynting vector                                                     |

| $\mu_0$                   | linear absorption coefficient                                       |

| $\Delta \phi$             | divergence of the incident x-ray beam                               |

| $\Delta\theta_B$          | effective misorientation                                            |

| <b>t</b> <sub>p</sub>     | penetration depth                                                   |

| g                         | the diffraction vector                                              |

| H <sub>i</sub>            | unit vector normal to the film edge and point away from film edge   |

| $\sigma_{i}$              | normal stresses in i direction                                      |

| $	au_{ij}$                | shear stress                                                        |

| $\epsilon_{\rm i}$        | normal strain                                                       |

| γij                       | shear strain                                                        |

| $\boldsymbol{E}$          | Young's modulus                                                     |

| ν                         | Poisson's ratio                                                     |

| $\boldsymbol{G}$          | shear modulus of elasticity                                         |

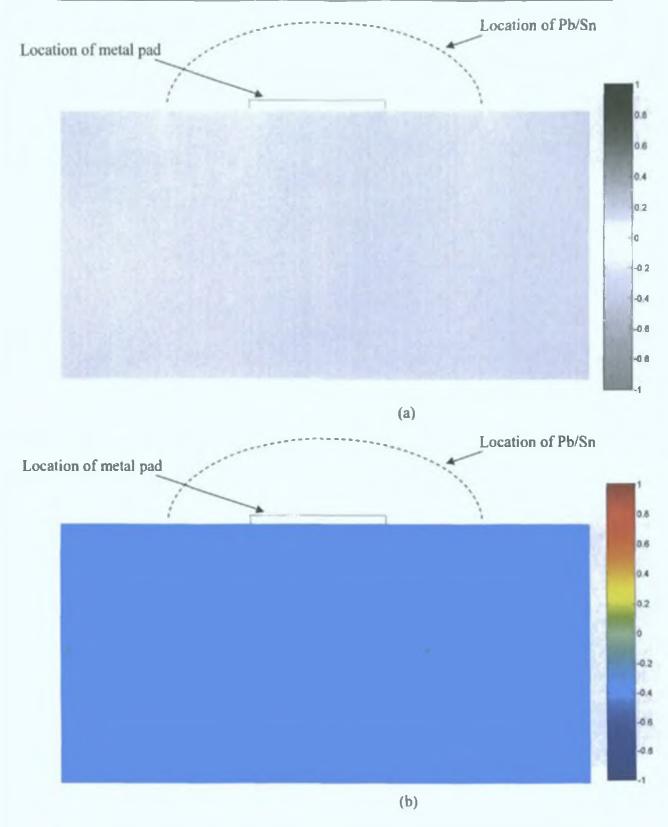

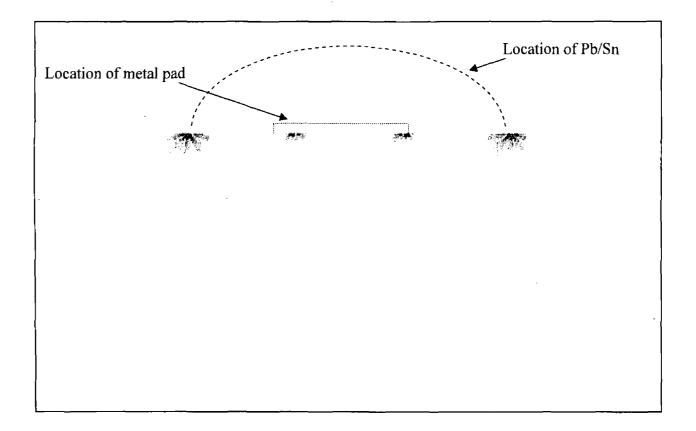

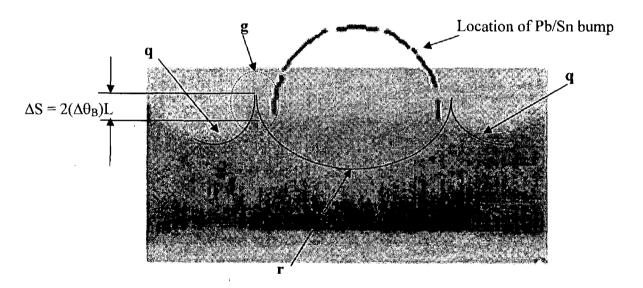

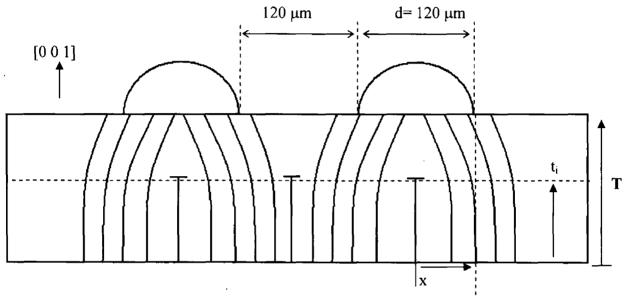

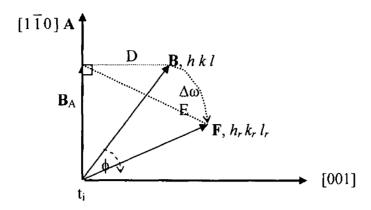

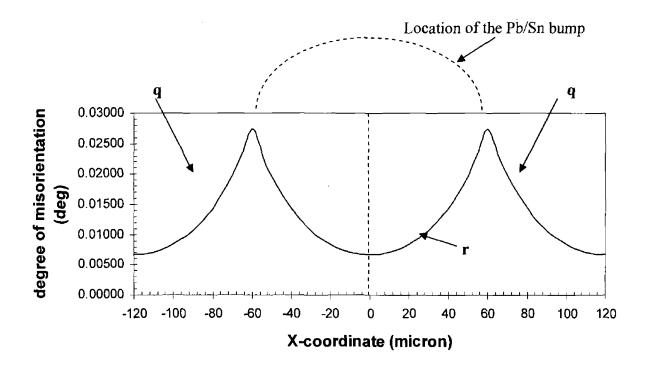

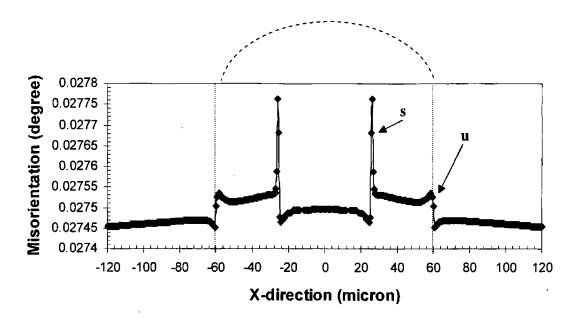

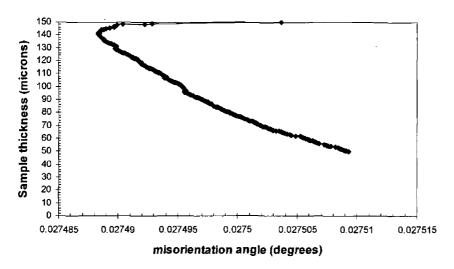

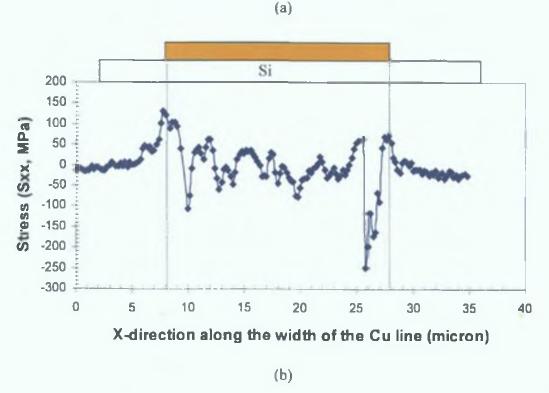

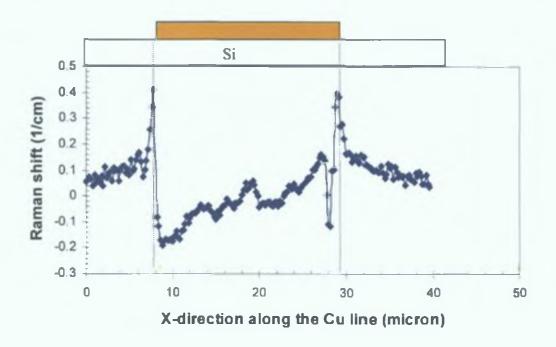

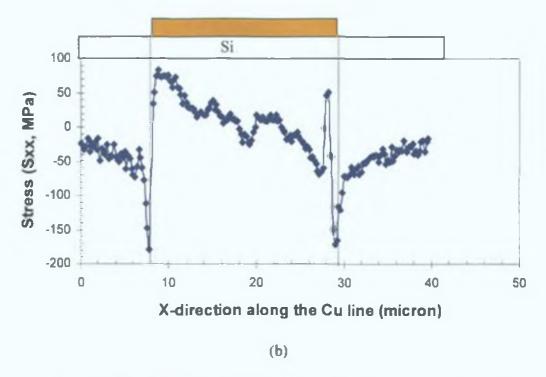

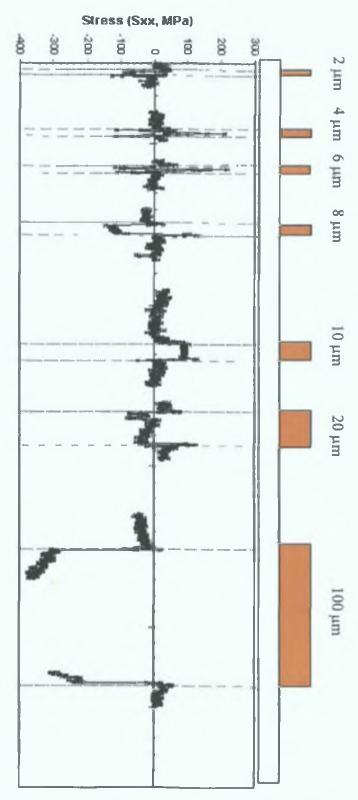

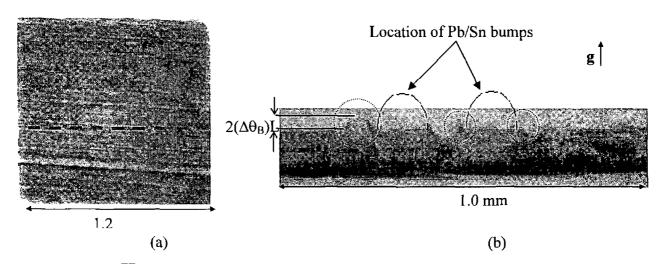

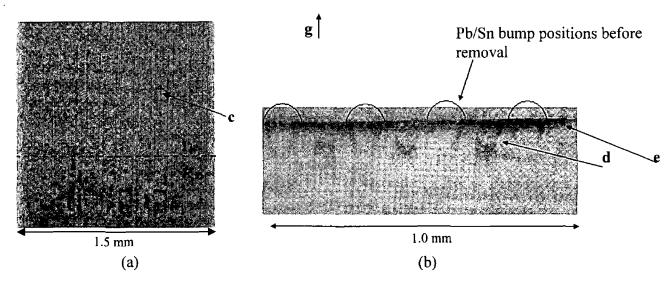

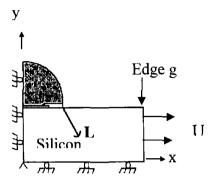

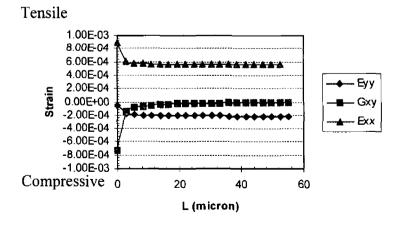

| ω                         | scattering frequency                                                |