# Electrical and Chemical Characterisation of Ultrathin Transistor Gate Dielectric Layers

A thesis for the Degree of Doctor of Philosophy

Presented to Dublin City University

by

Robert O'Connor, B.Sc. School of Physical Sciences Dublin City University

Research Supervisor:

Dr. Greg Hughes

January 2005

# Declaration

I hereby certify that this material, which I now submit for assessment on the programme of study leading to the award of Doctor of Philosophy is entirely my own work and has not been taken from the work of others save and to the extent of which the work has been cited and acknowledged

Signed: 1.D Number: 917482697

Date: 11/4/05

### Acknowledgements

Many thanks to everyone who helped me both directly and indirectly during the last 3 years; to Intel Ireland and Enterprise Ireland for funding. Thanks to IMEC for providing most of the samples used in this work, and to Robin Degraeve and many others at IMEC for passing on their expertise in the field, without which the project would have failed. Within DCU there are countless people to acknowledge, particular thanks to Pat Wogan for help with measurement setups and occasional automotive assistance! Away from DCU, thanks to friends and family for their support, both financial and otherwise, and lastly and most importantly, thanks to my project supervisor, Dr. Greg Hughes for listening and helping over the years and even travelling all the way to New York to make measurements!

| 3.2.3 Breakdown Mechanisms                                                   | 49    |

|------------------------------------------------------------------------------|-------|

| 3.3 Stress Induced Leakage Current                                           | 51    |

| 3.4 Detection of Interface Traps Using Charge Pumping                        | 53    |

| 3.5 Device Degradation                                                       | 55    |

| 3.6 Summary                                                                  | 58    |

| 3.7 References                                                               | 60    |

| Chapter 4: Electrical Characterisation of Ultra-thin SiON layers             | 64    |

| 4.1 Introduction                                                             | 64    |

| 4.2 Sample Fabrication                                                       | 64    |

| 4.3 Reliability                                                              | 66    |

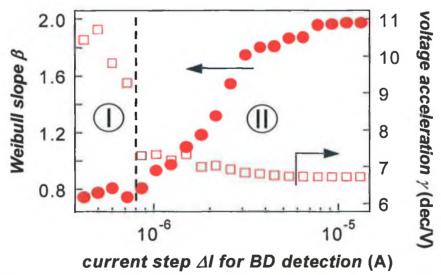

| 4.4 Further examination of Weibull slopes, trap generation and breakdow      | n 73  |

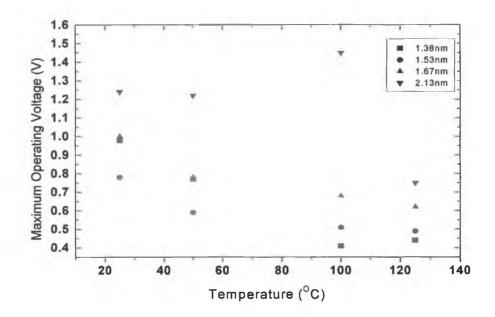

| 4.5 Elevated Temperature Effects                                             | 78    |

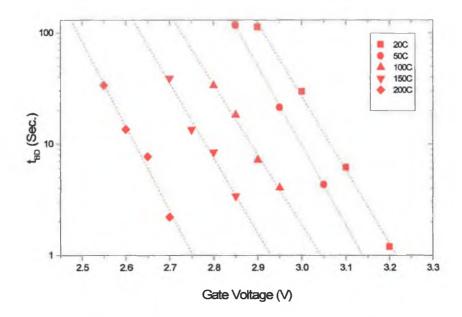

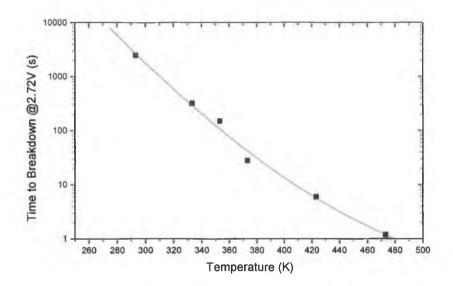

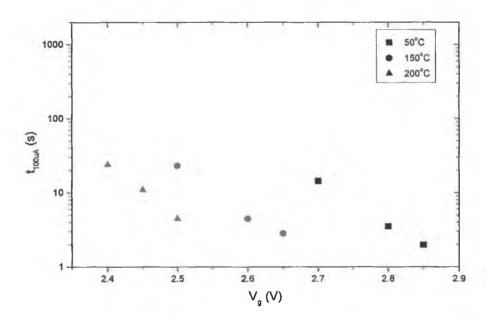

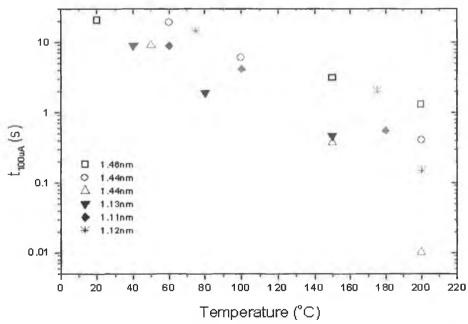

| 4.5.1 Temperature Accelerated Breakdown                                      | 78    |

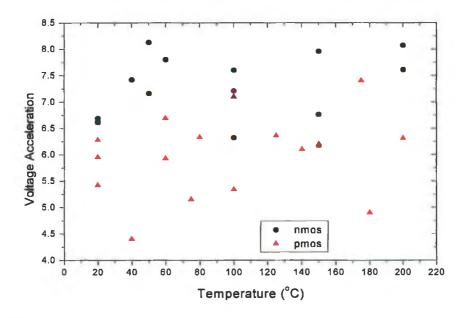

| 4.5.2 Interdependence of Temperature and Voltage During Stress               | 83    |

| 4.6 Progressive Breakdown and Device Functionality                           | 86    |

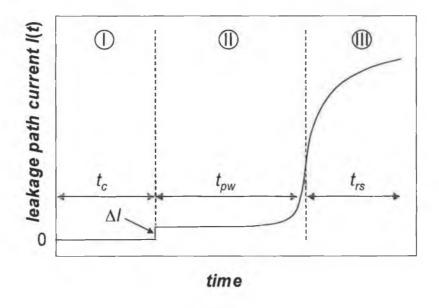

| 4.6.1 Progressive Wear-out                                                   | 86    |

| 4.6.2 Factors Affecting Progressive Breakdown                                | 88    |

| 4.6.3 FET Operation in the Progressive Phase                                 | 90    |

| 4.7 Impact of Breakdown on Circuit Operation                                 | 97    |

| 4.8 Summary                                                                  | 98    |

| 4.9 References                                                               | 100   |

| Chapter 5: Electrical Characterisation of Hafnium Silicate Dielectric Layers | s 103 |

| 5.1 Introduction                                                             | 103   |

| 5.2 Sample Preparation                                                       | 104   |

| 5.3 Reliability                                                              | 105   |

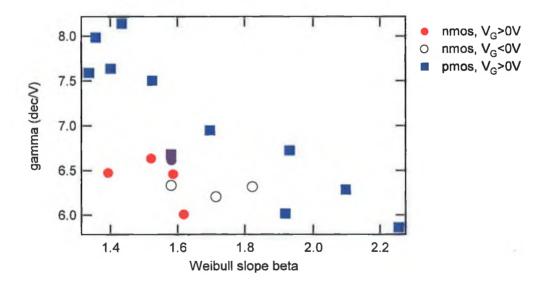

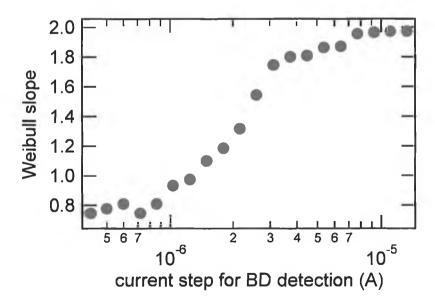

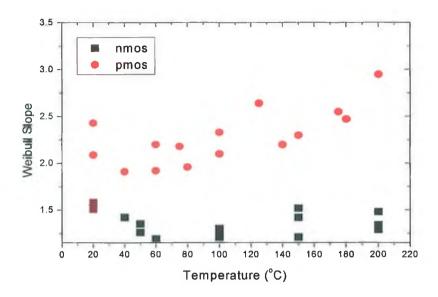

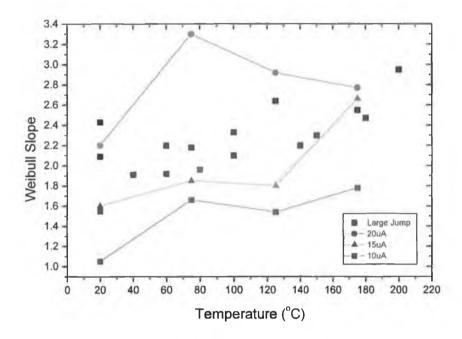

| 5.3.1 Weibull Slopes                                                         | 109   |

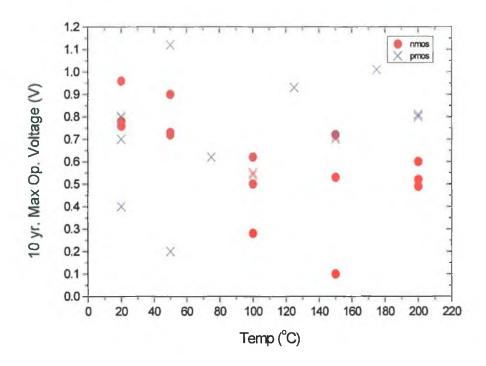

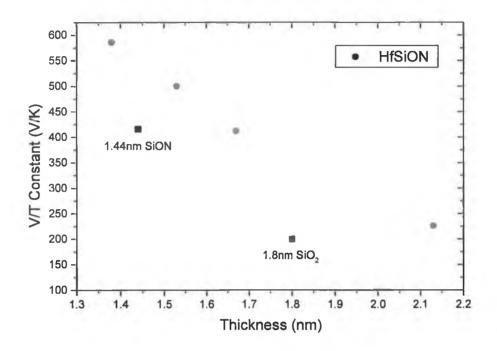

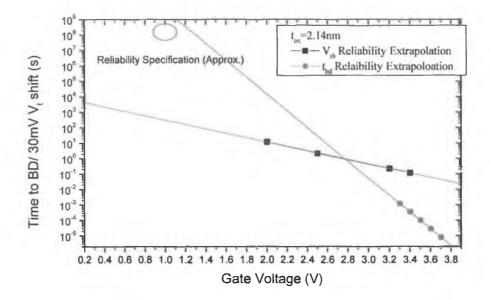

| 5.3.2 Voltage Acceleration                                                   | 111   |

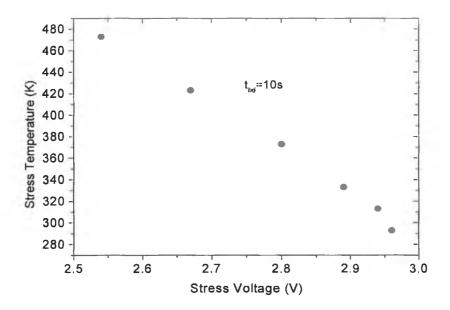

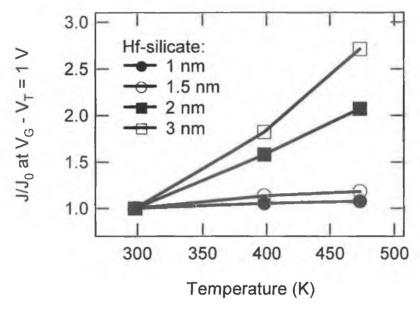

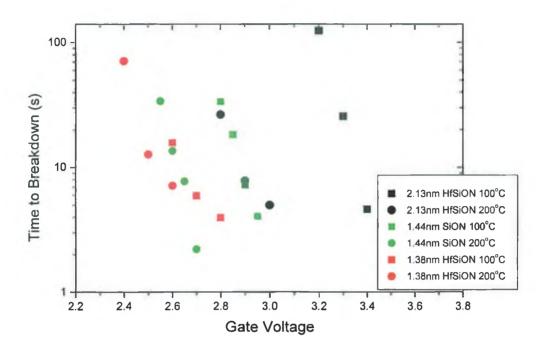

| 5.4 Temperature Acceleration of Breakdown.                                   | 113   |

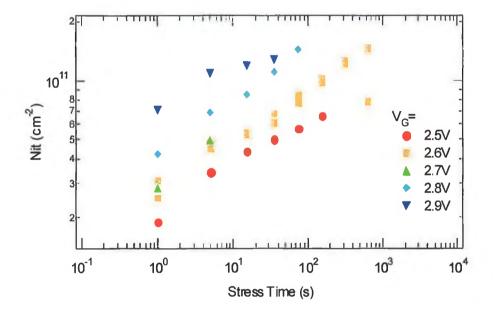

| 5.5 Degradation of FET Parameters During Stress                              | 115   |

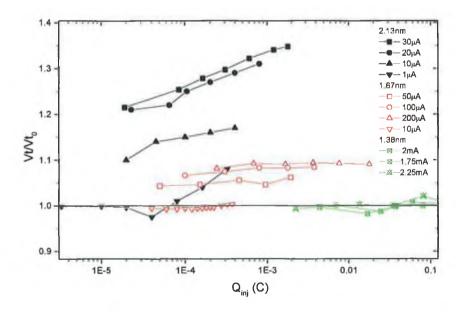

| 5.5.1 Threshold Voltage                                                      | 116   |

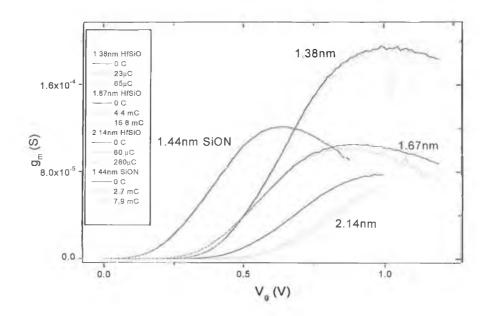

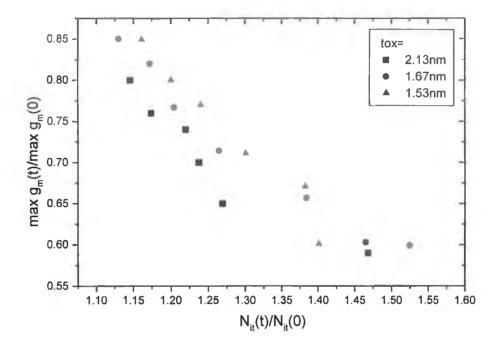

| 5.5.2 Transconductance                                   | 120          |  |

|----------------------------------------------------------|--------------|--|

| 5.5.3 Subthreshold Swing                                 | 124          |  |

| 5.4.4 Device Operation                                   | 125          |  |

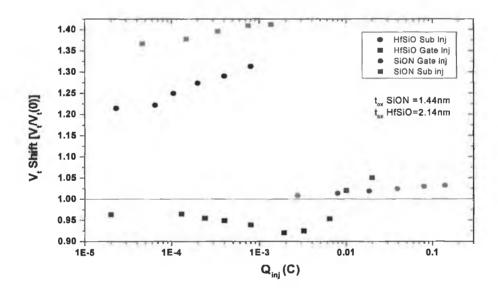

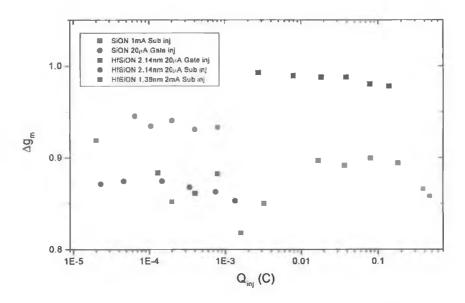

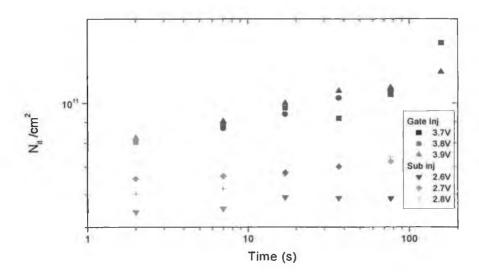

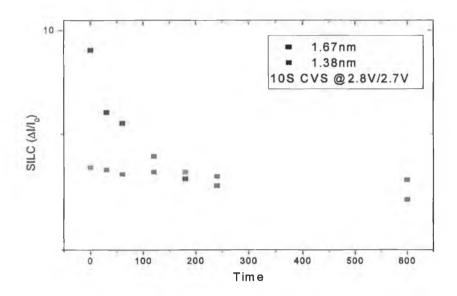

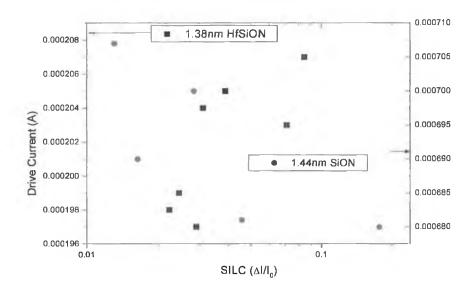

| 5.6 Stress Induced Leakage Current                       | 128          |  |

| 5.7 Summary                                              | 137          |  |

| 5.8 References                                           | 139          |  |

|                                                          | 1 HECON C-4- |  |

| Chapter 6: Chemical Characterisation of Blanket SiON and |              |  |

| Dielectrics Layers                                       | 142          |  |

| 6.1 Introduction                                         | 142          |  |

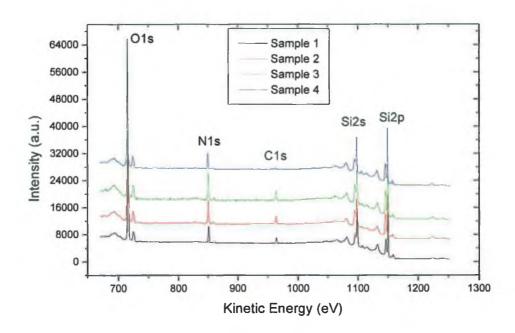

| 6.2 Characterisation of SiON layers                      | 144          |  |

| 6.2.1 XPS                                                | 144          |  |

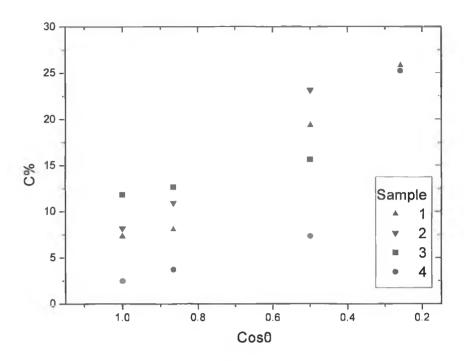

| 6.2.2 ARXPS Study                                        | 146          |  |

| 6.2.3 Soft XPS Using Synchrotron Radiation               | 151          |  |

| 6.2.4 SIMS                                               | 155          |  |

| 6.3 Characterisation of HfSiON Layers                    | 156          |  |

| 6.3.1 XPS and ARXPS Study                                | 156          |  |

| 6.3.2 SIMS Results                                       | 160          |  |

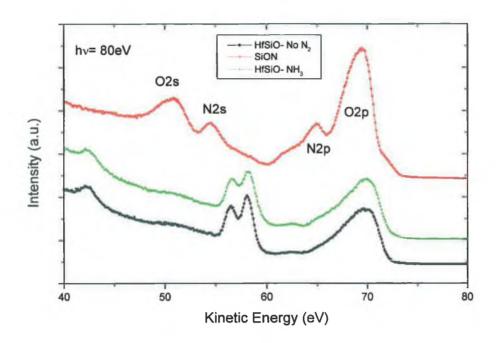

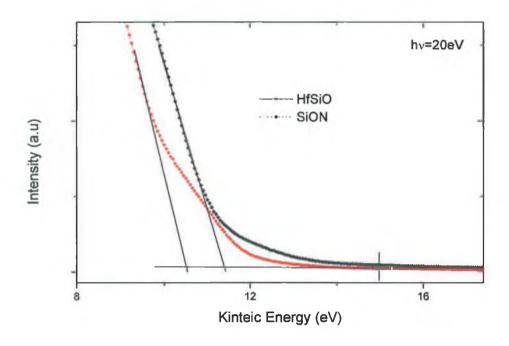

| 6.3.3 Soft XPS Using Synchrotron Radiation               | 162          |  |

| 6.3.4 X-Ray Absorption Spectroscopy                      | 165          |  |

| 6.4 Summary                                              | 167          |  |

| 6.5 References                                           | 169          |  |

|                                                          |              |  |

| Chapter 7: Conclusions and Future Directions             | 171          |  |

| 7.1 Conclusions of This Work                             | 171          |  |

| 7.1.1 Electrical Measurements                            |              |  |

| 7.1.2 Surface Analysis Results                           | 173          |  |

| 7.2 The Future for high-k dielectrics                    | 175          |  |

### Abstract

This work examines the suitability of both ultrathin Silicon Oxynitride (SiON) and Hafnium Silicate (HfSiON) layers to be used as high-permittivity gate dielectrics to serve as a replacement to silicon dioxide (SiO<sub>2</sub>) in future Metal-Oxide-Semiconductor (MOS) technologies. The reason SiO<sub>2</sub> needs to be replaced is the extremely high levels of leakage current displayed in ultrathin layers required for sub-90nm CMOS. The main part of the thesis consists of an electrical characterisation section, where the layers are evaluated in terms of their electrical reliability when fabricated into MOS devices, so as to determine their maximum operating voltage and performance during expected device lifetime. Techniques used include constant voltage stress, constant current stress, ramped voltage stress, charge pumping to determine interface state densities and stress induced leakage current measurements. Conventional methods of determining reliability are also evaluated. Results show that these methods cannot be blindly applied in ultrathin regime, and that finding an alternative dielectric material is a major challenge.

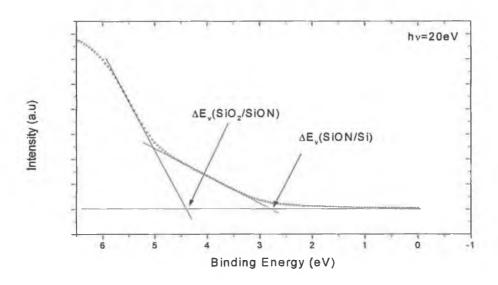

The second part of the thesis consists of a chemical characterisation section, where blanket layers of the materials are examined using a range of surface analysis techniques. X-ray photoelectron spectroscopy (XPS), synchrotron based photoemission and secondary ion mass spectroscopy (SIMS) are used to determine the chemical composition and chemical depth profile information of the layers and to probe the electronic structure of the valence bands and allow the valence band offsets to be determined.

# **Publications Resulting From This Work:**

Robert O'Connor, Robin Degraeve, Ben Kaczer, Anabela Veloso, Greg Hughes, Guido Groeseneken.

Weibull slope and voltage acceleration of ultrathin oxynitrides.

Microelectronic Engineering. 72 (2004) pp 61-65.

Robert O'Connor, Greg Hughes, Robin Degraeve, Ben Kaczer. Temperature accelerated breakdown in ultra-thin SiON dielectrics Semicond. Sci. Tech. 19 (2004) pp. 1254-1258.

Robert O'Connor, Greg Hughes, Robin Degraeve, Ben Kaczer.

Progressive breakdown in ultra-thin SiON dielectrics and its effect on transistor performance.

Microelectronics Reliability 45 (2005) pp 869-874.

Robert O'Connor, Greg Hughes, Robin Degraeve, Ben Kaczer, Thomas Kaureauf. *Reliability of HfSiON gate dielectrics*. Semicond. Sci. Tech. 20 (2005) pp. 68-71.

Robert O'Connor, Greg Hughes, Robin Degraeve, Ben Kaczer, Thomas Kaureauf. *Charge trapping in MOSFETS with HfSiON gate dielectrics*. In Press, Accepted to Microelectronic Engineering (2004).

Robert O'Connor, Stephen McDonnell, Greg Hughes.

Low voltage stress-induced leakage current in 1.4-2.1nm SiON and HfSiON gate dielectric layers.

Submitted to Semiconductor Science and Technology.

Robert O'Connor, Greg Hughes.

A synchrotron radiation study of high-k gate dielectrics In preparation.

A. Veloso, F. N. Cubaynes, A. Rothschill, S. Mertenl, R. Degraeve, R. O'Connor, C. Olsen, L. Date, M. Schaekers, C. Dachs, M. Jurczak.

Ultrathin oxynitride gate dielectrics by pulsed-rf DPN for 65nm general-purpose CMOS applications.

Proc. of the 33<sup>rd</sup> European Solid-State Device Research Conference ESSDERC'2003, pp. 239-242 (September 2003).

B. Kaczer, R. Degraeve, R. O'Connor, Ph. Roussel, G. Groeseneken. *Implications of progressive wear-out for lifetime extrapolation of ultra-thin (EOT~1nm) SiON films.*

Presented at IEDM 2004.

# Chapter 1: Introduction

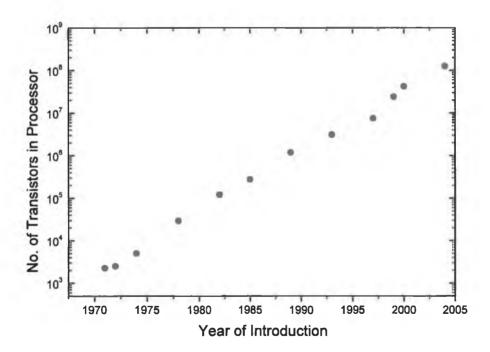

It is a well-known fact that the digital revolution of the last 40 years has been based on the development of increasingly faster and smaller microprocessors, memory units and other microelectronic devices that make data transfer faster. It is also common knowledge that these advanced devices have been made possible due to intensive research into the fundamental building block of these devices, namely the Metal Oxide Semiconductor Field Effect Transistor (MOSFET). The advancement of MOSFET technology has steadily followed Moore's Law <sup>1</sup> (as shown in figure 1.1) for over 30 years, and the number of transistors per microprocessor has now exceeded 10<sup>8</sup>.

Figure 1.1 The number of MOS transistors on Intel processor versus year of introduction. Moore's Law states that the number should double every 18-24 months. Data from INTEL.

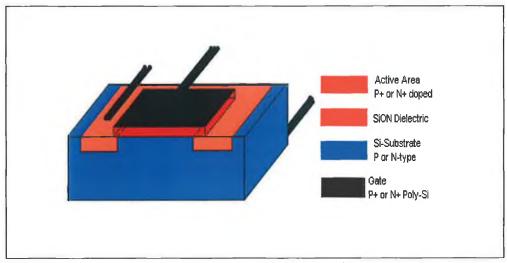

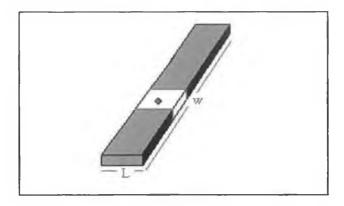

### 1.1 The MOS Transistor

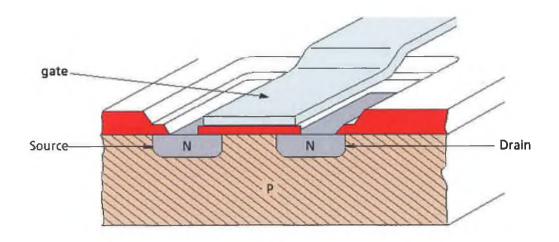

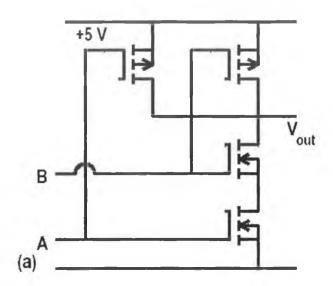

In the microprocessor, the MOSFET essentially works as a switch for controlling digital logic, allowing Boolean calculations. The MOSFET is fabricated as shown in figure 1.2 by implanting a p-type (or n-type) silicon substrate with n-type (p-type) wells which act as source and drain. A layer of insulating material is used to cover the channel between the source and the drain. This insulator allows a conductive channel to be formed at the substrate-insulator interface when a sufficient gate bias is applied, thereby enabling conduction from source to drain.

Figure 1.2 Schematic cross section of an n-MOSFET.

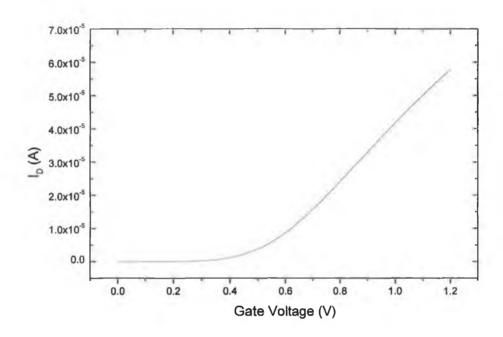

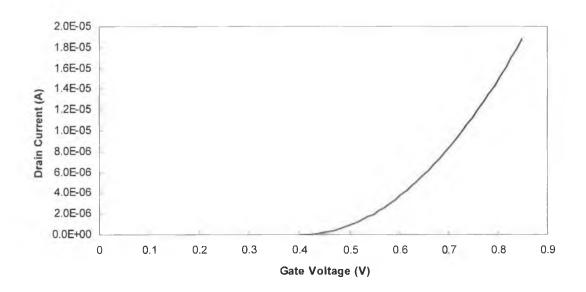

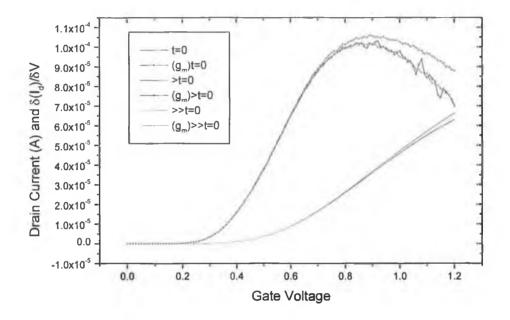

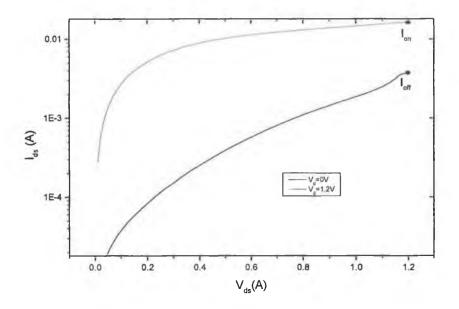

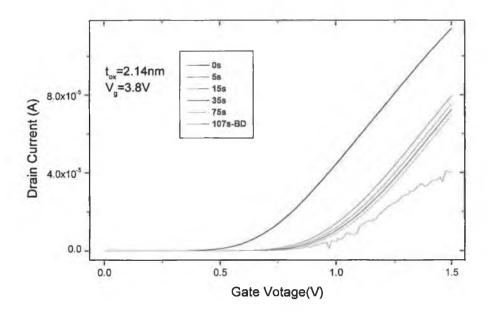

The gate voltage controls the switching action by controlling the carrier density in the channel. Above the 'threshold voltage', current flows and the switch is on, below this voltage almost zero current flows and the switch is off. A drain current-gate voltage ( $I_dV_g$ ) curve for such a device is shown in figure 1.3, where a fixed voltage of 0.05V is applied to the drain and the gate voltage is increased.

Figure 1.3 Sample  $I_dV_g$  curve for a MOSFET

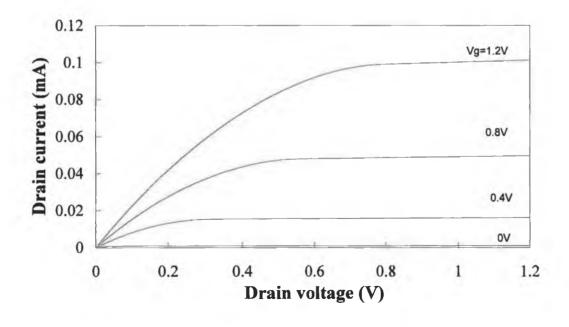

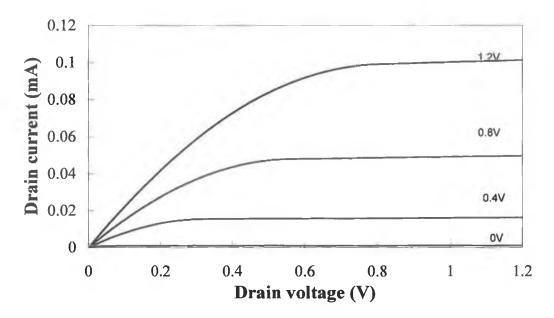

The threshold behaviour can be clearly seen above a gate voltage of 0.5V. Another plot commonly used to analyse a MOSFET is shown in figure 1.4. The plot shows the drain current ( $I_d$ ) versus the drain voltage ( $V_g$ ) characteristics for a range of gate voltages and illustrates the how the I-V curve for the channel is modified by the changing gate voltage.

Figure 1.4 Sample I<sub>d</sub>V<sub>d</sub> curves for a MOSFET, showing the effect of increasing gate voltage.

# 1.2 Scaling Limits and the End of SiO<sub>2</sub>

The gate dielectric plays a critical role in MOSFET technology. From the beginning of integrated circuit fabrication from silicon, the material used as the gate dielectric has been  $SiO_2$ . It is the native oxide of Si and has excellent material properties including large bandgap (~8.8eV), high resistivity (>10<sup>12</sup>  $\Omega$ .m), and it forms a high quality interface with the Si substrate with very low interface state densities ( $<5x10^{10}$ cm<sup>-2</sup>)<sup>2</sup>. All of these properties make it the ideal choice as dielectric layer, and indeed it is because of these properties that the Si/SiO<sub>2</sub> system has been so successful in comparison to other possible semiconductor candidates, such as germanium.

Over the years, SiO<sub>2</sub> has continued to be the dielectric of choice during aggressive scaling that has led to a reduction in channel length (the distance from source to drain in the silicon substrate) from 6µm for the 8080 Processor in 1974 to 0.18µm for the Pentium 4 in 2000. Already channel lengths as low as 65nm are being currently tested for integration into microprocessors<sup>3</sup>. One of the problems associated with this approach is that we cannot assume that device properties will be maintained for as long as the down-scaling continues. Over the years, scaling laws have often appeared to be a limiting factor. Decreasing all device dimensions increases current density and power loss, but a reduction in supply voltage to counteract this limits the speed, so there are many trade offs to be considered.

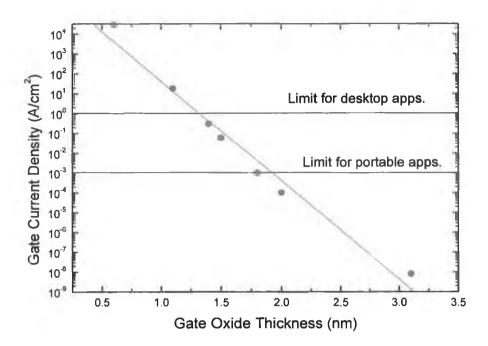

As dimensions are further reduced, a problem with the SiO<sub>2</sub> layer becomes evident. Electrons can tunnel quantum mechanically through barrier layers, which have a thickness in the nanometer range. The tunnel current is exponentially dependent on oxide thickness and in ultra-thin layers it can result in the degradation of the insulating properties of the dielectric, within the expected lifetime, which can lead to device failure. The tunnel current vs. oxide thickness plot <sup>4</sup> in figure 1.5 illustrates the extraordinary current densities present in ultrathin layers. The horizontal lines, indicating the maximum allowable leakage currents for portable and desktop applications, show that an alternative dielectric with lower leakage current is required below 1.2nm thickness.

Figure 1.5 Oxide leakage current @1.5V for 35nm channel length nMOS devices. From ref. 2.

Indeed below 1.2nm the idea of a layer of SiO<sub>2</sub> begins to lose meaning as a large fraction of the layer is made of the structural transition region from Si to SiO<sub>2</sub> leaving perhaps 2-3 monolayers of 'bulk' SiO<sub>2</sub>. At these ultrathin dimensions, thickness uniformity also becomes an issue due to the fact that a non-uniform layer leads to conduction hot-spots<sup>5</sup>.

The basic necessity for an alternative material is that it can give the same capacitance as an ultrathin layer of SiO<sub>2</sub>, but can be fabricated thicker to stem the leakage current problem. The basic equation dictating the capacitance of a dielectric layer is given by:

$$C_{ox} = \frac{\varepsilon_r \varepsilon_0 A}{d}$$

Eq. 1.1

where  $\varepsilon_r$  (sometimes denoted by 'k') is the relative permittivity of the material,  $\varepsilon_0$  is the permittivity of free space, A is the area of the layer, and d is the thickness. It is clear that using a material with a higher relative permittivity (dielectric constant) than SiO<sub>2</sub> (k=3.82) would allow the thickness of the layer to be increased while maintaining the same capacitance. This increase in thickness

has the effect of reducing the leakage current due to a reduction in the quantum mechanical tunneling current.

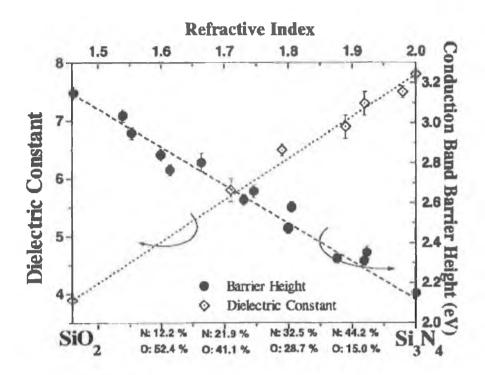

The addition of nitrogen to SiO<sub>2</sub> to make a SiO<sub>x</sub>N<sub>y</sub> dielectric layer was found to increase the dielectric constant slightly<sup>6</sup>. As the nitrogen concentration is increased in the layer, the dielectric constant rises linearly, as seen in figure 1.6. As well as raising the dielectric constant, SiON gate dielectrics have been shown to suppress the migration of boron from p+ poly-Si gates into the channel, which is a problem with SiO<sub>2</sub> that causes threshold voltage shifts <sup>7</sup>. The nitrogen incorporation also leads to a better quality Si/SiO<sub>2</sub> interface. One reason which has been proposed to explain this improvement is that the introduction of a trivalent atom accommodates more flexible local bonding arrangements than is possible with the tetravalent silicon and divalent oxygen at the interface. Note also from the figure that nitrogen incorporation has the negative effect of lowering the barrier height to tunnelling carriers. The obvious question that arises from studying figure 1.6 is 'Why not use pure Si<sub>3</sub>N<sub>4</sub> as the dielectric, as you could have a layer twice as thick with the same capacitance?'

The reason is that at higher nitrogen concentrations, transconductance (the conductivity of the channel in a transistor) is lowered, the threshold voltage is shifted and, at high concentrations near the interface, the device mobility is adversely affected <sup>6</sup>. While SiO<sub>x</sub>N<sub>y</sub> layers are clearly convenient gate dielectrics, involving only a modest change in processing steps, it is accepted that their use in advanced processors will be limited and that a move completely away from silicon oxide based dielectrics will eventually be needed as aggressive dimensional scaling continues.

# 1.3 Charge transport mechanisms in gate dielectrics

When a ramp voltage is applied across an oxide, it becomes clear that the oxide is not a perfect insulator, as a current is detected. Figure 1.7 below shows the I-V characteristics for 3 different oxides prepared under different conditions, with a thickness of  $\sim 1.5$ nm. The sudden increase in current at a voltage of about 3.5V results from a breakdown of the insulating properties of the layers. From the point where this breakdown occurs we can then calculate the breakdown field  $(E=V/t_{ox})$  to be  $2.33\times10^9$  V/m.

Figure 1.7 Tunnel current in 1 µm x 1 µm capacitor with active area encompassing source and drain, n+ poly-si gate and active area, p-type substrate. Thicknesses quoted are optically measured.

The predominant conduction process in dielectric layers of this thickness is quantum mechanical electron tunnelling through the oxide<sup>9</sup>. During I-V measurements on thin oxides where the gate voltage is lower than 3.7V, the electrons no longer travel through a triangular energy barrier into the oxide conduction band as happens for thicker oxides. The electrons tunnel directly from anode to cathode into the conduction band of the substrate. This process is

shown in figure 1.8. The easiest way to differentiate between the two is that direct tunnelling shows no temperature dependence, as the same barrier is encountered by tunnelling carriers independent of thermal energy, whereas with FN tunnelling the barrier becomes smaller as thermal energy is increased. The two processes are described by different equations, but the important factor is that the tunnel current is exponentially dependent on oxide thickness. In thicker oxides, Fowler-Nordheim<sup>10</sup> tunnelling dominates, where the electrons travel through the SiO<sub>2</sub> conduction band into that of the silicon substrate.

Figure 1.8 Tunnelling mechanisms though SiO<sub>2</sub>. 'CB' represents the start of the silicon conduction band

Fowler-Nordheim Tunnelling is described by the equation<sup>13</sup>:

$$J_{FN} = A.E_{ox}^2 \exp\left[-\frac{B}{E_{ox}}\right]$$

Eq 1.2

where

$$A = \frac{q^3}{16\pi^2\hbar\Phi_B}$$

and  $B = \frac{4}{3}\frac{(2m^*)^{1/2}}{q\hbar}\Phi_B^{3/2}$ .

q is the electron charge,  $\Phi_B$  is the barrier height, and  $m^*$  is the effective electron mass.

Direct tunnelling is more difficult to describe and involves using the WKB approximation. One model describes the current as <sup>12</sup>:

$$J_{DT} = AB \exp\left(\frac{\left(-4\pi(2q.m^*)^{1/2}\right)T_{ax}B^{1/2}}{h}\right) - A\Phi_R \exp\left(\frac{\left(-4\pi(2q.m^*)^{1/2}T_{ax}\Phi_B^{1/2}\right)}{h}\right)$$

(Eq 1.3)

where

$$A = \Phi_B - \frac{V_{ox}}{2}$$

and  $B = \left(\frac{q^2}{2\pi h T_{ox}^2}\right)$ ,  $V_{ox}$  is the oxide voltage, and  $T_{ox}$  is

the oxide thickness. Clearly direct tunnelling is a lot more difficult to describe mathematically. Tunnel current mechanisms are discussed in more detail in Chapter 3.

### 1.4 The Si/insulator Interface

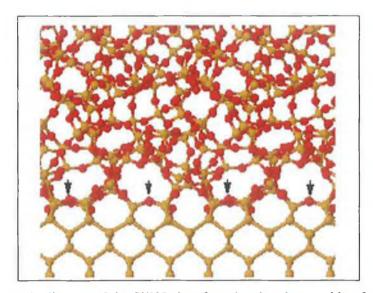

The ideal device will have a periodic crystal of Si terminated at the interface where a layer of amorphous SiO<sub>2</sub> begins. This however is only an ideal case, and in Si/SiO<sub>2</sub> systems is not possible. Termination is never perfect due to bond orientation and strain between the two layers as shown in Figure 1.9. Hydrogen is used to passivate dangling Si bonds at the interface as the uppermost layer of Si cannot be co-ordinated to four oxygen atoms as required for stoichiometric SiO<sub>2</sub><sup>11</sup>. Imperfections at the Si/SiO<sub>2</sub> surface can also degrade the quality of the interface.

Figure 1.9 Schematic diagram of the  $Si/SiO_2$  interface showing the transition from amorphous  $SiO_2$  to crystalline Si. This transition cannot be made without introducing structural imperfections. Yellow-silicon, Red-oxygen

A more realistic description of the interface is crystalline Si merging into some interfacial oxide SiO<sub>x</sub> where x is less than 2 and then into bulk SiO<sub>2</sub>. The resulting interface trapped charge (from mid-bandgap interface states) contributes to threshold voltage shifts and accelerates oxide breakdown, and can also degrade transconductance (and thus channel mobility) due to scattering<sup>12</sup>. As mentioned earlier, as the gate dielectric is scaled down toward 1nm, the interface becomes a more significant fraction of the total layer, and the understanding of interface properties becomes all the more critical. These interfacial problems become more pronounced as SiO<sub>2</sub> is replaced by new materials, which may behave quite differently on a Si substrate.

# 1.5 Summary and Outline

It is clear that dielectric scaling poses a significant problem for the semiconductor industry. Chapter 2 outlines the techniques used for the study of the chemical composition of blanket dielectric layers, including X-ray Photoelectron Spectroscopy (XPS), synchrotron radiation based photoemission studies, and Secondary Ion Mass Spectroscopy (SIMS). XPS provides information on the chemical composition while the synchrotron based

photoemission studies probe the electronic structure of the valence bands and allow the valence band offsets to be determined. SIMS provides some useful depth profile information. This work in Chapters 3,4, and 5 focuses on time dependent dielectric breakdown (TDDB), and the external parameters that influence reliability estimates based on TDDB measurements. Chapter 3 outlines the techniques used to characterise devices, how reliability estimates are arrived at, the causes of breakdown and the effect of oxide breakdown on a device. Chapter 4 deals with work carried out on ultra-thin SiON dielectric layers for use in the 65nm process node, their reliability, the temperature dependence of timeto-breakdown, the progressive nature of the breakdown and the effects of oxide degradation on MOSFET parameters and the implications for a real circuit. Chapter 5 deals with a similar procedure for HfSiON layers, and outlines the differences in characterisation methods and reliability between the two materials. The final part of the thesis (Chapter 6) deals with the chemical characterisation of blanket layers of the SiON and HfSiON dielectrics. These layers are the same thickness as those used in the device structures. Chapter 7 then concludes the work, summarising the findings from the electrical and chemical characterisation of the dielectric layers, and includes a brief discussion on the options available for CMOS dielectric layers for future generations.

#### 1.6 References

- <sup>3</sup> A. Veloso, F. N. Cubaynes, A. Rothschild, S. Mertens, R. Degraeve, R. O'Connor, C. Olsen, L. Date, M. Schaekers, C. Dachs, M. Jurczak, Ultra-thin Oxynitride Gate Dielectrics by Pulsed-RF DPN for 65 nm General Purpose CMOS Applications, *Proc. of the 33<sup>rd</sup> ESSDERC'2003*, pp. 239-242.

- <sup>4</sup> M. L. Green, T. W. Sorsch, G. L. Timp, D. A. Muller, B. E. Weir, P. J. Silverman, S. V. Moccio and Y. O. Kim, Understanding the limits of ultrathin SiO<sub>2</sub> and Si-O-N gate dielectrics for sub-50 nm CMOS, Microeletron. Eng. 48 (1-4) (1999) pp. 25-30.

- <sup>5</sup> J.H. Stathis, Reliability limits for the gate insulator in CMOS technology, IBM J. Research and Dev 46 (2/3) (2002) pp. 265-286.

- <sup>6</sup> X. Guo, T.P. Ma, Tunneling leakage current in oxynitride: dependence on oxygen/nitrogen content, IEEE Elec. Dev. Letters, 19 (6) (1998) pp. 207-209.

- <sup>7</sup> C.T. Wu, A. Mieckowski, R. S. Ridley Sr., G. Dolny, T. Grebs, J. Linn and J. Ruzyllo, Effect of nitridation on the reliability of thick gate oxides, Microelectron. Reliab. 43 (1) (2003) pp. 43-47.

- <sup>8</sup> G.D. Wilk, R.M. Wallace, J.M. Anthony, High-k gate dielectrics: Current status and materials properties consideration, J. Appl. Phys. 89 (10) (2001), pp. 5243-5275.

<sup>&</sup>lt;sup>1</sup> G.E. Moore, Cramming more components onto integrated circuits, Electronics 38 (8) 1965.

<sup>&</sup>lt;sup>2</sup> M.L. Green, E.P. Gusev, R. Degraeve, E.L. Garfunkel, Ultrathin (<4nm) SiO<sub>2</sub> and Si-O-N gate dielectric layers for silicon microelectronics: Understanding the processing, structure, and physical and electrical limits, J. Appl. Phys. 90 (5) (2001) pp. 2057-2121.

<sup>9</sup> M. Hirose, Electron tunnelling through ultrathin SiO<sub>2</sub>, Materials Sci, and Eng, B41 (1996) pp. 35-38.

<sup>10</sup>R. H. Fowler, L. Nordheim, Electron emission in intense electric fields, Proc. R. Soc. London, Ser. A 119, 173 (1928).

<sup>11</sup> E.H. Poindexter, MOS interface states: overview and physicochemical perspective, Semicond. Sci. Tech. 4 (1989) pp.961-969.

<sup>12</sup> Y.B. Park, D.K. Schroder, Degradation of thin tunnel gate oxide under constant Fowler-Nordheim current stress for a flash EEPROM, IEEE Trans. Electron. Devices, 45 (6) pp. 1361-1368 (1998).

# Chapter 2: Chemical Characterisation Techniques for Dielectric Layer Analysis

### 2.1 Introduction

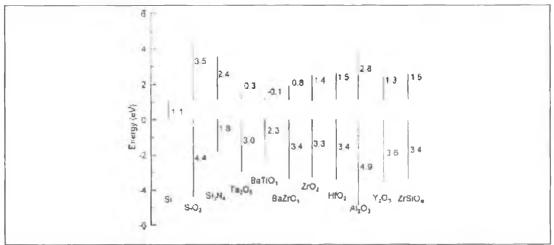

It is the electrical characteristics of a device that are the ultimate factor in evaluating the effectiveness of a particular dielectric layer. However, the chemical composition, elemental depth profile, and interface quality of the layer impact on the electrical properties that it exhibits. Accordingly, chemical characterisation techniques are used to obtain information about the valence and conduction band offsets, which have a direct influence on the electrical characteristics of the structures.

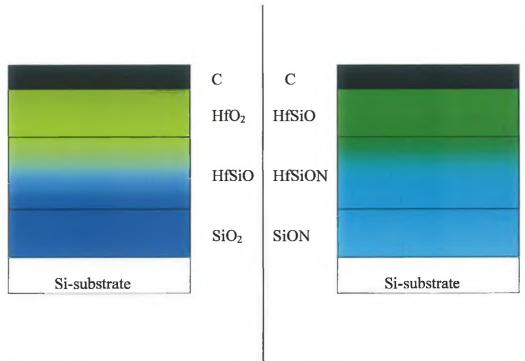

The SiO<sub>2</sub>/Si interface has been studied thoroughly in the past 30 years, and is relatively well understood. However, as technology has evolved and the requirement for a new dielectric material has become evident, many new material systems are being studied. The incorporation of nitrogen into the SiO<sub>2</sub>, which raises the dielectric constant slightly was undertaken and, more recently, the use of metal oxides such as HfO<sub>2</sub> and TiO<sub>2</sub> which have significantly higher dielectric constants is being actively investigated. More complex systems have also come to be studied, like gate stacks with two or three interfaces within the layered structure<sup>1</sup>.

This chapter outlines the techniques use to characterise both SiON and HfSiON blanket dielectric layers deposited on silicon substrates. The SiON layers were grown in the same process as the device wafers that are electrically characterised in Chapter 4 of this thesis, and therefore directly represent the same oxide layers. This allows for the possibility of attributing particular electrical characteristics to different processing conditions. The hafnium silicate blanket layers were grown for test purposes and were not integrated into device structures. Nevertheless, some interesting chemical analysis can be carried out by comparing results from different processing conditions.

Techniques used for the chemical analysis were X-ray photoelectron spectroscopy (XPS) (and angle resolved XPS), Soft XPS using a synchrotron radiation source, X-ray absorption spectroscopy (XAS) and Secondary Ion Mass Spectroscopy (SIMS). The underlying principles and strengths of each technique are briefly outlined in this chapter.

# 2.2 X-ray Photoelectron Spectroscopy

### 2.2.1 Photoemission

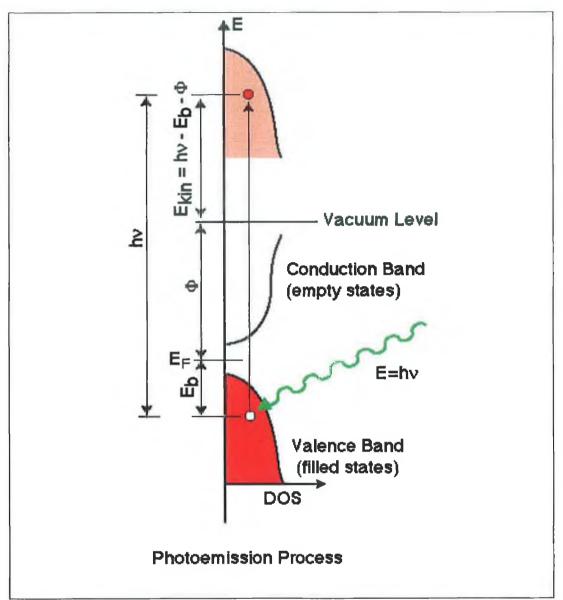

The basic photoemission process is shown in figure  $2.1^2$ . When light of suitable photon energy is incident on a solid, electrons in the material can absorb the photons as described by the photoelectric effect. In this work, the x-ray photon source was a conventional Mg K $\alpha$  line producing 1253.6eV photons. Because of the energy of the incident photon, the electrons that have binding energy less than 1250eV can be excited from below the Fermi level to above the vacuum level of the solid<sup>3</sup>.

Figure 2.1 The basic photoemission process, showing how the resultant kinetic energy of the photoelectron is deduced.

The kinetic energy of such an electron is described in equation 1.

$$E_{Kin} = h \nu - E_B - \phi \qquad \text{Eq. 2.1}$$

That is, the kinetic energy  $(E_k)$  of an emitted electron is dependent on the incident photon energy  $(h\nu)$ , the binding energy of the electron in the parent atom  $(E_B)$  and the work function  $(\phi)$  of the solid. Because the binding energy of each core level electron is characteristic of the atom from which it came, analysis of the range of kinetic energies of the emitted electrons allows elemental

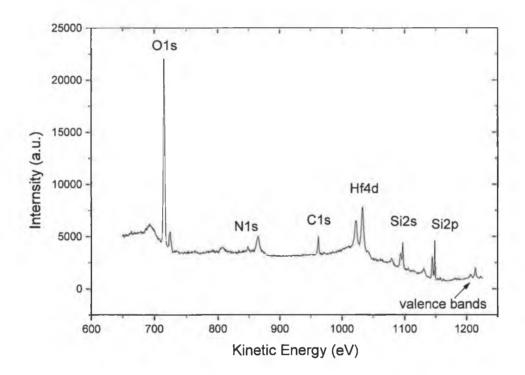

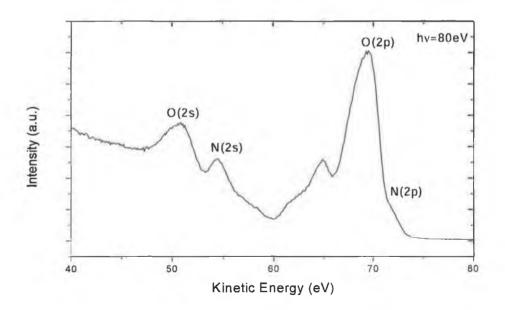

analysis. Valence band states can also be probed. They are however broader and more complicated as valence band electrons are involved in bonding with other atoms. A typical survey XPS spectrum of an ultrathin HfSiON layer is shown in figure 2.2.

Figure 2.2 A typical wide scan for a HfSiON sample showing peaks associated with all of the expected elements.

The peaks associated with elements silicon, hafnium, oxygen, nitrogen, and carbon (which contaminates the sample surface) can be identified, as can the valence band levels at higher kinetic energy. The entire spectrum sits on a background of secondary electrons, which have been scattered during the photoemission process.

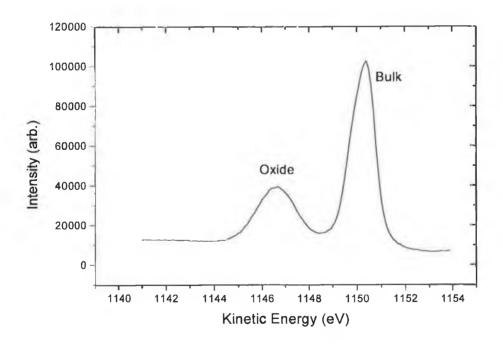

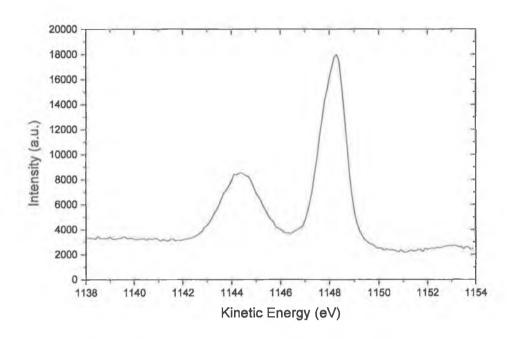

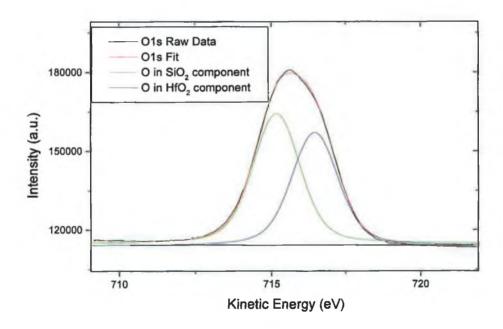

This wide energy scan is primarily used to determine the individual elements present in the sample. Further higher-resolution scans are carried out in the region of each elemental peak. In this case, Si2p, Hf4d, C1s, N1s, and O1s would be investigated. Shown in figure 2.3 is a Si2p spectrum from this HfSiON sample. There are 2 peaks, one at 1150.25eV and one at 1146.6eV. These kinetic energies can be converted to binding energies of 102.75eV and 106.4eV

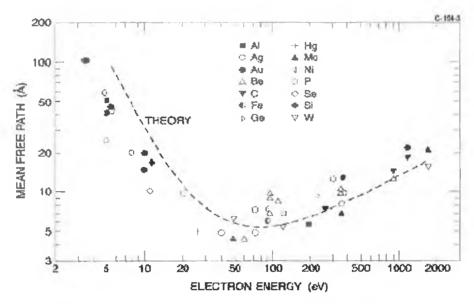

respectively. The lower binding energy peak is attributed to silicon atoms in the underlying substrate, while the higher binding peak is related to silicon atoms in an SiO<sub>2</sub> environment in the dielectric overlayer. The difference in binding energy reflects the difference in the chemical environment of these silicon atoms and is conventionally referred as to the chemical shift. The fact that the silicon substrate signal can be observed illustrates that the sampling depth of the technique is sufficient to 'see' through to the silicon substrate. The sampling depth is limited by the mean free path of an electron in the material in question. That is, the average distance an electron will travel in the material without undergoing a collision. Obviously, electrons will be detected from deeper down in a material with a high mean free path.

The dependence of electron mean free path on electron kinetic energy is illustrated in Figure 2.4<sup>4</sup>

Figure 2.3 A typical Si2p spectrum. The signal from the bulk is larger than the oxide signal, indicating that the sampling depth is much greater than the oxide thickness

The photoelectrons detected in our experiments, where measured  $E_K < 1000 eV$ , will thus originate from less than 10nm into the surface, due to exponential drop-off in signal with depth. Because the dielectric layers under consideration are no

more than ~5nm physical thickness, both the overlayer and the substrate can be simultaneously probed.

Because the samples under consideration are insulators, they are slow to replace electrons that leave during the photoemission process, leaving the layer positively charged. This charging causes the spectrum to move to higher binding energy. Because of this effect, all spectral peaks are referenced to the known binding energy of the surface C1s peak (285eV).

Figure 2.4 The universal electron mean free path curve.

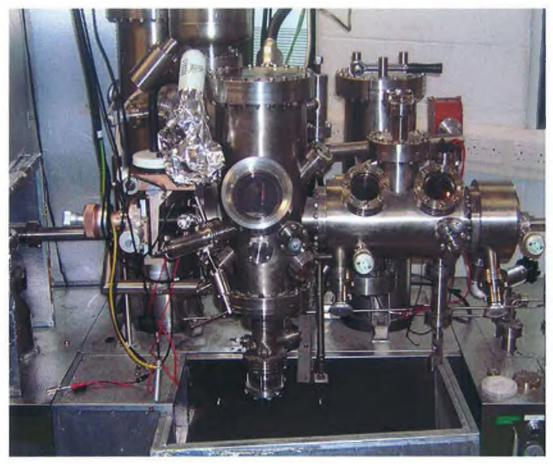

# 2.2.2 Experimental Setup

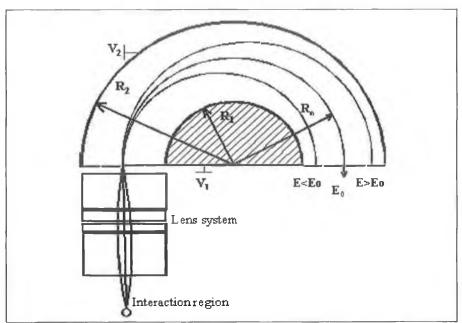

XPS is performed under vacuum, so as photoelectrons can enter the electron analyser without being scattered and the sample surface remains of constant chemical composition for the duration of the experiment. The vacuum system used consists of two rotary backed oil diffusion pumps. The system is shown in figure 2.5a. Samples are transferred from air through the fast entry lock on the right through a gate valve into an ultrahigh vacuum (UHV) preparation chamber. The sample is then transferred through another gate valve into the analysis chamber containing the x-ray source and the analyser. The hemispherical electron energy analyser is schematically shown in figure 2.5b. The excited electrons are focused through an electrostatic lens, and then pass through the

hemispherical analyser. Only electrons of energy  $E_0$  will pass through the hemispheres undeflected.  $E_0$  is swept through the entire energy range under consideration to acquire a spectrum.

Figure 2.5a XPS system. Samples are inserted through the fast entry lock on the right, through the preparation, and into the main analysis chamber where measurements are performed under ultrahigh vacuum

Figure 2.5b. A hemi-spherical analyser. Electrons of energy  $E < E_0$  and  $E > E_0$  are deflected by the potential applied to the analyser walls.

The photoelectron current is amplified by an electron multiplier know as a channeltron. The multiplier amplifies the signal by accelerating the electrons through a potential difference of 3.5KeV, causing the electrons to collide with the multiplier surface, releasing many more electrons in an electron cascade. The signal is then fed to a computer, which displays the number of counts as a function of electron kinetic energy.

# 2.2.3 Experimental Data Analysis

Before making quantitative comparisons of elemental composition, the 'photo-ionisation cross-section<sup>5</sup> for the elements in question must be taken into account. This is basically a measure of the probability of a particular atomic level being photo-ionised by an incident photon. Each photoemission peak is scaled to account for this before quantitative analysis can be carried out. The scaling factors are known as Relative Sensitivity Factors (RSF) and are used to normalise the peak heights in order to extract elemental concentrations from the spectra.

For the purpose of our study, each peak was divided by the appropriate elemental RSF, and the normalised peak heights were determined. The background was

removed by simple linear subtraction. The peak heights for each element could then be compared in order to determine elemental concentrations. An example is shown below in table 2.1

| Element  | Counts | RSF | Normalised       |

|----------|--------|-----|------------------|

|          |        |     | Number of Counts |

| Silicon  | 3000   | .25 | 12000            |

| Oxygen   | 26400  | .66 | 40000            |

| Nitrogen | 1680   | .42 | 4000             |

| Total    | 31080  |     | 56000            |

Table 2.1: Sample elemental peak heights and normalisation in XPS

In this simplistic case, the silicon concentration would be 12000/56000= 21.5%, 71.4% for oxygen, and 8.1% for nitrogen.

The wide energy scan in figure 2.2 shows a carbon 1s peak at just above 950eV kinetic energy. This peak is attributed to hydrocarbon contamination on the surface of the sample<sup>6</sup>, which forms when the sample is exposed to air. Generally this surface layer is only a couple of monolayers deep and represents <10% of the total signal. However care must be taken, as carbon can continue to adsorb to the surface when in the analysis chamber. The additional carbon comes from the oil diffusion pumps, which help maintain the vacuum<sup>7</sup>. The effect of the carbon on measurements can be better understood by using angle resolved XPS.

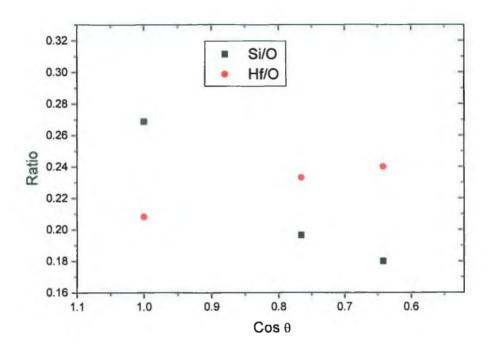

# 2.3 Angle resolved XPS (ARXPS)

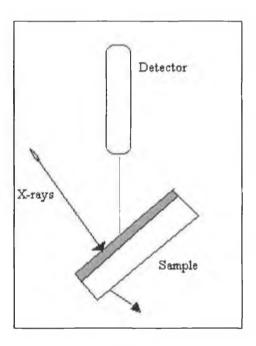

Angle resolved XPS was used in an attempt to study the depth profile of the layers. A more commonly used method to determine depth profile information is to perform an XPS scan followed by Ar<sup>+</sup> bombardment and then another XPS scan, in a sequential manner. However, Ar bombardment is found to damage the layer, introducing sub-oxides to the top surface of the layer<sup>8</sup> and contributing to

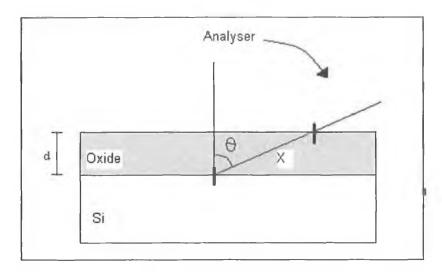

intermixing across the interface. Also, because the layers under consideration are so thin, control of the uniformity of the bombarding process becomes difficult. ARXPS involves a modification of conventional XPS, wherein the sample is rotated about it's own axis normal to the x-ray beam, and XPS spectra are taken at a number of angles with respect to the surface normal. This is shown schematically in figure 2.6a. When the sample is rotated to an angle  $\theta$  with respect to the detector, the path length for an electron to escape the layer at depth 'd' into the material becomes  $x = \frac{d}{\cos \theta}$ . This is illustrated in figure 2.6b.

Figure 2.6a Angle Resolved XPS. The sample is rotated about its own axis, thus varying the sample depth

Figure 2.6b Path length difference in ARXPS.

Because the XPS signal falls off exponentially with depth, a scan taken at an angle >0° will have a greater sensitivity to the upper part of the layer, and at extreme angles, virtually all of the signal comes from the overlayer. Assuming a sampling depth of 3.5nm for example, and an overlayer of thickness 2nm, 55% of detected electrons will originate from the overlayer. Moving to an angle of 30° means that 66% of detected electrons come from the overlayer and at 60°, the number rises to 75%. So, in this manner a chemical compositional depth profile of the layer can be determined.

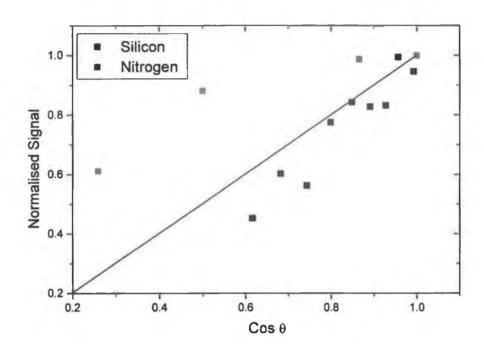

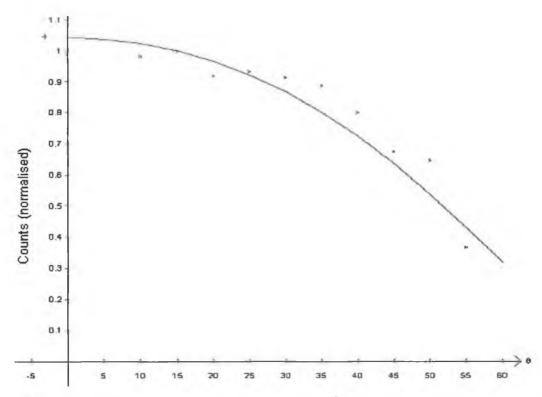

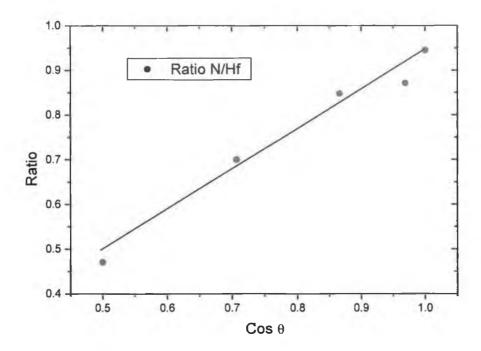

If an element is distributed uniformly in the material, its associated peak height should ideally remain constant with angle. However, surface hydrocarbon contamination attenuates the signal with a  $\cos\theta$  dependence and so the signal from a uniformly distributed element will in fact have a  $\cos\theta$  dependence because of the presence of this layer. If the peak drops off faster than this, it is likely that the element is concentrated deeper in the layer, as the off normal emission angle measurement is more sensitive to the surface. If the peak intensity drops off slower than  $\cos\theta$ , the element is primarily located at the surface. In the example shown in figure 2.7, for a SiON sample, the oxide silicon signal falls off slightly faster than  $\cos\theta$ , indicating that it has a slightly higher concentration in the lower part of the layer, whereas the nitrogen drops significantly slower than  $\cos\theta$ , indicating that it is heavily surface localised.

Figure 2.7 Normalised Si and N peaks show the change of signal with angle. The variation from  $\cos \theta$  behaviour indicates that the elements are not uniformly distributed through the layer.

De-convoluting the data so as to obtain a quantitative depth profile is an extremely complicated process and was not examined in great detail. Results are presented in Chapter 6 using an ARXPS software module by Tougaard<sup>9</sup>, to model the layers based on ARXPS intensities.

# 2.4 Soft XPS Using Synchrotron Radiation

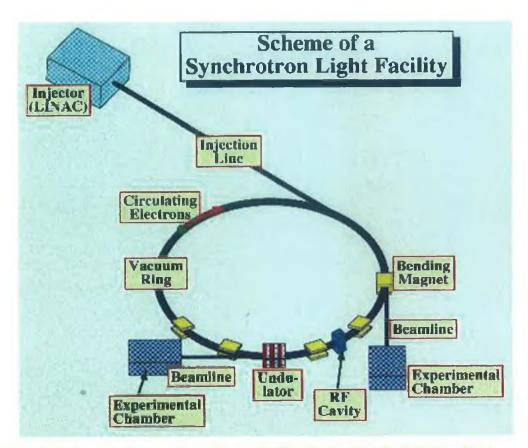

Soft XPS measurements were taken on the U4A beamline at the National Synchrotron Light Source (NSLS) at Brookhaven National Laboratory, New York. In the synchrotron, electrons travel under UHV at high velocity in a circular path, 'steered' by a magnetic field. While moving at velocities near the speed of light, the electrons emit electromagnetic radiation tangential to their direction of travel. This broadband electromagnetic radiation is made available to individual beamlines tangential to the storage ring. A synchrotron is shown schematically in figure 2.8<sup>10</sup>.

Figur 2.5 Schemot diagram of a synchrotron buildy, throwing how the light is produced

The main advantage of using synchrotron light is the broad spectral range of photon energies available which when compled with a monochromator, enables very high resolution spectra to be acquired.

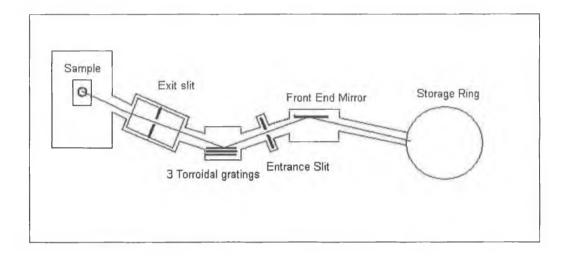

The D4A beamline at the NSLS is part of the VUV ring at the sacility. The beamline structure is shown at future 2.9. The light passes through a front end mirror, an erorance slit, a 3 noroidal grating monochromator, an exit slit and then into the analysis chamber where it is incalent on the sample. The monochromator is used to select the photon energy. The 3 gratings have 288, 822, and 2400 lines/min giving a ringe of photon energies. Typical scans were carried out with a step size of 0.03eV, a dwell time of 0.2a, in the photon energy range 20-180eV with an overall resolution (200meV on the Si 2p peak. This photon energy range is ideal for the study of the Si 2p some level, which has a binding energy of approximately 100eV, and also for the investigation of valence bond features.

The vacuum in the chamber is maintained by a rotary-backed turbo-molecular pump and ion pumps. All samples were loaded simultaneously to avoid having to break vacuum, and to ensure identical experimental conditions for each sample.

Figure 2.9 Schematic Diagram of the U4A beamline at the NSLS, showing the path followed by the light from the storage ring to the sample

Some considerations for synchrotron data analysis were:

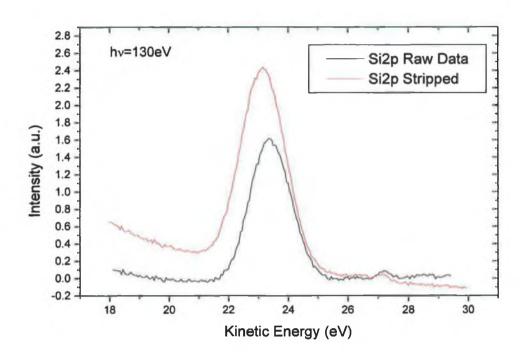

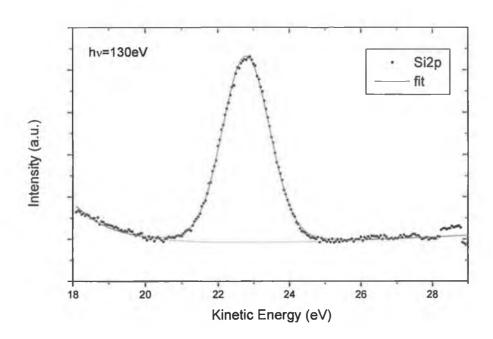

## Spin Orbit Stripping:

The finite resolution of the technique means that sometimes close-lying peaks cannot be resolved. In particular the  $Si2p_{3/2}$  and  $Si2p_{1/2}$  components are not well resolved. The two components in the Si2p peak arise from coupling between the magnetic fields of spin and angular momentum in the 'p' orbital. For this reason the silicon  $2p_{1/2}$  component was removed from the peak before analysis was performed. The software used also removes the background<sup>11</sup>. An example of a Si2p peak before and after stripping is shown in figure 2.10. The peak is much narrower when the  $Si2p_{1/2}$  component is removed.

Figure 2.10 Si2p peak before an after spin orbit stripping. The true single peak width can only be measured after stripping.

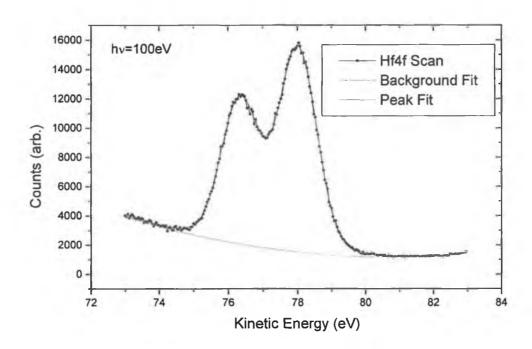

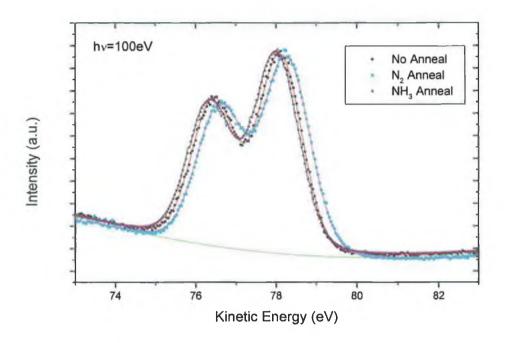

### Fitting:

Where necessary, peaks were fitted using a standard fitting program. Fitting peaks assists in determining the number of chemical environments present, and resolving the energy separation between them. Shown in figure 2.11 is a Hf 4f doublet peak at a photon energy of 100eV. In this case, the software calculates the best fit with an energy separation of 1.65eV between the peaks, and a branching (height) ratio of 0.73. The effect of varying preparation methods and fitting parameters was studied, to investigate peak broadening or shifting as a function of sample preparation procedures.

Figure 2.11 Hf4f peak fitted with a combined Gaussian-Lorentzian. The background is fitted with a polynomial.

# 2.5 X-ray Absorption Spectroscopy (XAS)

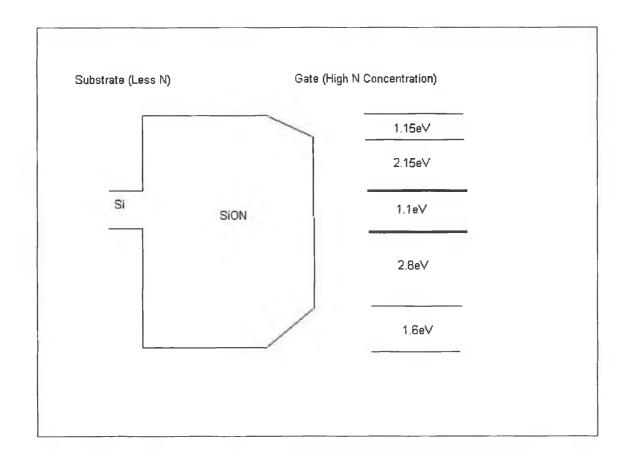

Conventional Soft XPS can be used to probe valence band electrons and thereby give information about the valence band offset. This represents the barrier height to tunnelling carriers in the valence band of the layer in question, as shown in figure 2.12. X-ray Absorption Spectroscopy (XAS) can in turn be used to calculate the conduction band offset, i.e. the barrier to tunnelling carriers in the conduction band. In XAS, monochromated synchrotron radiation light is used to scan through the absorption edge of a particular element causing the creation of core holes. The process results in the emission of x-rays due to de-exciting electrons filling the core holes. The intensity of this x-ray emission, which is measured in an x-ray spectrometer, is proportional to the partial density of states in the conduction band of that particular element. By comparing the XAS spectra for oxygen, for example, from SiO<sub>2</sub> and HfSiON, the conduction band offset can be measured.

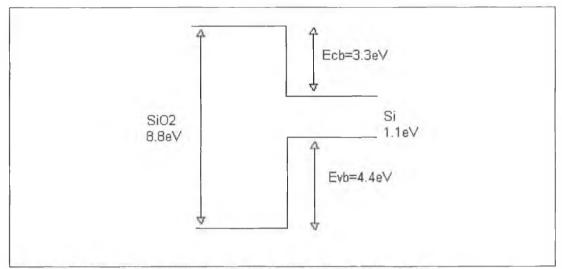

Figure 2.12. SiO<sub>2</sub> band structure showing conduction and valence band offsets

Previous results have shown that the incorporation of nitrogen alters the band structure of the Si/SiO<sub>2</sub> system<sup>12</sup>. In chapter 6, results are shown for HfSiON both with and without nitrogen, to examine whether similar effects are seen.

# 2.6 Secondary Ion Mass Spectroscopy (SIMS)

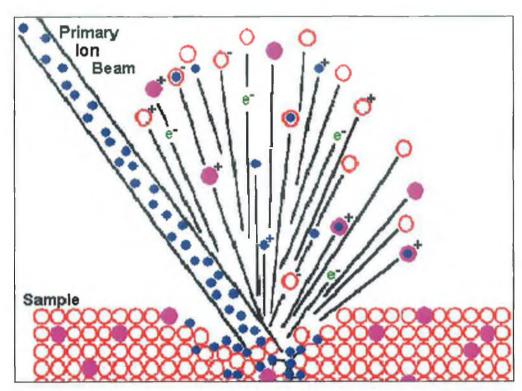

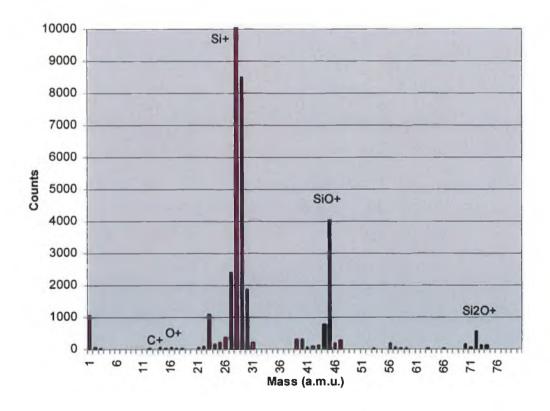

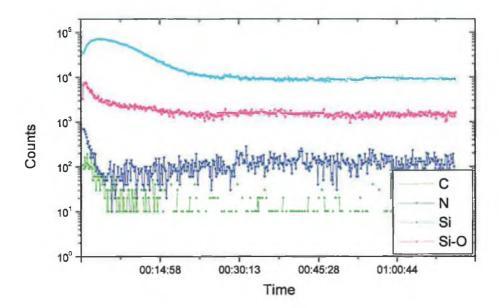

Secondary Ion Mass Spectroscopy (SIMS) is a valuable tool used to provide depth profile information about solid layers. During a SIMS measurement, the sample surface is slowly sputtered away with an ion beam. SIMS is thus a destructive technique. While the sputtering takes place, the fragments of the layer that are displaced are continually analysed in a mass spectrometer, so a depth profile can be constructed. The incident beam used in this study was a neutral Ar beam generated in a charge neutralisation chamber in order to avoid sample charging. The SIMS process is shown schematically in figure 2.13<sup>13</sup>. The displaced material consists of small concentrations of positive and negative ions of the elements present in the sample. These ions are analysed by a quadrupole mass spectrometer, which can be set up to sequentially accept ions of a certain mass/charge ratio. As the voltages on the rods of the spectrometer are varied, ions of varying charge to mass ratio are detected. An example mass/counts bar chart is shown in figure 2.14.

Figure 2.13 Schematic diagram of a SIMS experiment, showing how the primary beam interacts with the sold releasing secondary ions.

Figure 2.14 A typical SIMS spectrum; showing peaks associated with compounds of Si, N, C, and O atoms.

Silicon is seen at atomic mass 28 as expected. This peak represents  $\mathrm{Si}^+$ , or singly ionised silicon atoms. There is also a very small contribution from  $\mathrm{Si}$  at 14, which represents  $\mathrm{Si}^{2+}$ , which overlaps with  $\mathrm{N}^+$ . The overlap occurs because the technique cannot differentiate between two species with the same charge/mass ratio. The contribution of  $\mathrm{Si}$  at 14 is quite small in comparison with the  $\mathrm{N}$ , and so is ignored. There is also a peak attributed to  $\mathrm{Si}$  at 56 a.m.u. due to  $\mathrm{Si}_2^+$  i.e. two silicon atoms which are bonded together and pass through the analyser as a single mass fragment.

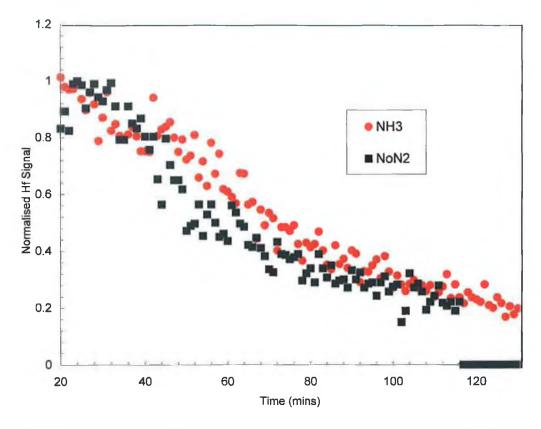

For this work, oxygen, silicon, nitrogen, and carbon (and hafnium for the HfSiON layers) were measured as a function of sample depth, by setting the ion beam at a very low sputter rate, and allowing the measurement to continue for several hours, as the layer is etched away. SIMS results are compared with depth profile information from ARXPS data.

#### 2.7 Summary

The techniques outlined in this chapter are powerful tools in obtaining vital chemical information about dielectric layers. XPS and ARXPS yield quantitative elemental concentration information and the angular aspect makes depth profiling of the layers possible in a non-destructive manner. This information can be cross-compared with SIMS results to give confidence in results. In this way, the effect of varying sample preparation on the final layer can be studied. The synchrotron based techniques can give information which can be related to the electronic properties of the layers, with conduction band offset being determined from X-ray absorption measurements, and valence band offset being measured from Soft-XPS. The effect on preparation conditions on these parameters can also be studied.

#### 2.8 References

<sup>1</sup>Z. Xu, B.Kaczer, J. Johnson, D. Wouters, G. Groeseneken, Charge trapping in metal-ferroelectric-insulator-semiconductor structure with SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>/Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> stack, J. Appl. Phys. 96 (3) (2004) pp. 1614-1619

<sup>2</sup>http://www.zaiko.kyushu-u.ac.jp/~watanabe/ SemiconSS/SCElectronic/PhotoEmission1.jpg

- <sup>3</sup> M.Cardona, L.Ley (Eds.). Photoemission in Solids, Pats 1 and 2, Springer, Berlin 1978.

- <sup>4</sup>M.P. Seah, W.A. Dench, Quantitative electron spectroscopy of surfaces: a standard data base for electron inelastic mean free paths in solids. Surface Interface Analysis, 1, (1979) pp. 2–11.

- <sup>5</sup> J. Schofield, Quantitative XPS analysis of the chemical composition of S1(Ag-O-Cs) photocathodes and its relation to the photosensitivity, J. Electron Spectrosc. Relat. Phenom. 8 (1976) pp. 129

- <sup>6</sup> K. Persy and N. Gurker, XPS—Investigation of contamination layers, Journal of Electron Spectroscopy and Related Phenomena, 13, (2) (1978) pp. 91-95.

- <sup>7</sup> L. Holland, Sources of surface contamination in vacuum evaporation systems, Vacuum, 13, (5) (1963), pp. 173-180.

- <sup>8</sup> E. Paparazzo et al, Evidence of SiO<sub>x</sub> suboxides at Ar ion etched silica surfaces, J. Vac. Sci. Technol. A, 8 (1990) pp. 2231-2235

- <sup>9</sup> QUASES-ARXPS, Version 1.1, S. Tougaard and T.S. Lassen, Denmark.

- <sup>10</sup> Trieste Synchrotron Website: http://www.elettra.trieste.it/visitors.

Charles Evans and Associates Website: http://www.cea.com/cai/simstheo/ionsput.htm

<sup>&</sup>lt;sup>11</sup> J. Roche, PhD Thesis, Page 71, Dublin City University (2002)

<sup>&</sup>lt;sup>12</sup> C. McGuinness, G. Hughes, J. Roche, D. Fu, J.E. Downes and K.E. Smith, Electronic structure of thin film silicon oxynitrides measured using soft x-ray emission and absorption, Journal of Applied Physics 94 (2003) pp. 3919-3922

# Chapter 3: Electrical Characterisation Methods for Gate Dielectrics

## 3.1 I<sub>G</sub>V<sub>G</sub> Tunnel Current Measurements

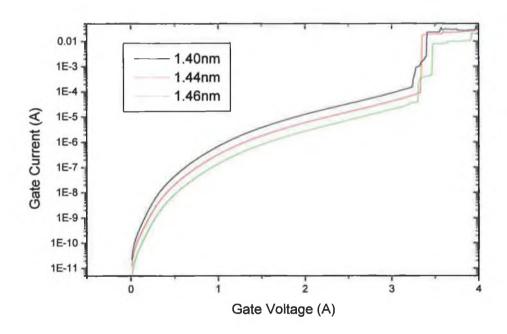

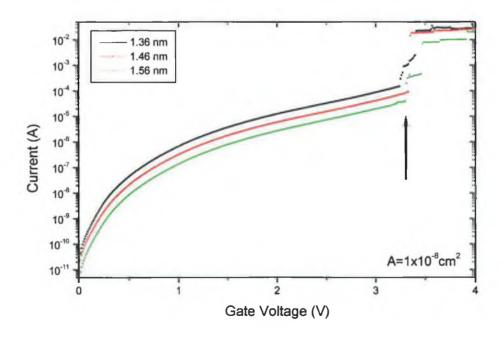

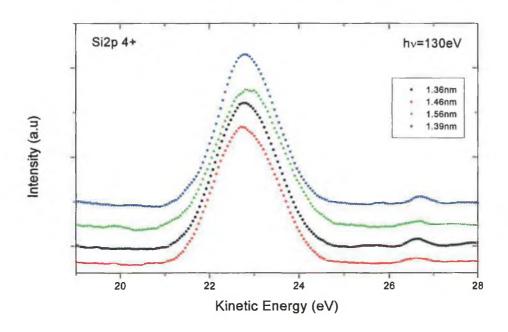

For the transistor gate dielectric thicknesses investigated in this thesis, the application of a gate voltage lower than the barrier height encountered by tunnelling electrons results in a small current flow. This is due to quantum mechanical electron tunnelling through the insulator potential barrier. A current-voltage (I-V) measurement can be used to determine the breakdown field of the layers under investigation as shown in figure 3.1. For these ultra-thin SiON samples, the breakdown voltage is approximately 24MV/cm. As tunnel current is exponentially dependent on barrier thickness, a reduction in thickness of just 0.2nm increases the current by a factor of 5.

Figure 3.1 Tunnel current characteristics for 1.36-1.56nm SiON samples. Breakdown voltage is approx 3.3V for these samples.

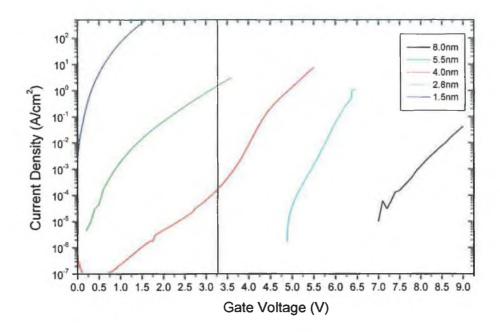

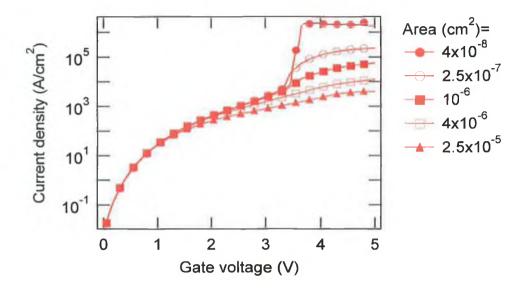

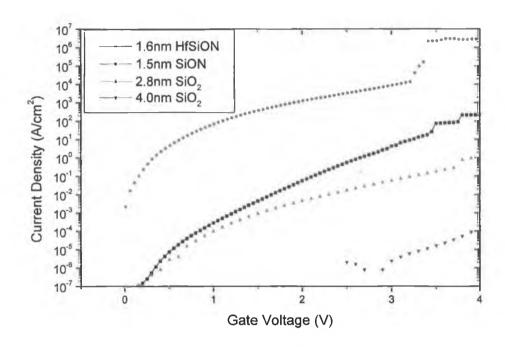

The significant increase in leakage current by reducing the gate oxide thickness is shown in figure 3.2, where the leakage current density is shown for a range of thicknesses.

Figure 3.2. Tunnel current characteristics for various oxide thicknesses illustrate the exponential rise in current for decreasing thickness. The transition from Fowler-Nordheim to direct tunnelling can also be seen

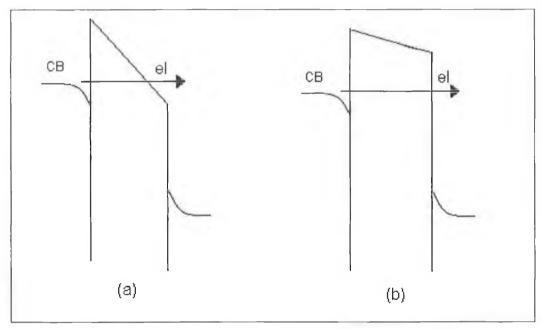

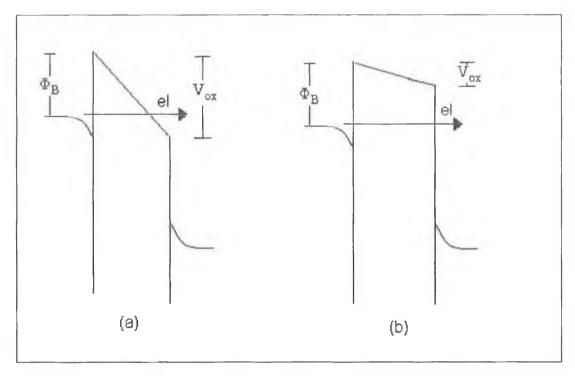

There are two possible current transport mechanisms, as discussed in Chapter 1, depending on the shape of the barrier encountered by tunnelling electrons. Fowler-Nordheim tunnelling takes place where the applied voltage across the oxide is greater than the barrier height (fig 3.3a), and the electrons tunnel through a triangular barrier into the SiO<sub>2</sub> conduction band prior to entering the silicon conduction band. However, when the oxide voltage is less than the barrier height, the electrons encounter a trapezoidal barrier (fig 3.3b), and tunnel directly into the conduction band of the Si. Depending on the substrate Si orientation, doping and other factors, the barrier height is generally accepted to be in the range 2.5eV-3.3eV for SiO<sub>2</sub><sup>1</sup> and nitrided SiO<sub>2</sub><sup>2</sup>. Therefore, depending on the oxide thickness the predominant tunnelling mechanism can vary in that in thick layers, the probability of direct tunnelling is greatly reduced. This is evident from figure

3.2, where the change in gradient can be clearly seen for the 4.0nm oxide. Direct tunnelling in the thinner layers causes a large increase in the current density and in some transport models is described using the Fowler-Nordheim equation and some multiplicative factor<sup>3</sup>.

Figure 3.3 (a) Fowler-Nordheim tunnelling through a triangular barrier, into the oxide conduction band. (b) Direct tunnelling through a trapezoidal barrier.

Though ultrathin oxides generally operate in the direct tunnelling regime, and Fowler-Nordheim tunnelling is no longer an issue, as high-k materials are incorporated with physical thicknesses of greater 4nm, Fowler-Nordheim tunnelling could again be a factor in I-V measurements and can yield some interesting information about the layers.

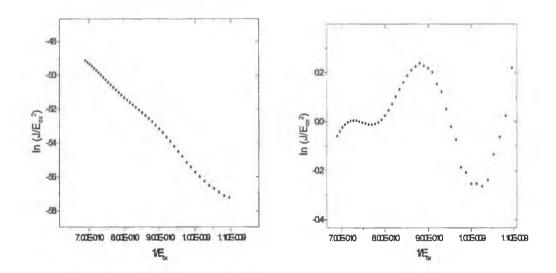

If the Fowler-Nordheim current profile is examined and  $\ln(J/E_{ox}^{2})$  vs. 1/F (fig 3.4a) is plotted, where F is the oxide field and J is the current density, a straight line plot (from the FN-tunnelling equation) is expected. However in 3-6nm oxides, a slight oscillatory component on the straight line (fig 3.4b) is present, which arises from the quantum reflection of electrons with the correct wavelength at the SiO<sub>2</sub> interface<sup>4</sup>.

Information about the  $SiO_x$  transition region width at the interface can be gained from the shape and width of the oscillations<sup>5</sup>. This is because the  $SiO_x$  region

reduces the distance through which the electrons have to tunnel, as there are available states in this region, and the shape and position of the oscillations reflect this. Using the interference model proposed by Mao et al<sup>4</sup>, we have observed similar differences in applied voltage and observed voltage at the current oscillation extrema, corresponding to a transition width of ~.35nm, approximately 10% of the total for the 4nm oxides used.

Figure 3.4 A Fowler Nordheim plot, with the tunnel current oscillations extracted from the straight line fit. The oscillations are extracted by subtracting the linear fit from the FN-equation, from the actual experimental data

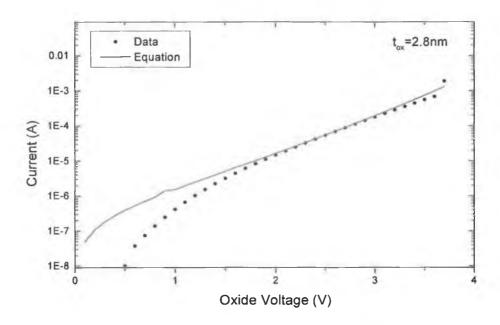

Direct tunnelling proves more difficult to describe accurately as shown in figure 3.5. Experimental data for a 2.8nm oxide is shown alongside the model for direct tunnelling outlined in chapter 1. Tweaking of parameters, such as barrier height (3.5V in the example), effective mass (0.45m\*<sub>0</sub> in the example), and oxide thickness is required to acquire the close fit in figure 3.5 and even still, like many approximations<sup>6</sup>, it has significant shortcomings in the low-field range. The model also begins to deviate from experimental data at the onset of Fowler-Nordheim tunnelling at around 3.3V as expected.

Figure 3.5 Experimental direct tunnelling data fitted with a model based on the WKB approximation for a capacitor with active area, n+ gate, p-type substrate. The model is quite inaccurate in the low field range.

# 3.2 Time Dependent Dielectric Breakdown

The primary function of the gate oxide is to act as an insulating layer for the lifetime of the device in which it is incorporated. However, when an oxide is stressed using either constant voltage, or constant current stress at high field, it is found to gradually lose its insulating properties over time, until eventually the layer suffers electrical breakdown. The main focus of the electrical measurement based part of this thesis is on the reliability of the layers under consideration, the degradation of the layers during their lifetime, and the operation of MOSFETs as oxide parameters degrade. This section deals with the characterisation methods used in the study.

Dielectric breakdown has long been attributed to the build-up of some sort of defect (now assumed to be electron traps) over time where, upon reaching a local critical defect density, oxide breakdown occurs. Early models consisted of dividing the oxide into cells, and as the electrons traps built up at random positions, they filled up these cells<sup>7</sup>. Breakdown was triggered when any one cell had exceeded the critical number of traps, which form a conductive path from

anode to cathode. However, problems with this method included the fact that the model could trigger breakdown once the critical number of traps was reached in a cell, even if the traps didn't reach from anode to cathode, but were condensed in the middle of the cell. Also, a local critical density could be reached but the traps may be distributed in neighbouring cells, and breakdown would not be triggered.

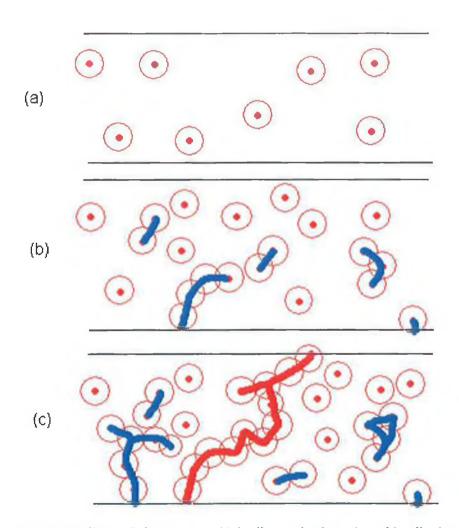

An advancement of this model using percolation theory was proposed by Degraeve et al<sup>8</sup>, whereby the traps form at random in the oxide, but they can only form a conductive chain with other traps if they are within a certain percolation distance of each other. When a conductive chain occurs from anode to cathode, breakdown occurs. The process is illustrated schematically in figure 3.6

Figure 3.6 Buildup of electron traps (a) leading to the formation of localized conduction paths within the oxide (b), and ultimately the formation of a conduction path from anode to cathode causing oxide breakdown (c).

From this figure, a number of effects of the random nature of trap generation on breakdown are clear. Firstly, because of the random location of trap generation, the time-to-breakdown will be statistically distributed; it becomes clear as well that the trap generation rate is a critical factor in determining time to breakdown.

Also, the effect of decreasing dielectric thickness on the time-to-breakdown parameter (t<sub>bd</sub>) becomes obvious. As fewer traps are required to form a breakdown path, the overall density at which breakdown occurs will generally be lower, and breakdown will occur much quicker for the same trap generation rate <sup>10</sup>. The next section outlines the statistics involved in describing oxide breakdown.

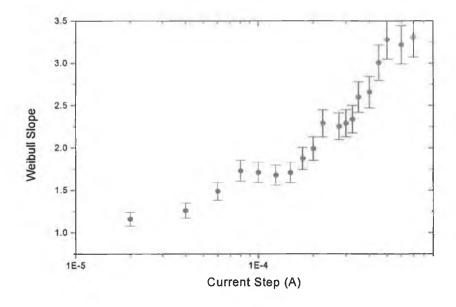

#### 3.2.1 Weibull Statistics

If a number of identical oxide samples are stressed under the same conditions, a wide variety of  $t_{bd}$  values will occur. The reason for this, as mentioned, is the buildup of traps at random locations, leading to the possibility of a conduction path forming at both low and high trap densities, depending on the particular trap location profile for each oxide. The distribution is described by Weibull statistics [9]. This distribution is used a lot in engineering applications where 'weakest link' processes occur. The function is:

$$F(t) = 1 - \exp\left[-\left(\frac{t}{\eta}\right)^{\beta}\right]$$

Eq 3.1

where,  $\beta$  is the Weibull Slope of the distribution (shape factor) and  $\eta$  is the 63% (scale factor) which is the time at which 63% of a certain sample set will have broken, independent of the number of samples tested.

Furthermore, by taking the natural log of both sides it can be shown that,

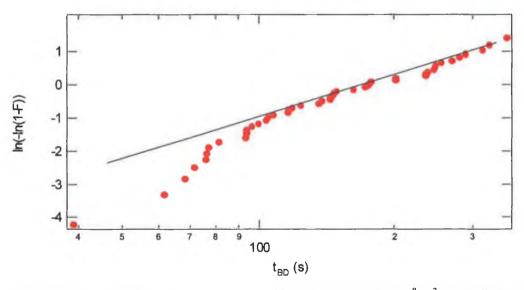

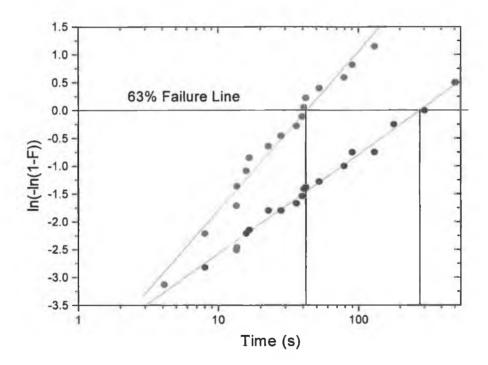

$$\ln\left[-\ln\left(1-F(t)\right)\right] = \beta \cdot \ln(t) - \beta \cdot \ln(\eta) \quad \text{Eq 3.2}$$

This is the usual way in which a set of breakdown data is presented, and a sample Weibull plot is shown below in fig 3.7, for a 1.5nm oxide. It has a Weibull slope of 2.2. The slope is calculated from a "maximum likelihood fit", which ensures a more accurate extraction than a least squares fit. The reason for this is that the "maximum likelihood" method gives more weight to time intervals in which breakdown occurs more often i.e. from 80-300 seconds in figure 3.7. The slope is then better fitted to the times at which breakdown has occurred more often. In thicker oxides, the distribution is made of 2 parts, an intrinsic breakdown slope and a flatter extrinsic one, at the low end of the t<sub>bd</sub> scale, attributed to process induced defects and oxides which are already broken prior to stress<sup>11</sup>. In today's low defect density, small area samples, the two modes are no longer distinguishable. This work focuses on intrinsic breakdown, which is due to electron flux and trap generation rather than processes related effects.

The Weibull slope and 63% values are key factors in investigating how the oxide layers will behave at lower voltages. A low Weibull slope is equivalent to a very wide distribution of breakdown times, whereas a higher slope means all the breakdowns occur in a narrower time window. The significance of the Weibull slope in reliability projections will be made clear in the next section.

Figure 3.7 Sample Weibull plot for a 1.5nm oxide with an area of 1x10<sup>-8</sup>cm<sup>2</sup>. Weibull plots are fitted with the maximum likelihood method to extract the Weibull slope.

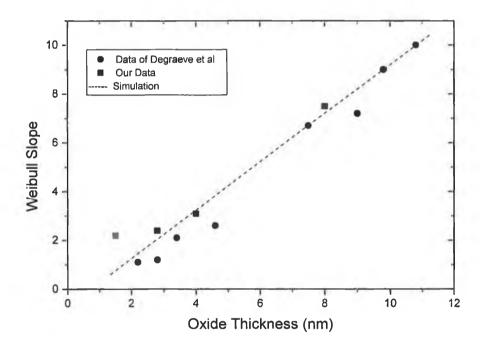

As mentioned, the trap density at breakdown becomes lower as oxide thickness is reduced. If we look at t<sub>bd</sub> statistics for decreasing thickness, we see that the Weibull slope also reduces for reducing thickness<sup>8</sup>. The reason for this is that as thickness is reduced, the number of traps required to form a breakdown path is reduced. Thus there is a wide statistical variation in the time it will take to form a path. In a thicker oxide, where 6-7 traps are required to form a path, the statistical spread is far less and the distribution is much steeper.

Figure 3.8 shows this relationship for our data, and for that of Degraeve et al<sup>8</sup>, and the effect as predicted by the percolation model. The reason for the high Weibull slope observed at 1.5nm is discussed in chapter 4.

Figure 3.8 Variation of Weibull slope with oxide thickness for oxide from 1.1 to 11nm. The percolation model provides a good fit to the data

The area of the test structure under consideration is also important in determining the time to breakdown. The distributions of devices of different areas are related by 12:

$$\frac{\eta_1}{\eta_2} = \left(\frac{A_2}{A_1}\right)^{\gamma_\beta}$$

Eq 3.3

where  $\eta$  is the 63% breakdown time, A is the device area, and  $\beta$  is the Weibull slope. So, as area is decreased, the time to breakdown increases as expected. Thus for a thin oxide where  $\beta$  is low, e.g. 2.2, a reduction in area of 1 order of magnitude results in a  $t_{bd}(63\%)$  almost 3 times higher.

#### 3.2.2 Reliability

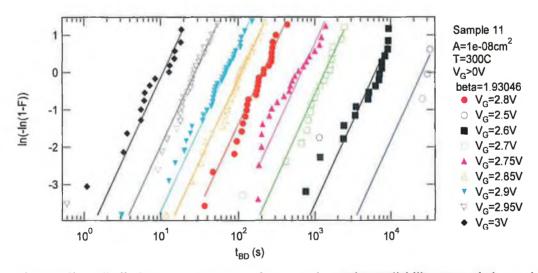

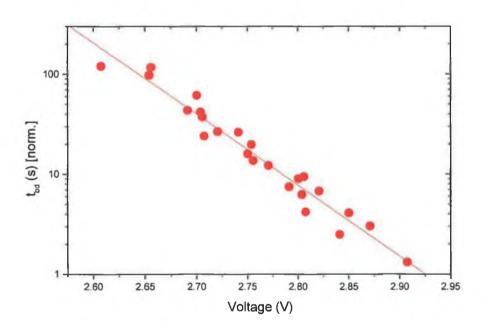

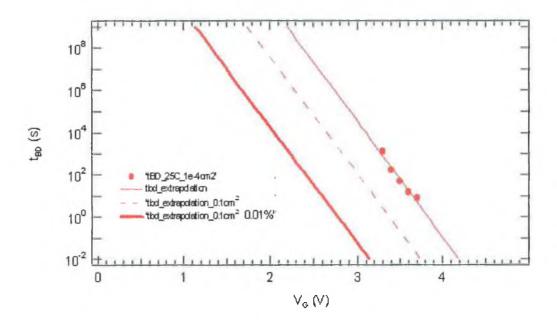

When fabricating an oxide layer for use in a device, it is generally expected that the layer will maintain its insulating properties and perform as expected for the lifetime of the device which is normally taken as 10 years. However, as the  $t_{bd}$  is statistically distributed, and many measurements are needed to accurately observe the distribution, it is impractical to stress oxides at operating voltage because the modal  $t_{bd}$  will be ~10 years, and in some individual oxides, 100's of years! The solution is to use accelerated lifetime tests, whereby an elevated stress voltage is used such that the modal  $t_{bd}$  occurs within a measurable time frame, generally less than 10000s. Measurements are made at multiple stress voltages, and it is then possible to make an extrapolation to the operational voltage and examine reliability. A data set for such a reliability examination is shown in figure 3.8b

Figure 3.8b Weibull plots at many stress voltages used to make a reliability extrapolation to the low field range. Weibull slope is seen to be independent of stress voltage. Devices: Capacitors with active area, p+ gate and active, n-type substrate.  $t_{ox}$ =1.11nm EOT. Breakdown criteria=large current jump

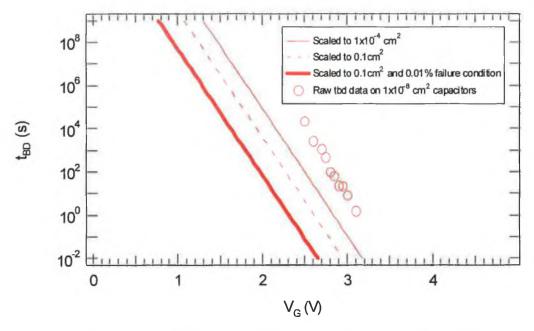

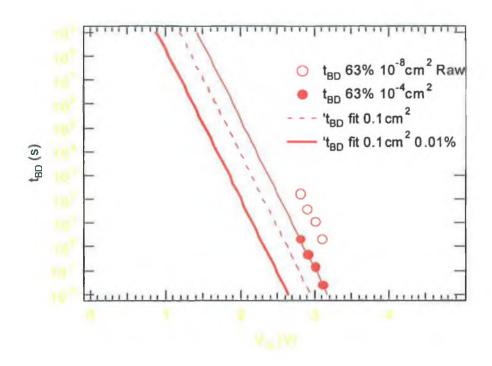

In this case stress voltages from 2.5V-3V are used for the stress. Obviously, using many measurements means better accuracy in the Weibull slope, and more points on the extrapolation line to the low field range. In this case we have used ~200 samples and so the error in the Weibull slope  $(\frac{1}{\sqrt{n}}) = 0.07$ , so the Weibull slope is 1.93 ± 0.13. To make the reliability estimate, we take the  $t_{bd}(63\%)$  values, corresponding to y=0 on the Weibull plot, and plot  $t_{bd}(63\%)$  vs. gate voltage as shown in figure 3.9, and extrapolate back to operating voltage.

Figure 3.9 Reliability extrapolation using  $t_{bd}63\%$  data from figure 3.8 including area and percentile scaling. Maximum operating voltage for any given lifetime requirements can be deduced from the plot.

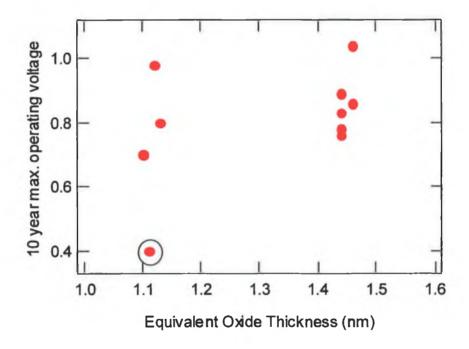

The raw data (open circles) acquired on devices of area  $1 \times 10^{-8} \text{cm}^2$  is first scaled to an area of  $1 \times 10^{-4} \text{cm}^2$  using the area scaling equation outlined earlier in this chapter. This allows data collected at a number of areas to be normalised to one reference area, however in this example only one area is used. The next step in making a reliability estimate is to scale to a typical chip area  $(0.1 \text{cm}^2)$  making the assumption that individual oxide breakdowns will stop the chip functioning. Since the area of a chip is so much larger than the area of individual gate dielectrics, the reliability estimate is essentially a worst-case scenario. Furthermore, our data points represent the  $t_{bd}(63\%)$  data, which is obviously an unacceptably high failure rate, and thus the data is further scaled to a 0.01%

failure rate condition, giving the final reliability extrapolation (bold line) and allowing a maximum operating voltage for a required lifetime to be deduced. From the above diagram, an operating voltage of 0.8V would give a projected lifetime well in excess of  $3x10^8$ s (10 years)

The Weibull slope affects the area scaling as mentioned previously; a high slope equates to  $t_{bd}$  distributions at different areas being closer together, and so the extrapolation lines (scaled to  $0.1 \text{cm}^2$  and  $1 \times 10^{-4} \text{cm}^2$ ) are drawn closer to the raw data (acquired at  $1 \times 10^{-8} \text{cm}^2$ ). This obviously improves the maximum operating voltage for a desired lifetime. The Weibull slope also affects the percentile scaling (bold line). The reason for this is illustrated in figure 3.10. A distribution with a high  $\beta$  has a  $t_{bd}(63\%)$  that is closer to the low percentile values than a distribution with a high  $t_{bd}(63\%)$ .

Figure 3.10 The effect of Weibull slope on percentile scaling. A low slope stems from a wide statistical spread and means a greater gap between the 63% time and the low percentile breakdowns.

For example in figure 3.10, low percentile values are found at  $\sim$ 5 seconds. The  $t_{bd}(63\%)$  for the distribution with the high slope is  $\sim$ 40s and for the low slope  $\sim$ 280s. So much less scaling is required in going from  $t_{bd}(63\%)$  to low  $t_{bd}(0.01\%)$  in the sample with the high slope. In figure 3.9, this would mean the bold line would be drawn closer to the raw data, thus improving the reliability outlook. It is clear then that for area and percentile scaling, a high  $\beta$  is desirable to improve the reliability prediction. The inherent properties of the oxide, which determine  $\beta$ , will be discussed in detail later in the thesis.

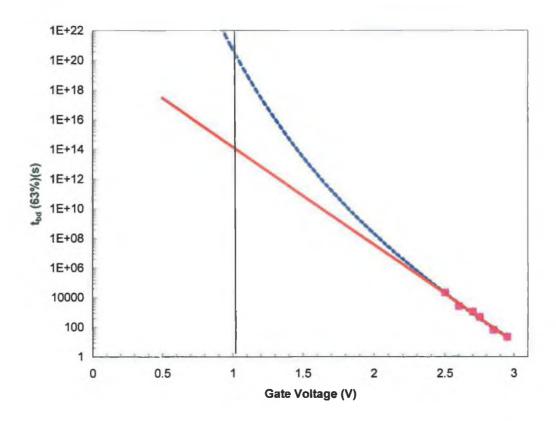

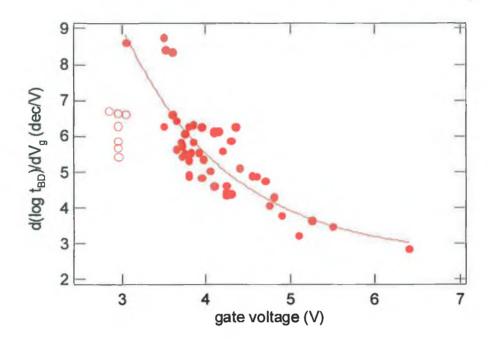

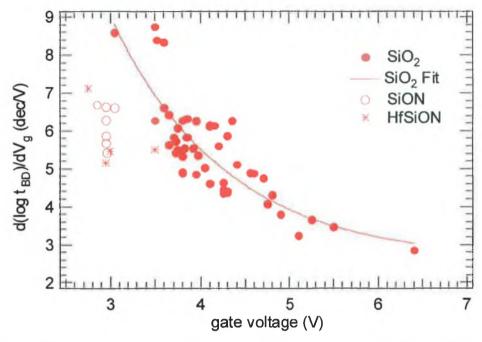

On examining figure 3.9, the slope of the extrapolation is obviously another important factor in determining reliability. The slope is known as the voltage acceleration  $^{13}$  ( $\gamma$ ) and is again an inherent property of the oxide. There are however a number of issues with making such an extrapolation. Firstly, there is nothing to suggest that the oxide suffers that same degradation at low field where it is impractical to measure, as it does in the measurement range. This however is difficult to confirm due to the time such measurements take, and the argument is based on theory rather than practice. The other more relevant issue is the extrapolation method used. In figure 3.9 we have used a linear extrapolation to the low field ( $t_{BD}$ = $t_0$ .exp(- $\gamma$ .V<sub>G</sub>)) to gauge reliability. However Wu et al<sup>14</sup>, have suggested that the correct extrapolation obeys a power law, where the voltage acceleration ( $\gamma$ ) is gate voltage dependent (i.e.  $\gamma$ =( $\delta$ (ln( $t_{bd}$ ))/ $\delta$ V). There are a number of reports in the literature discussing the correct model and the physical origin of the field acceleration model obeyed by the oxide<sup>15,16</sup>. These will be discussed in the next section.

The difference between the two models in determining  $t_{bd}$  at low field is shown in figure 3.11. When extrapolated using the linear extrapolation model, a  $t_{bd}$  of  $\sim 1 \times 10^{14} s$  is expected. Using the power law model on the same data yields a  $t_{bd}$  of  $> 1 \times 10^{20} s$  in this case. Again however, the timescale for making measurements to support either model is impracticable, and both are supported by theory rather than experiment. For this work, all reliability estimates are made using the linear extrapolation model, as it represents the worst case.

Figure 3.11 Using the power law model (blue) for reliability extrapolations leads to extremely favourable reliability outlooks when compared with the linear extrapolation model

#### 3.2.3 Breakdown Mechanisms

It is known that the degradation and breakdown of gate oxides is due to charge traps forming within the layer during its lifetime. However, the trapping process; that is, the physical origin of the traps, is not well understood. This section outlines the types of charge traps that form in the oxide, and the most commonly referred to mechanisms in the literature as to how they are created.

# 1. Fixed Oxide Charge 17

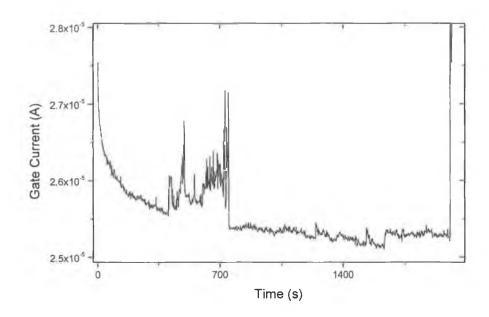

During a constant voltage stress on an nMOSFET using substrate injection in thick SiO<sub>2</sub> layers (>4nm), the current is found to initially increase, indicating the presence of positive charge trapped in the oxide. After a time, the increase stops

and the current begins to decrease, as negative charge trapping dominates, though this effect is only slight for layers of this thickness. In ultra-thin SiON, a very small increase in the current is detected, again indicating the presence of positive trapped charge. No decrease is observed before breakdown for ultra-thin layers. These observations suggest that positive trapped charge resides at the interface, and because there is little bulk in ultrathin layers, the negative charge buildup, which may form in the bulk, is negligible.

Extending the discussion to high k materials, hafnium silicate shows only a decrease in gate current, for thicker layers, indicating that negative trapped charge in the bulk is dominant, if it follows the same trends as SiON.

In thinner HfSiON layers, the rapidly increasing leakage current during voltage stress (Stress induced leakage current<sup>18</sup> is discussed in the next section) makes it impossible to judge whether positive or negative charge trapping is dominant.

#### 2. Interface Traps

Another widely studied mechanism is the presence of traps at the insulator/Si interface<sup>19</sup>. It is generally accepted that interface traps are created through the same mechanism as bulk traps, but due to the strained layer of SiO<sub>x</sub> at the interface (which originates from the structural mismatch between Si and the insulator) where the density of localised states is increased, the trap generation rate is different from that in the bulk<sup>20</sup>. The interface trap densities are measured by charge pumping in this work, a technique that is outlined in section 3.4. The interface trap generation rates for both SiON and HfSiON are discussed in Chapters 4 & 5 respectively.

#### 3. Neutral Electron Traps

During the stressing of an oxide, neutral electron traps form throughout the layer<sup>21</sup>. There is extensive information in the literature to suggest that it is these traps that build up, form a percolation path and result in the breakdown of the oxide<sup>8</sup>. However, because the traps are neutral, they require a filling step to make them electrically visible. Neutral trap densities cannot be measured for ultrathin

oxides, as the full traps have a tendency to empty before they can be measured. There are 3 models that suggest how these traps are formed:

The *anode hole injection*<sup>22</sup> model assumes that some electrons that arrive at the anode have sufficient energy to release an energetic hole back into the oxide. These energetic holes then create oxide traps as they tunnel. However, this model fails to explain the temperature dependence of oxide degradation.

The *hydrogen release*<sup>23</sup> model views the holes injected at the anode as not taking place in the trap generation process, but that the hole injection mechanism happens alongside the release of hydrogen (used to passivate the interface) into the oxide at the anode that generates traps. Thus, the measured hole fluence is simply a monitor of the trap generation process as both are dependent on the energy released at the anode by tunnelling electrons.

Finally, the *electric field* <sup>21</sup> model assumes that the energy released by tunnelling electrons at the anode is not responsible for trap generation, but that simply the electric field gives sufficient energy to the oxide to stimulate the process that leads to trap generation.

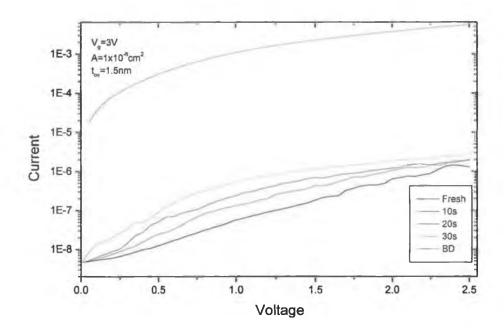

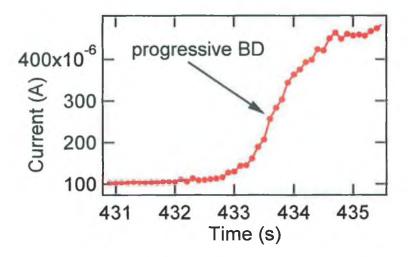

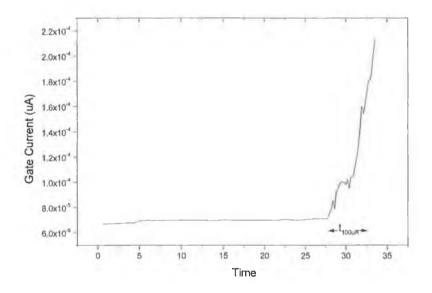

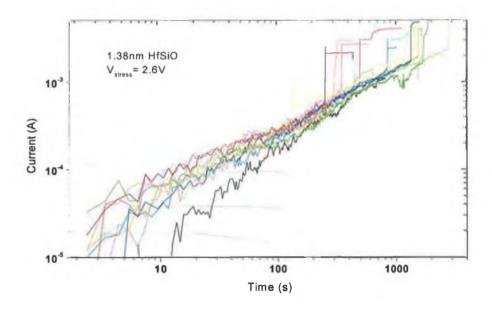

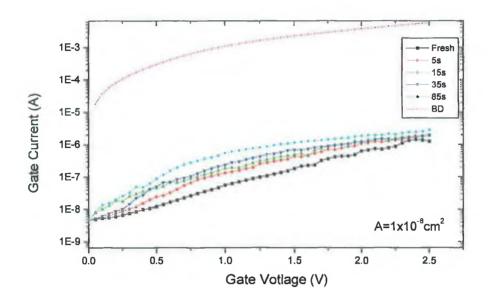

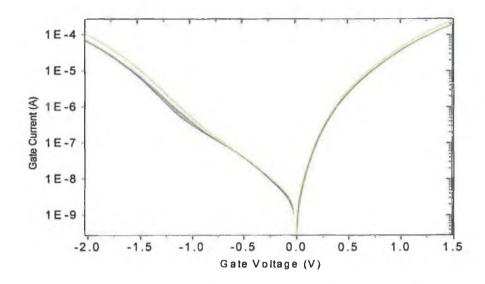

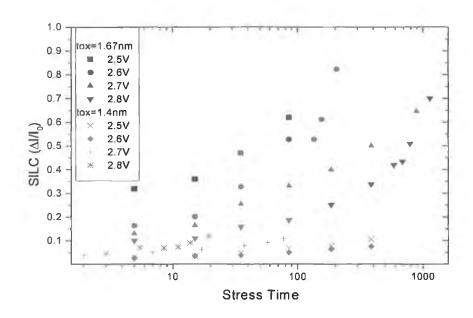

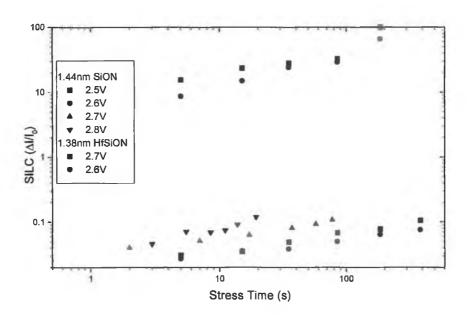

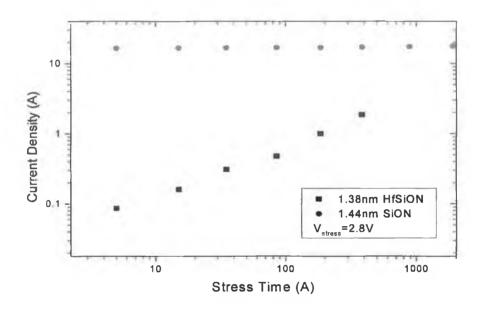

# 3.3 Stress Induced Leakage Current

It was noted in the 80's by Maserijian and Zamani<sup>24</sup>, that the I-V curve of an oxide that had undergone stress differed from that of a fresh oxide, in that the stressed I-V displayed a higher current in the low field range, a so called stress induced leakage current (SILC). The effect is shown in figure 3.11, where a device is stressed for a set time, and then an I-V measurement is performed, and so on until breakdown. The effect is dominant at low field as at the high field, the I-V curves converge again. The predominant mechanism responsible for SILC is believed to be trap assisted tunnelling through neutral electron traps formed during stress <sup>25</sup>. Direct tunnelling at high field swamps this effect, and this is the reason why the I-V curves are similar at high field.

Figure 3.12 The buildup of SILC during a constant voltage stress. The increase in SILC can be directly correlated to the number of neutral electron traps in the layer.

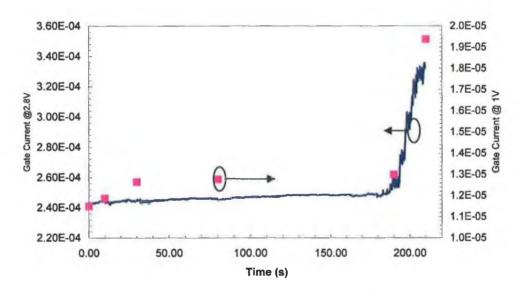

A more conventional way to measure the SILC is to stress the layer at high field, then stop the stress and measure the SILC at low field, such that no further degradation is taking place during the sense measurement. The time interval between the stress and sense measurements is important, as SILC has a transient component associated with the discharging of traps near to the interface. This is less important in thinner oxides, where the steady state trap assisted tunnelling component dominates the current flow.

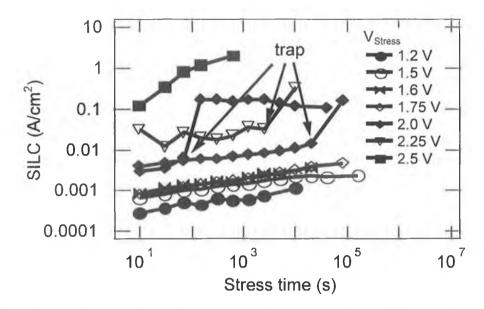

An example of a SILC measurement for an ultrathin layer is shown in figure 3.13 taken from<sup>26</sup>. The slight rise in SILC as the stress continues is attributed to positive charge trapping, and the formation of traps near to the interfaces that assist the tunnelling process. However, measurements at 2V and 2.25V show a sudden increase in SILC. This corresponds to the formation of a 'well placed' trap, in the middle of the oxide, the location of which is ideal for the trap assisted tunnelling process. The formation of such a trap in a thin oxide is often an indication that breakdown will soon follow.

Figure 3.13 Increase in SILC with stress time at a number of stress voltage during CVS. The formation of a "well placed" trap causes a sharp rise in the  $SILC^{26}$ .

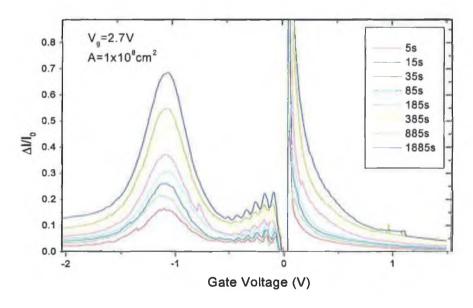

The level of SILC is a good measure of the neutral electron trap density in the oxide<sup>27</sup>, and can be used for degradation and breakdown predictions. SILC is a problem in memory devices, as stored charge can leak out, causing information to be lost. Also, in MOSFETS, the SILC causes a higher consumption of power, which can be problematic for portable devices.

# 3.4 Detection of Interface Traps by Charge Pumping

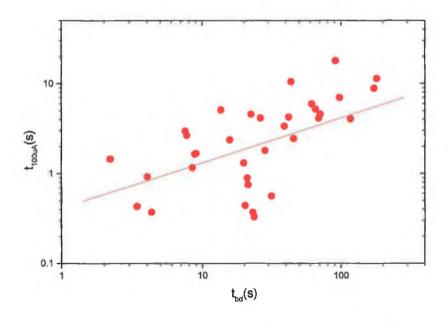

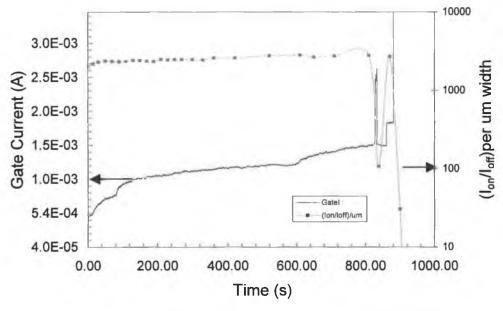

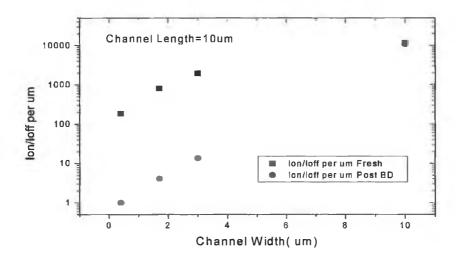

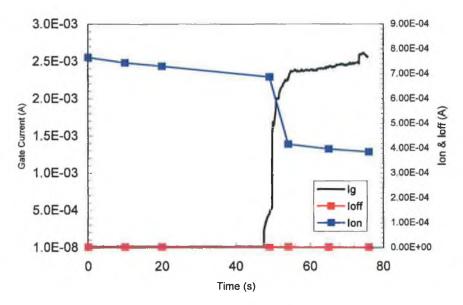

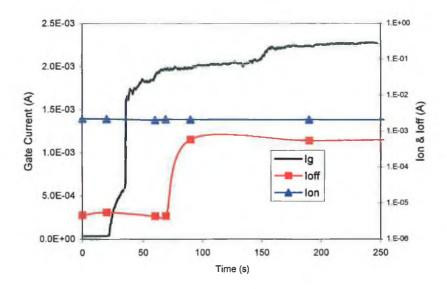

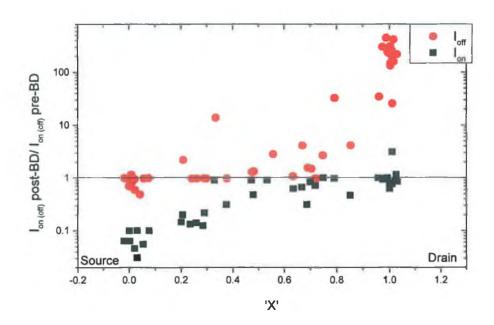

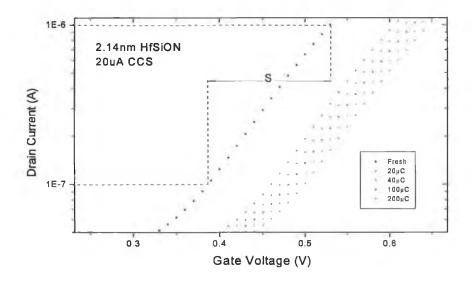

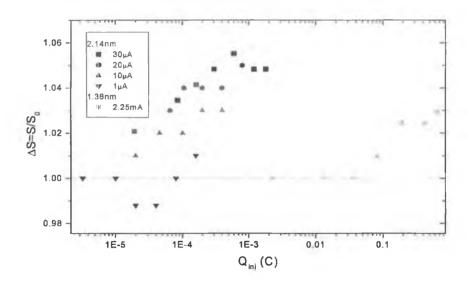

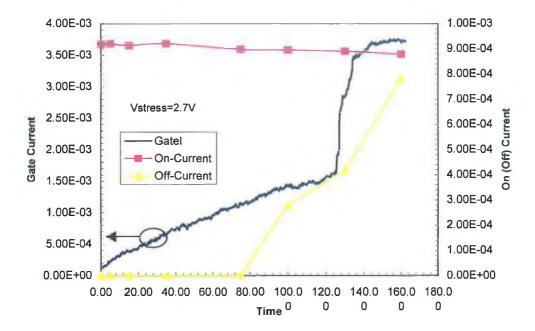

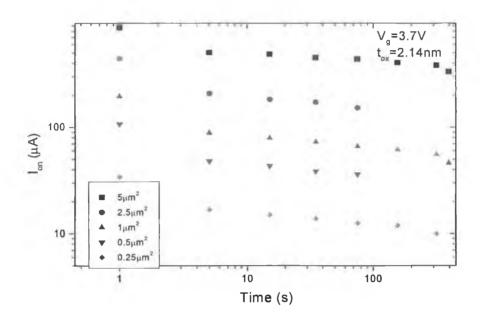

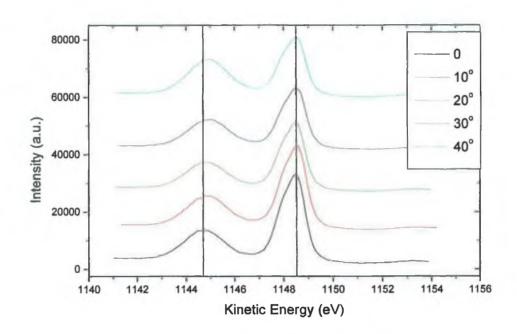

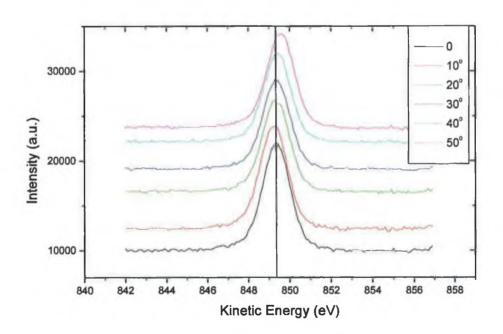

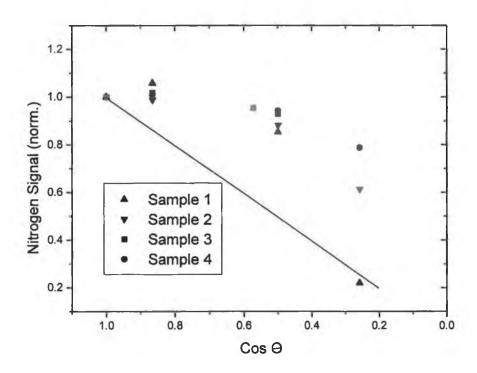

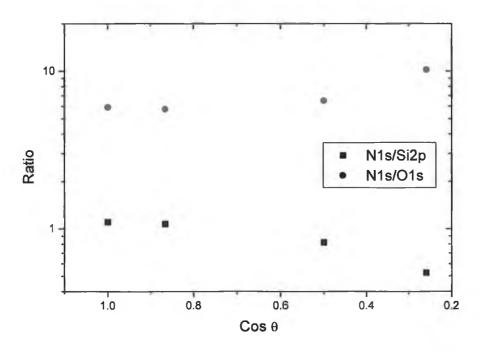

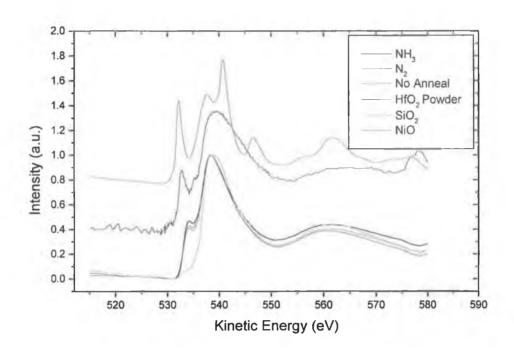

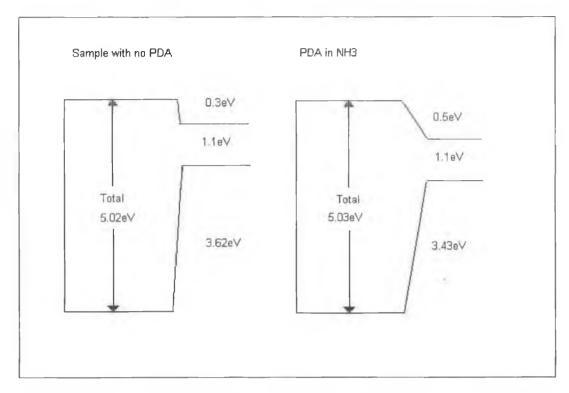

Traps in the strained Si/dielectric interfacial region are of particular interest as it is these traps that are closest to the critical channel region of the device. For this reason, a reliable method of determining the interface state density is important in evaluating new dielectric layers. Charge pumping is employed as the primary method of interface state detection, as it is particularly effective for ultra-thin layers. This is because it remains accurate even when the gate leakage current is high, and its analysis is simpler than that of Deep Level Transient Spectroscopy (DLTS) and more reliable than methods based on 1/f noise analysis<sup>28</sup>.