# Compromising Emissions from a High Speed Cryptographic Embedded System

A Thesis Submitted in Fulfillment of the Requirements for the Degree of Master of Engineering (Electronic Engineering)

By

Damien O'Rourke

B.Eng., MIEEE

School of Electronic Engineering Faculty of Engineering and Design Dublin City University

> Research Supervisor Prof. Charles McCorkell Msc, PhD, CEng, FIEI, FIEE

> > September 2003

### **Declaration**

I hereby certify that this material, which I now submit for assessment on the programme of study leading to the award of Master of Engineering is entirely my own work and has not been taken from the work of others save and to the extent that such work has been cited and acknowledged within the text of my work.

Signed: Davie O' lask

Date: 01-10-03

### **Acknowledgments**

I would like to thank my research supervisor and colleague Prof. Charles McCorkell for all his support and advice over the duration of this thesis. Without his guidance, encouragement and patience, this work would have invariably been a lot more difficult.

I would also like to express a special thanks to Prof. Michael Ryan for sharing his invaluable knowledge in the area of cryptography and for his complete patience in helping me whenever it was needed.

I am grateful to Frank Flanagan and Richard Rooney for all their help throughout this research and also to Dr. Liam Barry for making me an "honorary" member of his lab and for including me in all the lab events.

I would especially like to thank my parents Margaret and Terry for supporting me in every decision I have ever made and for always being there.

To my dear friend and girlfriend Claire. I couldn't have done this without you.

I am very grateful to the Mr. Conor Maguire, Mr. Robert Clare, Mr. Liam Meany, Mr. John Whelan, Mr. Jim Dowling, Mr. Liam Sweeney, Mr. Paul Wogan, Mr. Billy Roarty and Dr. Pascal Landais for assisting me in various aspects of my work in Dublin City University. Thank you all for your time and friendship.

I would like to thank my friends and colleagues here at the University: Eoin, Clauss, Paul, Frank, Brendan, Prince, Ola, Antonia and Ashling. Your friendship and support has been invaluable, thank you all.

I would like to thank all my friends for being there and for lending me an ear when things got tough. I would especially like to thank Robert Clarke and Colin Smith who being the nerds they are, kept me highly motivated.

Last but certainly not least, I would like to thank God for blessing me with such a beautiful family and friends, and for helping me to come this far.

# **Dedication**

To Mam, Dad and Claire - this is for you.

#### **Abstract**

### Compromising Emissions from a High Speed Cryptographic Embedded System

Damien O'Rourke, B.Eng., MIEEE

Specific hardware implementations of cryptographic algorithms have been subject to a number of "side channel" attacks of late. A side channel is any information bearing emission that results from the physical implementation of a cryptographic algorithm. Smartcard realisations have been shown to be particularly vulnerable to these attacks. Other more complex embedded cryptographic systems may also be vulnerable, and each new design needs to be tested.

The vulnerability of a recently developed high speed cryptographic accelerator is examined. The purpose of this examination is not only to verify the integrity of the device, but also to allow its designers to make a determination of its level of conformance with any standard that they may wish to comply with.

A number of attacks were reviewed initially and two were chosen for examination and implementation - Power Analysis and Electromagnetic Analysis. These particular attacks appeared to offer the greatest threat to this particular system. Experimental techniques were devised to implement these attacks and a simulation and microontroller emulation were setup to ensure these techniques were sound.

Each experimental setup was successful in attacking the simulated data and the micr-controller circuit. The significance of this was twofold in that it verified the integrity of the setup and proved that a real threat existed. However, the attacks on the cryptographic accelerator failed in all cases to reveal any significant information. Although this is considered a positive result, it does not prove the integrity of the device as it may be possible for an adversary with more resources to successfully attack the board. It does however increase the level of confidence in this particular product and acts as a stepping stone towards conformance of cryptographic standards.

The experimental procedures developed can also be used by designers wishing to test the vulnerability of their own products to these attacks.

# **Contents**

|   | Decl  | ration                                                 | i  |

|---|-------|--------------------------------------------------------|----|

|   |       |                                                        | ii |

|   |       | ationii                                                |    |

|   |       | <i>nct</i>                                             |    |

|   | AOSII | <i>tct</i>                                             | V  |

| 1 | Intro | duction                                                | 1  |

|   | 1.1   | Cryptography                                           | 2  |

|   |       | 1.1.1 Secret Key Cryptography                          | 3  |

|   |       | 1.1.2 Public Key Cryptography                          | 6  |

|   | 1.2   | Security of cryptosystems                              | 9  |

|   |       | 1.2.1 Compromising Emissions                           | 1  |

|   |       | 1.2.2 Tamper Resistance                                | 5  |

|   | 1.3   | FIPS Standards                                         | 6  |

|   | 1.4   | Motivation and thesis aims                             | 8  |

|   | 1.5   | Thesis Organisation                                    | 8  |

| 2 | Dow   | r Analysis 2                                           | U  |

| 4 |       | - TRANSPORT                                            | _  |

|   | 2.1   |                                                        |    |

|   | 2.2   | Overview of Power Attacks                              |    |

|   | 2.3   | Simple Power Analysis (SPA)                            |    |

|   |       | 2.3.1 Hamming Weight Leakage                           | 0  |

|   |       | 2.3.2 Transition Count Leakage                         | 1  |

|   |       | 2.3.3 The Threat of SPA                                | 3  |

|   | 2.4   | Differential Power Analysis (DPA)                      | 3  |

|   |       | 2.4.1 DPA attacks on a symmetric key algorithm - DES 3 | 5  |

|   |       | 2.4.1.1 Single Bit DPA                                 | 6  |

|   |      |         | 2.4.1.2      | Multiple Bit DPA                             |    | 41  |

|---|------|---------|--------------|----------------------------------------------|----|-----|

|   |      |         | 2.4.1.3      | High-Order DPA (HO-DPA)                      |    | 43  |

|   |      |         | 2.4.1.4      | Inferential Power Analysis (IPA)             |    | 44  |

|   | 2.5  | Variati | ons of the D | PA attack for public key systems             |    | 45  |

|   |      | 2.5.1   | Implement    | ation of modular exponentiation              |    | 45  |

|   |      | 2.5.2   | Explanatio   | on of compromising power fluctuations        |    | 47  |

|   |      | 2.5.3   | Points of o  | occurrence of the fluctuations               |    | 49  |

|   |      | 2.5.4   | Attacking    | the exponentiation implementation            |    | 51  |

|   |      |         | 2.5.4.1      | Multiple-Exponent, Single-Data (MESD) attack |    | 52  |

|   | 2.6  | Summ    | ary          |                                              |    | 54  |

| 3 | Elec | tromag  | netic Analy  | sis (EMA)                                    |    | 56  |

|   | 3.1  | Electro | magnetic R   | adiation of Electronic Systems               |    | 57  |

|   |      | 3.1.1   | Basic Con    | cepts                                        |    | 58  |

|   |      | 3.1.2   | Modeling     | radiation from circuits                      |    | 59  |

|   |      | 3.1.3   | Spectral co  | ontent of signals                            |    | 66  |

|   | 3.2  | TEMP    | EST          |                                              |    | 71  |

|   | 3.3  | Literar | y Review .   |                                              |    | 75  |

|   | 3.4  | Summ    | ary          |                                              |    | 81  |

| 4 | Exp  | erimen  | al Setup an  | nd Results                                   |    | 83  |

|   | 4.1  | Initial | Problems .   |                                              |    | 83  |

|   | 4.2  | Initial | Setup        |                                              |    | 85  |

|   | 4.3  | Power   | analysis .   |                                              |    | 96  |

|   |      | 4.3.1   | Initial SPA  | Setup                                        |    | 101 |

|   |      | 4.3.2   | Simulated    | setup                                        |    | 106 |

|   |      | 4.3.3   | Initial DPA  | A attack                                     |    | 113 |

|   |      | 4.3.4   | Emulated     | Setup                                        |    | 116 |

|   |      | 4.3.5   | Final Pow    | er Attack                                    |    | 126 |

|   |      |         | 4.3.5.1      | SPA                                          |    | 127 |

|   |      |         | 4.3.5.2      | DPA                                          |    | 137 |

|   | 4.4  | Electro | omagnetic A  | analysis                                     | ٠. | 146 |

|   |      | 441     | Fmulated     | Setup                                        |    | 146 |

|   |     | 4.4.2    | Basic Setup                                       | 148 |

|---|-----|----------|---------------------------------------------------|-----|

|   |     | 4.4.3    | Alternative Setup                                 | 151 |

|   |     | 4.4.4    | Other strategies attempted                        | 152 |

|   |     | 4.4.5    | Summary                                           | 153 |

| 5 | Cou | nterme   | asures                                            | 154 |

|   | 5.1 | Counte   | ermeasures against Power Analysis                 | 155 |

|   |     | 5.1.1    | Timing Randomisation                              | 156 |

|   |     | 5.1.2    | Random Process Interrupts                         | 157 |

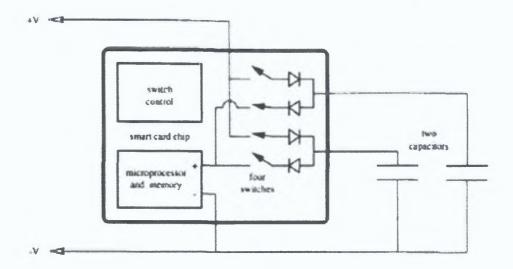

|   |     | 5.1.3    | Internal power supplies                           | 159 |

|   |     | 5.1.4    | Data masking                                      | 160 |

|   |     | 5.1.5    | Tamper Resistance                                 | 161 |

|   |     | 5.1.6    | Fail Counters                                     | 161 |

|   |     | 5.1.7    | Removal of conditional elements                   | 162 |

|   | 5.2 | Count    | ermeasures against EMA attacks                    | 162 |

|   |     | 5.2.1    | Asynchronism                                      | 163 |

|   |     | 5.2.2    | Shielding                                         | 164 |

|   |     | 5.2.3    | Balancing                                         | 166 |

|   |     | 5.2.4    | Red/Black Separation                              | 166 |

|   |     | 5.2.5    | Provably secure Countermeasures                   | 167 |

|   |     | 5.2.6    | Summary                                           | 167 |

| 6 | Con | clusion  | s                                                 | 169 |

|   | Bib | liograp  | hy                                                | 176 |

|   | Ap  | pendix A | A: Data Encryption Standard - DES                 | 185 |

|   | Ap  | pendix l | B: Overview of Number Theory                      | 191 |

|   | Ap  | pendix ( | C: RSA                                            | 197 |

|   | Ap  | pendix l | D: Montgomery's method for modular exponentiation | 200 |

|   | Ind | lex      |                                                   | 210 |

# **List of Tables**

| 2.1 | The cryptosystem accepts a plaintext input $(pi_j)$ and produces both a power waveform $(wf_{jk})$ and a ciphertext output $(co_j)$ . Sometimes only the ciphertext is available to the attacker                                                                      | 36 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Number of waveforms required in a multiple bit DPA attack to keep the SNR the same as a single bit DPA attack. $N_1$ is the number of waveforms required for a one bit DPA attack                                                                                     | 43 |

| 2.3 | Example of modular exponentiation on the DUT with $e=1011_2$ (all values are modulo $m$ ). The final answer is converted back into the normal domain by performing a Montgomery reduction on it: $b^{11}R \mod m$ $\stackrel{reduction}{\longmapsto} b^{11} \mod m$ . | 48 |

| 3.1 | Equations for the fields produced by an ideal loop and wire structure in both the near and far field. The ratio E/H is known as the wave impedance and is equal to the free space impedance in the far field                                                          | 62 |

| 3.2 | Equations for the fields produced by the more practical model in both the near and far field. For the near field, the equations are dependent on the impedance of the circuit.                                                                                        | 65 |

# **List of Figures**

| 1.1 | Secret key encryption                                                                                                                                                                                                                                                                         | 3  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Public key encryption                                                                                                                                                                                                                                                                         | 7  |

| 1.3 | Classical model of a cryptographic communication system                                                                                                                                                                                                                                       | 10 |

| 1.4 | Updated model of a cryptographic communication system incorporating side channel emissions. $K_S$ may or may not equal $K_D$ depending on the cryptographic scheme used                                                                                                                       | 15 |

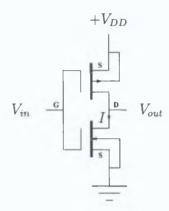

| 2.1 | CMOS Logic Inverter                                                                                                                                                                                                                                                                           | 23 |

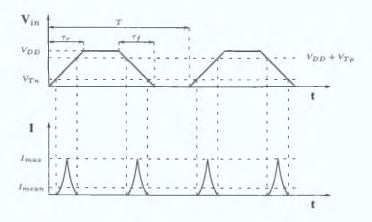

| 2.2 | Current behaviour of inverter without load                                                                                                                                                                                                                                                    | 24 |

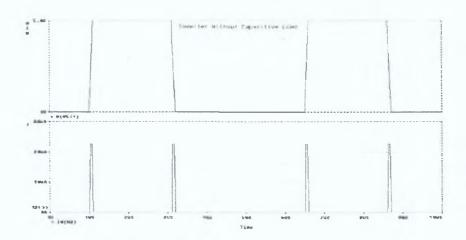

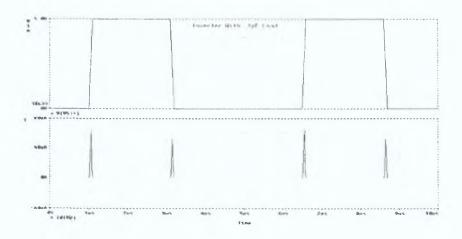

| 2.3 | PSpice analysis of CMOS logic inverter without load                                                                                                                                                                                                                                           | 25 |

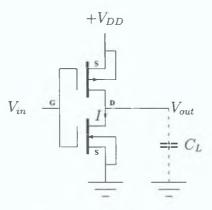

| 2.4 | CMOS Logic Inverter with capacitive load                                                                                                                                                                                                                                                      | 25 |

| 2.5 | PSpice analysis of CMOS logic inverter with .1pF load                                                                                                                                                                                                                                         | 27 |

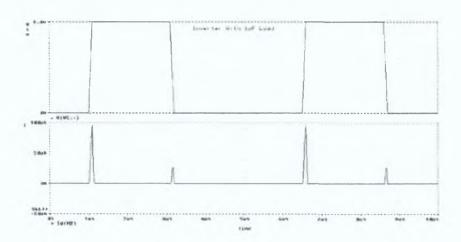

| 2.6 | PSpice analysis of CMOS logic inverter with 1pF load                                                                                                                                                                                                                                          | 28 |

| 2.7 | Two possible versions of the "right to left, square and multiply" algorithm. The function <code>exp_always_mul()</code> is more like the one implemented by the DUT and is more resistant to DPA attacks. Both versions use Montgomery's method for modular reduction to increase efficiency. | 47 |

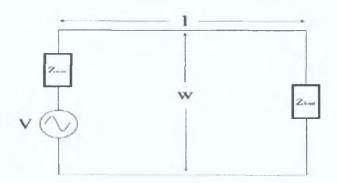

| 3.1 | More practical model of a radiating circuit. The total impedance of the circuit is $Z_{total} = Z_{wire} + Z_{load}$ where $Z_{wire}$ is the impedance of the wire and $Z_{load}$ is the total impedance of any loads driven by the voltage                                                   | 64 |

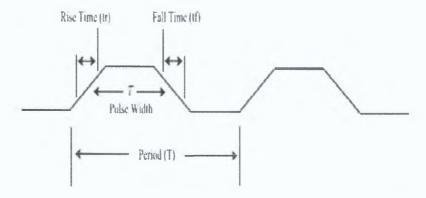

| 3.2 | Trapezoidal waveform with finite rise $(t_r)$ and fall $(t_f)$ times, pulse width $\tau$ and period $T$ . The duty cycle is $d = \tau/T$                                                                                                                                                      | 66 |

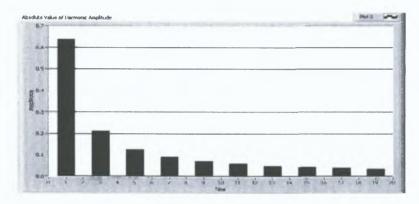

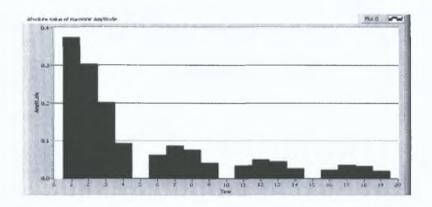

| 3.3 | First 20 harmonics present in a square wave with 2ns rise time and 50% duty cycle. The fundamental frequency is .64 times the peak amplitude of the current.                                                                                                                                  | 67 |

| 3.4 | First 20 harmonics present in a square wave with 2ns rise time and 80% duty cycle. The fundamental frequency is now only .37 times the peak amplitude of the current and even harmonics are present. Every multiple of the 5th harmonic is zero however.                                      | 68 |

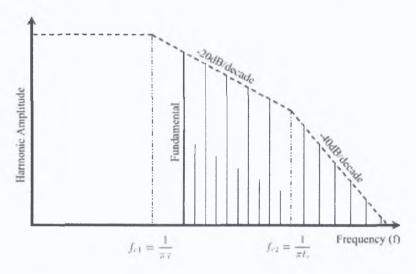

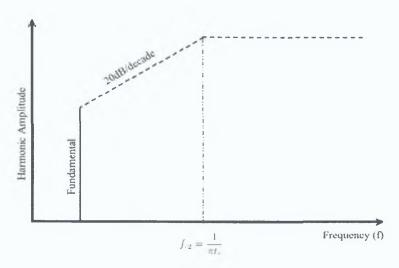

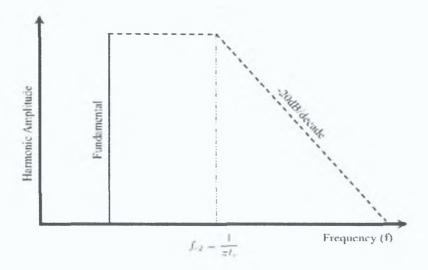

| 3.5  | Envelope of the spectrum of the trapezoidal wave shown in figure 3.2                                                                                                                                                                                                                                                           | 69 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.6  | Differential mode radiated signal                                                                                                                                                                                                                                                                                              | 70 |

| 3.7  | Common mode radiated signal                                                                                                                                                                                                                                                                                                    | 71 |

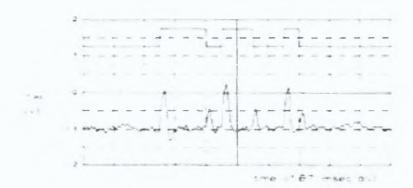

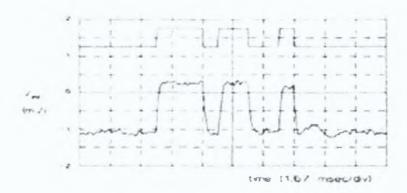

| 3.8  | Graph presented by Smulders that compares the original data on an RS-232 cable with the intercepted data. All that was used was a simple pocket radio tuned to 16MHz and placed 7m from the source. At this frequency the receiver uses an AM detector which results in loss of the signs of the transitions                   | 78 |

| 3.9  | As with figure 3.8 a radio receiver placed at 7m from the source was used. This time however it was tuned to 98MHz and FM demodulation was used. The full signal is present as can be seen.                                                                                                                                    | 78 |

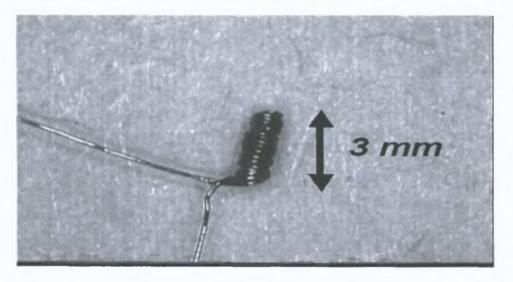

| 3.10 | Coil used by Gandolfi et al. to carry out EMA attacks on a number of smartcards.                                                                                                                                                                                                                                               | 80 |

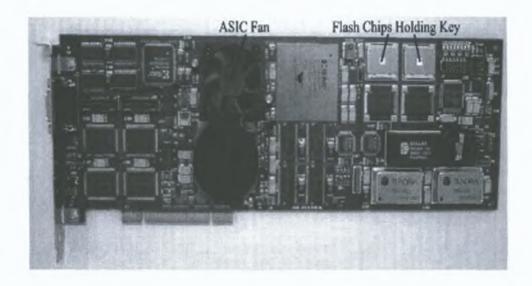

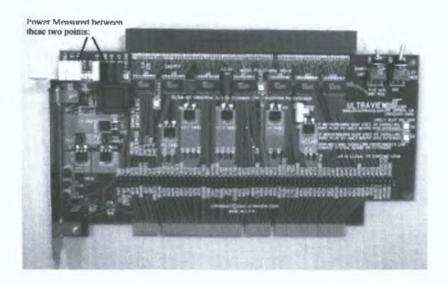

| 4.1  | Device Under Test (DUT) - This is a prototype Encryption Board but is similar in operation to the marketed versions.                                                                                                                                                                                                           | 86 |

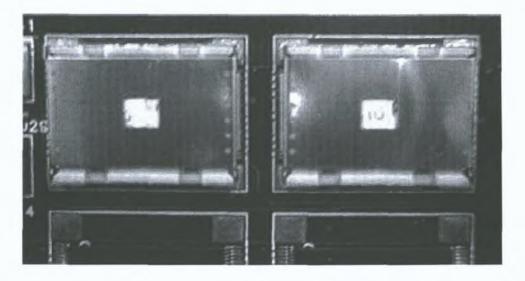

| 4.2  | The slots on the DUT where the flash chips are seated                                                                                                                                                                                                                                                                          | 86 |

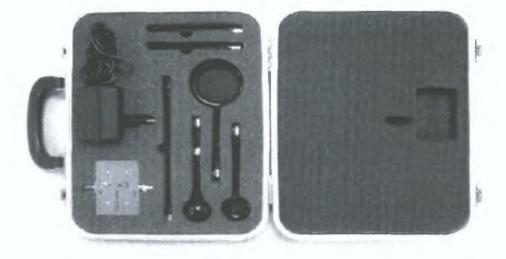

| 4.3  | The EMC kit used to capture and amplify the radiated emissions emanating from the DUT.                                                                                                                                                                                                                                         | 88 |

| 4.4  | Five antennas lined side by side for comparison. The three loops pick up magnetic fields while blocking electric fields, while the ball and the monopole pick up electric fields while blocking magnetic fields. The different sizes allow for more (smaller) or less (larger) precise localisation of the offending emission. | 89 |

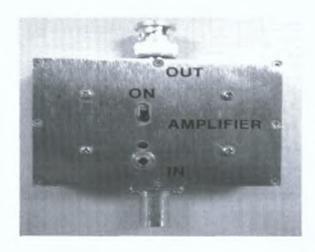

| 4.5  | 20dB shielded amplifier designed for EMC measurements                                                                                                                                                                                                                                                                          | 90 |

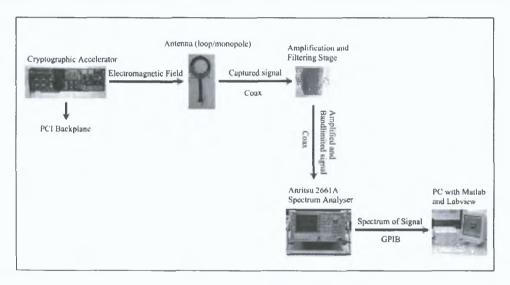

| 4.6  | The initial experimental setup. The antenna was used to pick the magnetic (loop) or electric (monopole/ball probe) field energy surrounding the board. This was then amplified and passed into the spectrum analyser. The analysers measurements were then sent over GPIB to a PC for analysis with MATLAB.                    | 92 |

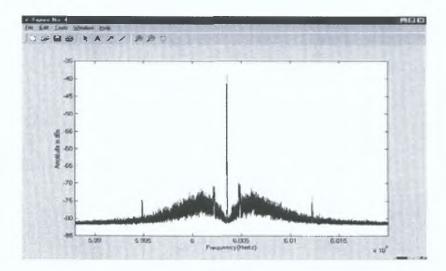

| 4.7  | This is the fundamental frequency of the 60MHz clock. There appears to be sidebands on either side of it which may have contained information                                                                                                                                                                                  | 94 |

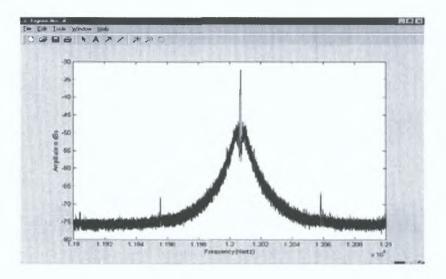

| 4.8  | The second harmonic of the 60MHz clock. This is actually larger than the third harmonic which suggested that the clock did not have a 50% duty cycle                                                                                                                                                                           | 95 |

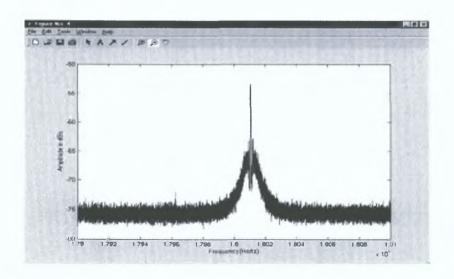

| 4.9  | The third harmonic of the 60MHz clock                                                                                                                                                                                                                                                                                          | 95 |

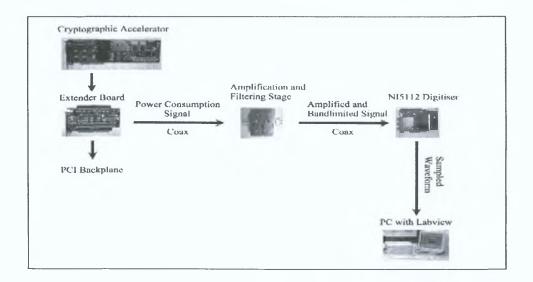

| 4.10 | Extender Board used to measure the power consumption. The DUT sits on top of this. The third slot in the top left hand corner allows observation of the 3.3V power consumption (which is of concern here) with respect to ground (the slot two to the right of it).                                                            | 97 |

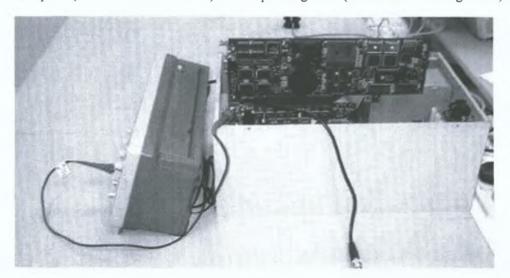

| 4.11 | Side view of the PCI backplane holding the extender board and the cryptographic module                                                                                                                                                                                                                                         | 97 |

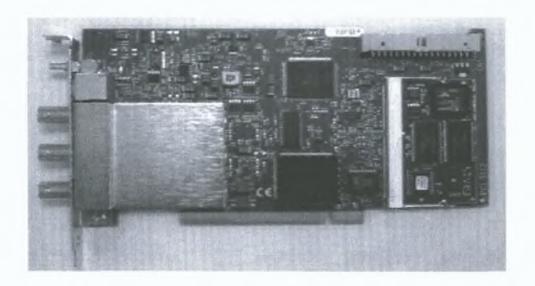

| 4.12 | Close up of NI5112 digitiser. The three BNC connectors are channels 0, 1 and an external trigger. There is also and SMA connector.                                                                                                                                                                                                   | 101 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

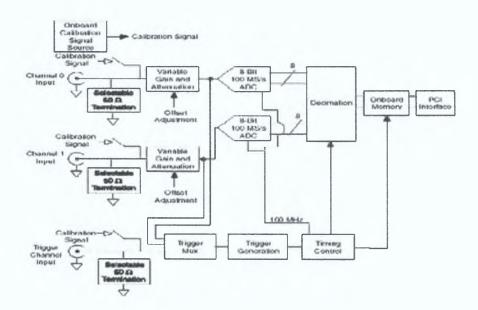

| 4.13 | Block diagram of inner workings of the NI5112. As can be seen there are two input channels as well as an external trigger channel. The input impedances are switchable between $50\Omega$ and $1M\Omega$ .                                                                                                                           | 102 |

| 4.14 | All three PCI boards placed side by side for comparison. From left to right: DUT, Extender Board and NI5112 digitiser.                                                                                                                                                                                                               | 102 |

| 4.15 | Block Diagram of DPA setup                                                                                                                                                                                                                                                                                                           | 103 |

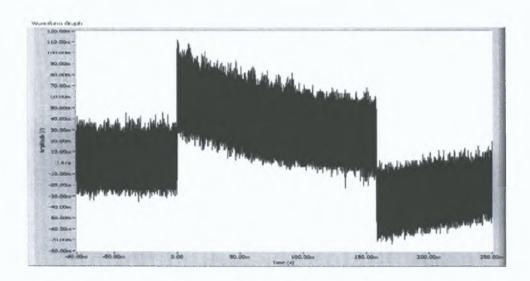

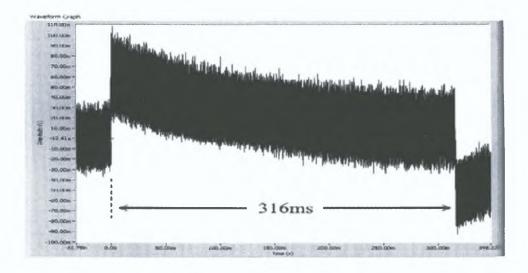

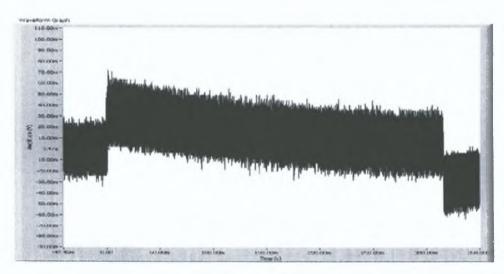

| 4.16 | This is a 158ms pulse in which one complete encryption is performed. The amount of memory needed to capture this entire waveform at 100MSs <sup>-1</sup> would have been impractical, so only sections of it were sampled for the attack                                                                                             | 105 |

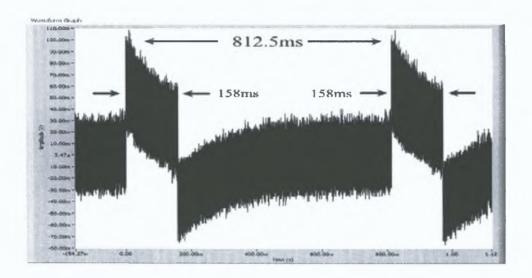

| 4.17 | Two encryption pulses showing the time difference between encryptions                                                                                                                                                                                                                                                                | 106 |

| 4.18 | The Front Panel of the main vi for simulating the power waveforms produced by the DUT.                                                                                                                                                                                                                                               | 108 |

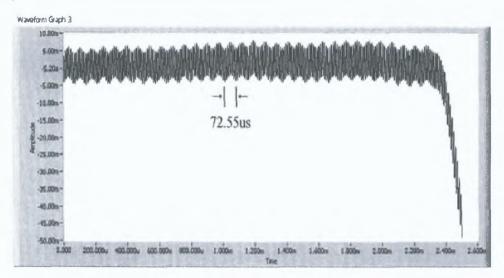

| 4.19 | This is one part of the Block Diagram of Labview program for producing the simulated power waveform.                                                                                                                                                                                                                                 | 108 |

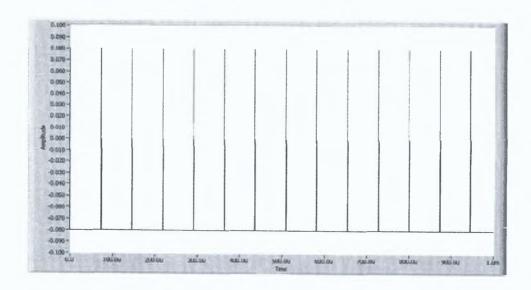

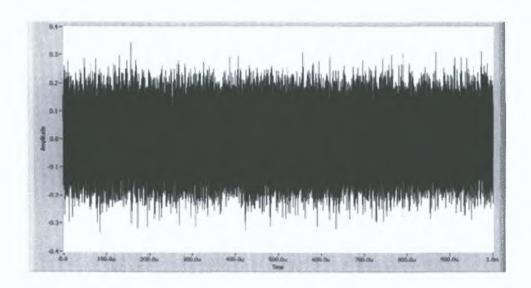

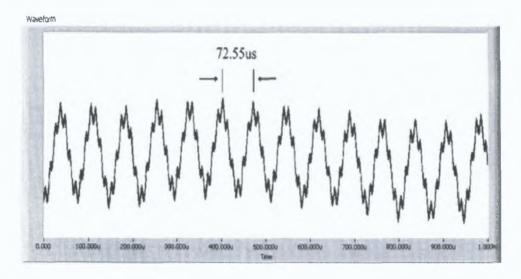

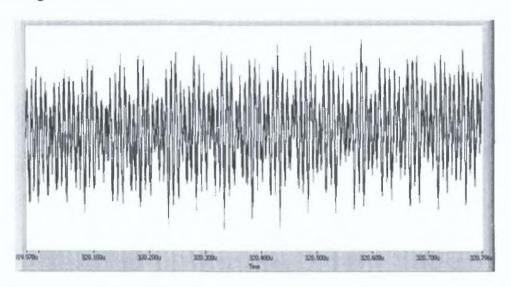

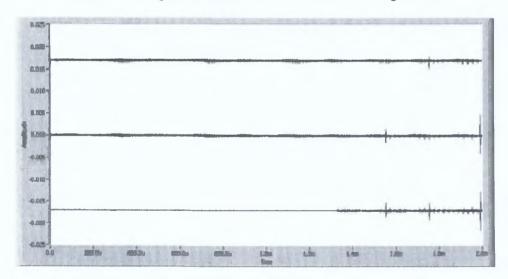

| 4.20 | The signal here is the simulated version of what might have been produced (without any noise) using a key with all ones. The spikes had an amplitude of $160 \text{mV}$ and were offset by $-80 \text{mV}$ . They lasted for only $16 \text{ns}$ which was a mark-space ratio of only .01 percent (as the period was $72.55 \mu s$ ) | 110 |

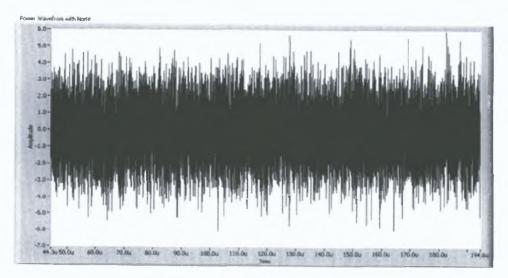

| 4.21 | This graph shows the one in figure 4.20 with an excessive amount of noise added. This signal can be seen to exceed $\pm 5V$ at some points and completely masks the power signal sought after                                                                                                                                        | 110 |

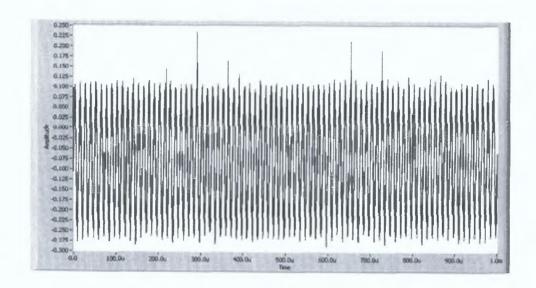

| 4.22 | This graph shows the quality of the signal produced using the "All Ones" simulated data after 1000 averages. The noise has been reduced significantly however it still completely masks the power signal sought after                                                                                                                | 111 |

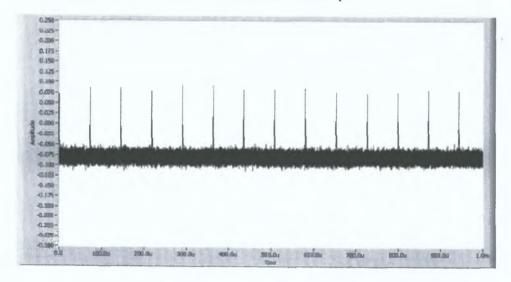

| 4.23 | This graph shows the quality of the signal produced using the "All Ones" simulated data after 15000 averages. The random noise has been reduced to insignificant levels however a large 80kHz wave can be seen that masks the bias spikes.                                                                                           | 112 |

| 4.24 | This is the differential trace produced by subtracting the average of the waveform produced by the key with all zeros from that with all ones. The key is clearly visible thus verifying the integrity of the Labview program                                                                                                        | 112 |

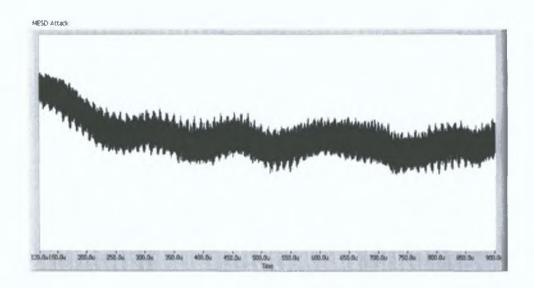

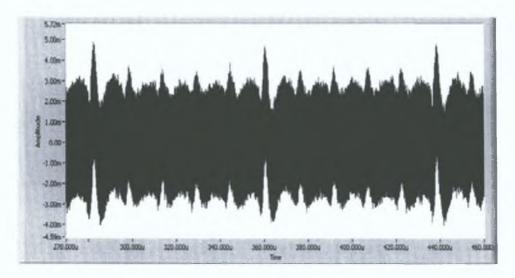

| 4.25 | Average of the waveforms produced by the exponent with all ones. There is a signal of approximately 90kHz effecting the reading. Each exponent operation can be barely distinguished as the envelope of the 90kHz signal.                                                                                                            | 114 |

|      |                                                                                                                                                                                                                                                                                                                                      |     |

.

| 4.26 | Close up of the trace obtained using the all ones key. This particular waveform was collected at the center of the 158ms pulse and was passed through a Butter-                                                                                                                                                                                              |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | worth high pass filter with a lower cut-off of 200kHz. Each exponent operation is clearly visible however its value cannot be identified                                                                                                                                                                                                                     | 115 |

| 4.27 | Pin diagram for the PIC16F877 microcontroller used to emulate the operations of the DUT. The chip can accept and number of inputs as well as produce a number of outputs (as implied by the two way arrows) which can be used to control the value of the data being operated upon (using a switch) as well as displaying the results (using an LCD display) | 117 |

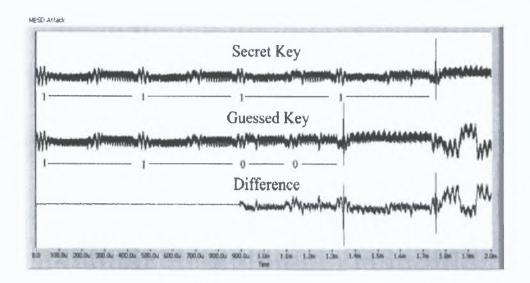

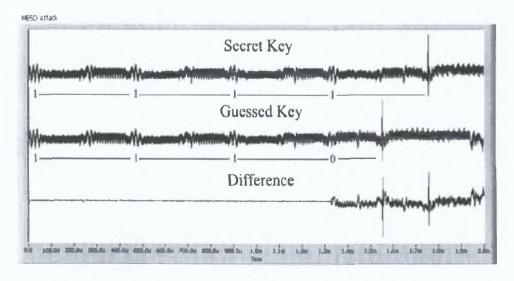

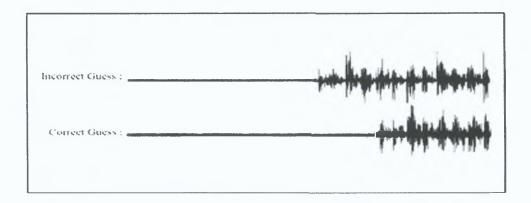

| 4.28 | The difference between the average power of the secret key and that of a key with an incorrectly guessed bit. The values up to the attacked bit had been successfully retrieved and the difference in power fluctuations tend to zero up to this point.                                                                                                      | 121 |

| 4.29 | The difference between the average power of the secret key and that of a key with a correctly guessed bit. It can be seen quite clearly from the differential trace that the waveforms are now the same up to the fourth bit                                                                                                                                 | 121 |

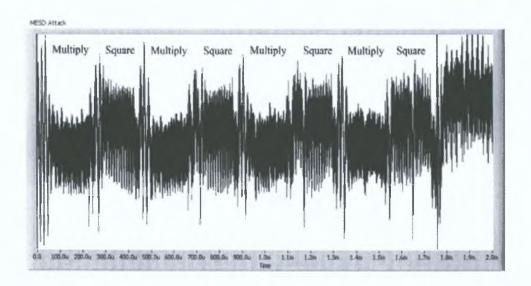

| 4.30 | Results of the MESD attack reported by Messerges et al It can be seen that these waveforms are very similar to those shown in figures 4.28 and 4.29                                                                                                                                                                                                          | 122 |

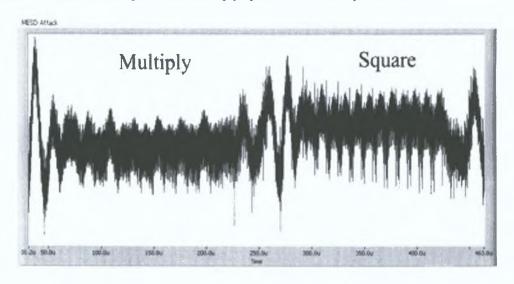

| 4.31 | A magnified view of the power waveform obtained with the exponent 1111. The differences between a square and a multiply operations are clearly visible                                                                                                                                                                                                       | 123 |

| 4.32 | The power waveforms representing the square and the multiply operation. The two sections are clearly distinguishable. The multiply operation took slightly longer to complete than the square operation                                                                                                                                                      | 123 |

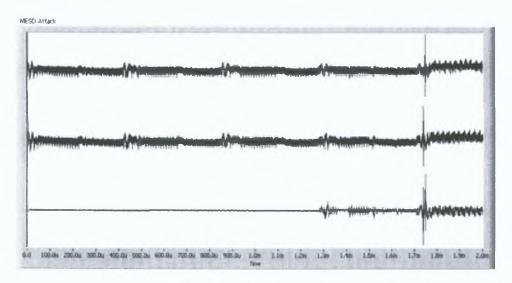

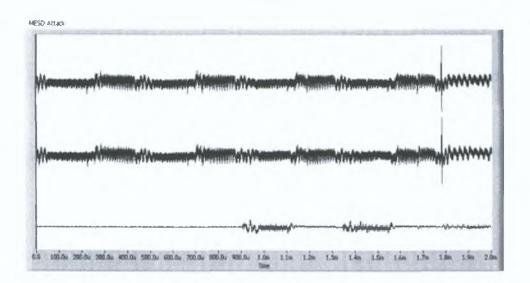

| 4.33 | The power waveforms and differential trace when the multiplication operation is performed in every round. There is still a slight time difference and the difference waveform is still correlated to the key.                                                                                                                                                | 124 |

| 4.34 | PIC run with two if statements. One for a 1 and the other for a 0. The difference is still distinguishable                                                                                                                                                                                                                                                   | 125 |

| 4.35 | These are the power waveforms from a register update only but with an if statement for both the zero case and one case.                                                                                                                                                                                                                                      | 126 |

| 4.36 | This is the pulse representing one complete encryption. As the clock had been reduced to 30MHz, the operations took twice as long to complete and the pulse width was now twice that of figure 4.16                                                                                                                                                          | 127 |

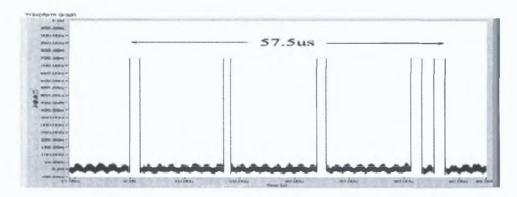

| 4.37 | Trigger signal used to allow a steady capture of the power waveform. The encryption began at the beginning of the first pulse. It was necessary to set the "holdoff" option on the digitiser to 1ms so as not to accidently trigger off the other four pulses.                                                                                               | 128 |

|      |                                                                                                                                                                                                                                                                                                                                                              |     |

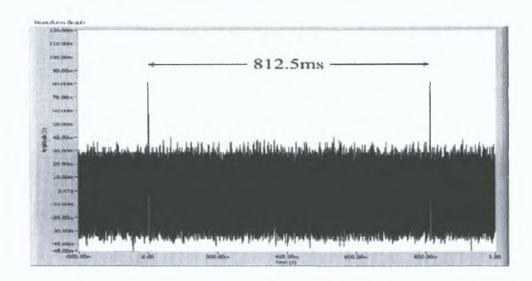

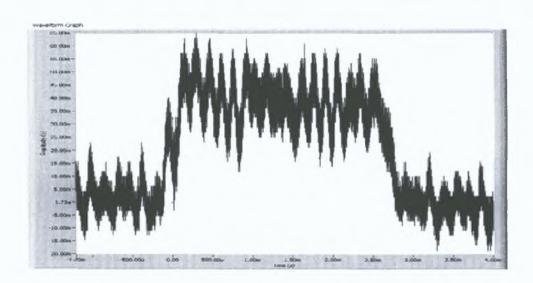

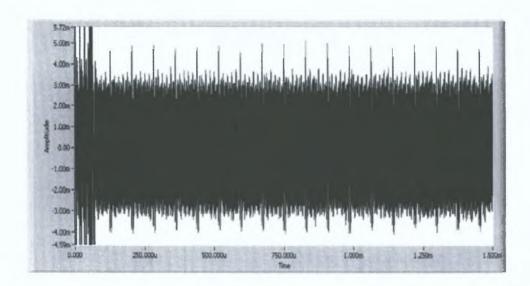

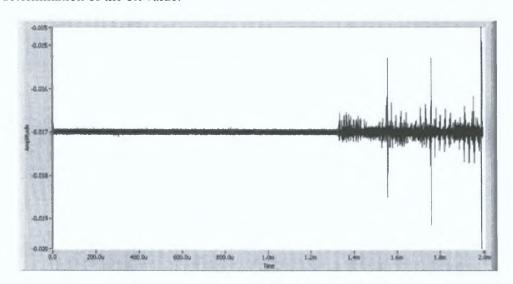

| 4.38 | This graph shows two complete operations. Each operation lasts about 2.5ms compared with the 812.5ms between operations. The pulses representing the encryptions are at a level of just over 80mV due to the excessive noise                                                                                                                                                                                   | 132        |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

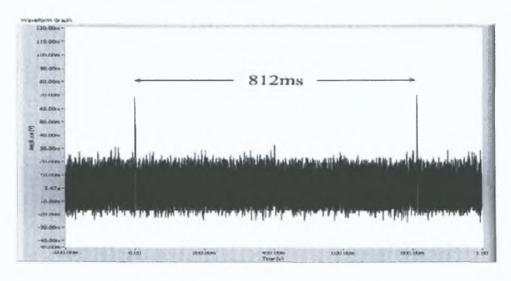

| 4.39 | This graph again shows two complete operations however this time the bandwidth has been limited to 20MHz. The noise dropped quite substantially and the pulse appeared to be only 70mV in amplitude                                                                                                                                                                                                            | 132        |

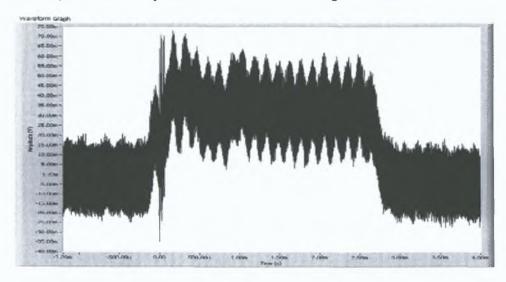

| 4.40 | One complete encryption. This was sampled at 100MSs <sup>-1</sup> and was limited to 20MHz bandwidth to prevent aliasing. Each of the 16 exponent operations could be seen with some clarity however it was possible to mistake them as background noise                                                                                                                                                       | 133        |

| 4.41 | This particular encryption was sampled at an effective rate of 2GSs <sup>-1</sup> using RIS. The 16 exponent operations are a lot more distinguishable in this case                                                                                                                                                                                                                                            | 133        |

| 4.42 | Waveform collected for a modulus of all ones and a base one less than the modulus. The key is some odd value.                                                                                                                                                                                                                                                                                                  | 134        |

| 4.43 | The two LSBs of the base are changed to 1001 1001 so the equation 4.3 doesn't hold and the result appears random.                                                                                                                                                                                                                                                                                              | 135        |

| 4.44 | Base and modulus set to alternating ones and zeros and the result is 1. This waveform was the largest one obtained.                                                                                                                                                                                                                                                                                            | 136        |

| 4.45 | Base and modulus set to alternating ones and zeros and the result is equal to the base. The waveform has reduced in size                                                                                                                                                                                                                                                                                       | 136        |

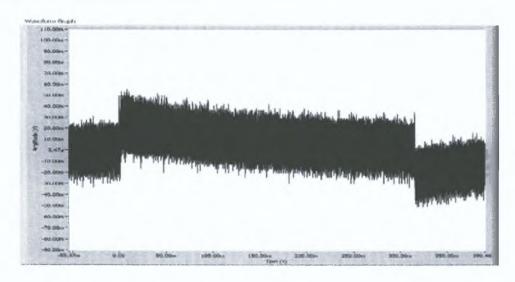

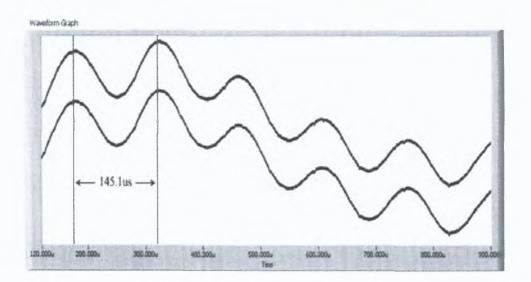

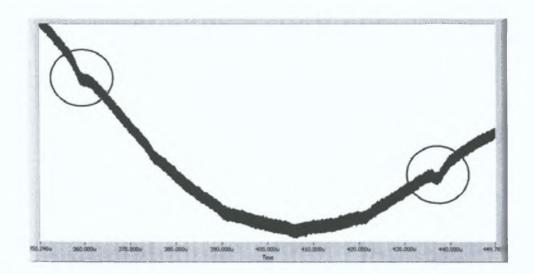

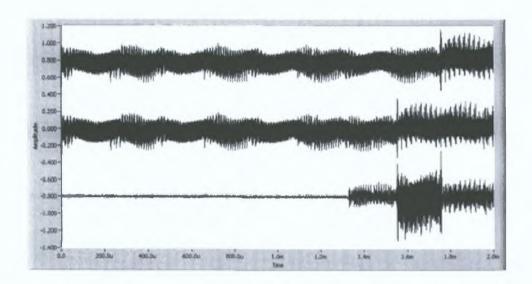

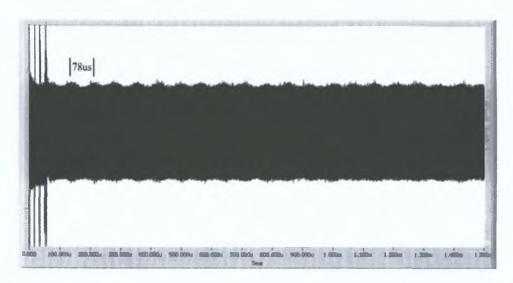

| 4.46 | Waveforms obtained using the key consisting of all ones (top) and key with half ones half zeros (bottom). These were amplified using the EMC amplifier and the low frequency components are present acting as a guide to the occurrences of each operation. It can be seen that time difference between the crest of each pulse is exactly $145.10\mu s$ which is the time it took for each bit to be operated | 100        |

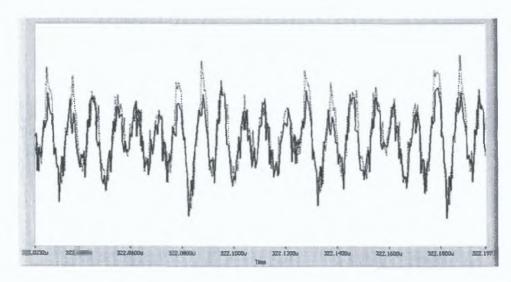

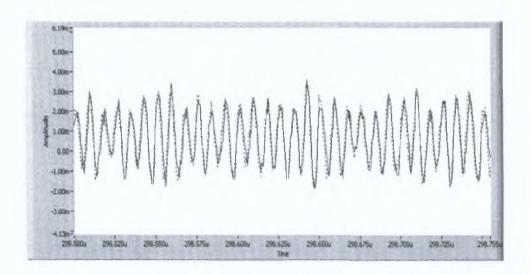

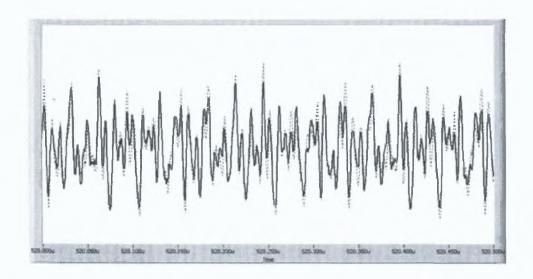

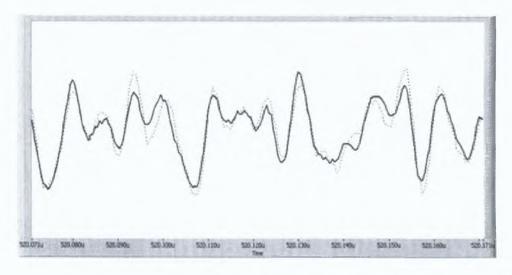

| 4.47 | This is a close up of the waveform shown in figure 4.46 before the keys begin to differ. The dotted line represents the waveform produced with the all ones key and the continuous line is that produced by the key with half one, half zeros. As would be expected the waveforms are almost identical                                                                                                         | 139<br>139 |

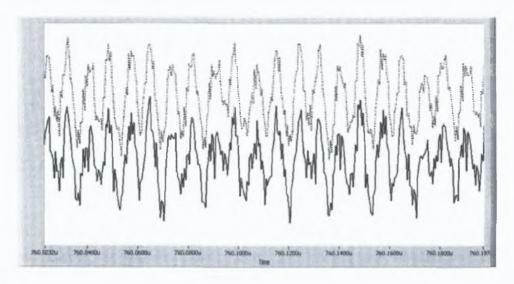

| 4.48 | This is a close up of the waveform shown in figure 4.46 after the keys have differed. It was expected that the two waveforms be quite different from each other due to algorithmic noise etc. however this appeared not to be the case. The main difference is a slight offset of the two waves however it is doubtful that this reveals any information.                                                      | 140        |

| 4.49 | 20MHz beating, probably caused by the fact that the RIS was run at 100 times this value                                                                                                                                                                                                                                                                                                                        | 141        |

| 4.50 | Differential trace of the two waveforms shown in figure 4.46. A difference should occur at about $580.40 \mu s$ however no difference is noticed                                                                                                                                                                                                                                                               | 142        |

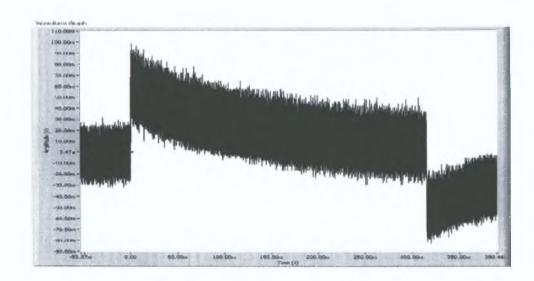

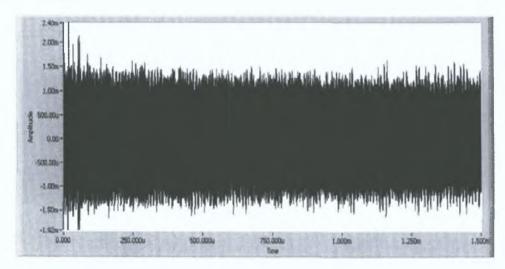

| 4.51 | Power waveform collected over 8,000 averages. This particular waveform was passed through the two Picosecond 5840 amplifiers which filtered out the lower frequency components seen in figure 4.46                                                             | 143 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.52 | Magnified view of figure 4.46 showing anomalous $78 \mu s$ spikes                                                                                                                                                                                              | 144 |

| 4.53 | Magnified view of figure of three spikes. There is certainly a regularity amongst the fluctuation however they occur for both values of the exponent and appear not to be related to the exponent                                                              | 144 |

| 4.54 | Similar view to that of figure 4.48. The waveforms for each exponent are identical again.                                                                                                                                                                      | 145 |

| 4.55 | Differential trace revealing no information                                                                                                                                                                                                                    | 145 |

| 4.56 | Waveform captured using the medium sized loop antenna (see figure 4.4) placed in a horizontal position over center of PIC. A similar result was produced for the monopole antenna. The value of the bit guessed at was correct as was the case in figure 4.29. | 147 |

| 4.57 | Waveform captured using medium sized loop antenna at top of PIC (near pin 1). The amplitude has dropped dramatically from that of figure 4.56 however it is still possible to determine the value of the exponent                                              | 147 |

| 4.58 | Close up of the differential trace of figure 4.57. Even placed a distance away from the source, the MESD attack was still successful                                                                                                                           | 148 |

| 4.59 | This is the waveform that was collected using the exponent consisting of all ones. The $78\mu s$ spikes can be seen as "humps" on the waveform. The waveform for the half ones, half zeros exponent is almost identical                                        | 149 |

| 4.60 | A close up of the graph of figure 4.59 is shown here. Again it can be seen that the two waveforms follow each other very closely.                                                                                                                              | 150 |

| 4.61 | An even closer view of figure 4.59 verifying the similarity between the fluctuations. This was the case throughout the entire waveform.                                                                                                                        | 150 |

| 4.62 | A picture of the general setup for the DPA attacks outlined in this chapter                                                                                                                                                                                    | 152 |

| 5.1  | Detached Power supply proposed by Shamir                                                                                                                                                                                                                       | 160 |

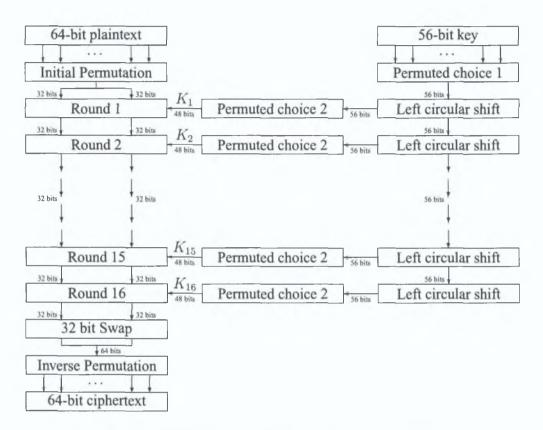

| 6.1  | Flow Diagram of DES algorithm for encrypting data                                                                                                                                                                                                              | 187 |

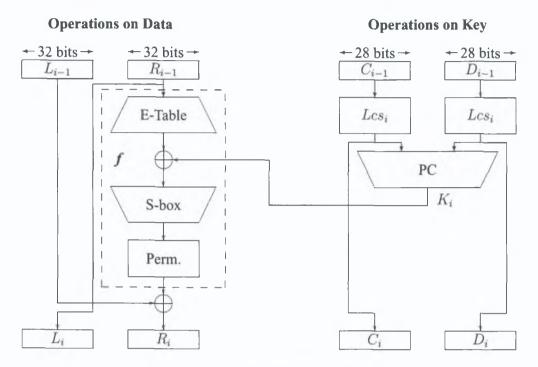

| 6.2  | Details of a single DES round                                                                                                                                                                                                                                  | 188 |

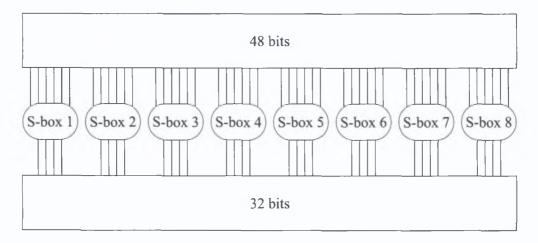

| 6.3  | Diagram of S-box substitution.                                                                                                                                                                                                                                 | 190 |

| 6.4  | This algorithm computes the value of $XR^{-1} \mod m$ without having to divide by $m.\ldots\ldots\ldots\ldots\ldots\ldots$                                                                                                                                     | 203 |

| 6.5  | This algorithm computes the value of $PQR^{-1} \mod m$ without having to divide                                                                                                                                                                                | 207 |

|      | by <i>m</i>                                                                                                                                                                                                                                                    | 206 |

# **Chapter 1**

### Introduction

The idea of communications interception is not new. For as long as human beings have been communicating, some unintended recipient has been listening. With the advent of technology, communication methods have improved dramatically, and ways have been devised to make it increasingly difficult for unauthorised parties to intercept and analyse the information communicated. Unfortunately, using the same technology, the methods of interception have also greatly improved.

Secure communications can be achieved to an extent using a technique known as *Cryptography* - the art of secret writing. Cryptography has been around for centuries in one form or another and has received new life with the extraordinary computing power available in todays microprocessors. During the two world wars, cryptography was a highly classified subject and little was known about it in the public domain. With the advancement of technology however, public domain research flourished, and the first public algorithms were developed. Not surprisingly, with these algorithms came reported attacks on them.

Until recently most of the attacks were aimed at the algorithm itself. Mathematical weakness's were exploited to allow the secret information to be revealed. However as the theoretical integrity of the algorithms evolved, direct attacks became much less effective. Attackers looked for alternative ways to compromise the security of these algorithms and inevitably found them - the so called *side channels*.

A "side channel" is any information bearing emission<sup>1</sup> that results from the physical implementation of a cryptographic algorithm. Due to the fact that these emissions are information bearing, they are referred to as *compromising emissions*.

This thesis aims to test the vulnerability of a certain high speed *cryptographic device* to some of these compromising emissions (specifically the first and last attacks outlined in section 4.11 of the Federal Information Processing Standard (FIPS) 140-2, "Security Requirements For Cryptographic Modules" [1]). A cryptographic device (also known as a cryptoprocessor) is any electronic or mechanical<sup>2</sup> device that is used to keep information secure. Published research would suggest that side channels have been used primarily to attack smart cards and other low power, minimal circuitry devices. The high speed cryptographic device tested here (herein referred to as the Device Under Test or DUT) is far more complicated than any smart card. It has it's own purpose built Application Specific Integrated Circuit (ASIC), and also contains at least one countermeasure to these attacks. It will be seen that the attacks were far more difficult to implement in this case.

#### 1.1 Cryptography

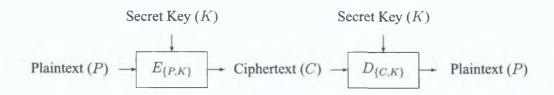

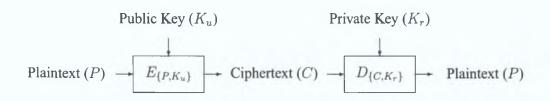

The idea of cryptography is to convert information to a form that will be unintelligible to an unintended recipient. It accomplishes this using a cryptographic algorithm known as a *cipher*, and an object known as a *cryptographic key*. Figures 1.1 and 1.2 show examples of the two classes of cryptographic systems in use today. The information to be converted is known as *plaintext* and the converted information is known as *ciphertext*. The process of converting plaintext to ciphertext is known as *encryption* and the process of converting back from ciphertext to plaintext is known as *decryption*.

<sup>&</sup>lt;sup>1</sup>The US military refers to it as an "emanation" however the two words will be used interchangeably throughout this thesis.

<sup>&</sup>lt;sup>2</sup>Today they are built for practical applications using electronics only, however during World War II, they were entirely mechanical.

The cryptographic key may (figure 1.1) or may not (figure 1.2) be the same for both encryption and decryption depending on the type of algorithm used. A dedicated circuit board used to perform encryption and decryption is known as a *cryptoprocessor* which can be part of an overall system known as a *cryptosystem*<sup>3</sup>.

There are two main types of cryptography in use today - *symmetric* or *secret key* cryptography and *asymmetric* or *public key* cryptography. Symmetric key cryptography is the oldest type whereas asymmetric cryptography is only being used publicly since the late 1970's<sup>4</sup>. Asymmetric cryptography was a major milestone in the search for a perfect encryption scheme.

#### 1.1.1 Secret Key Cryptography

As mentioned, secret key cryptography is by far the oldest of the two types and goes back to Egyptian times. It involves the use of only one key which is used for both encryption and decryption (hence the name symmetric key cryptography). Figure 1.1 depicts this idea. It is necessary for security purposes that the secret key never be revealed.

Figure 1.1: Secret key encryption.

To accomplish encryption, most secret key algorithms use two main techniques known

<sup>&</sup>lt;sup>3</sup>Sometimes the two terms are used interchangeably.

<sup>&</sup>lt;sup>4</sup>It is claimed by some that government agencies knew about asymmetric cryptography before this.

as *substitution* and *permutation*. Substitution is simply a mapping of one value to another whereas permutation is a reordering of the bit positions for each of the inputs. These techniques are used a number of times in iterations called *rounds*. Generally, the more rounds there are, the more secure the algorithm. A non-linearity is also introduced into the encryption so that decryption will be computationally infeasible<sup>5</sup> without the secret key. This is achieved with the use of *S-boxes* which are basically non-linear substitution tables where either the output is smaller than the input or vice versa. See [2] for more details.

For the past 25 years, the main standard for encrypting data was a symmetric algorithm known as the *Data Encryption Standard* (DES)<sup>6</sup>. DES is a 64 bit *block cipher* which means that it encrypts data 64 bits at a time. This is contrasted to a *stream cipher* in which only one bit at a time (or sometimes small groups of bits such as a byte) is encrypted.

DES was the result of a research project set up by International Business Machines (IBM) corporation in the late 1960's which resulted in a cipher known as LUCIFER. In the early 1970's it was decided to commercialise LUCIFER and a number of significant changes were introduced. IBM was not the only one involved in these changes as they sought technical advice from the National Security Agency (NSA) [3] (other outside consultants were involved but it is likely that the NSA were the major contributors from a technical point of view). The altered version of LUCIFER was put forward as a proposal for the new national encryption standard requested by the National Bureau of Standards (NBS)<sup>7</sup>. It was finally adopted in 1977 as the Data Encryption Standard DES.

Some of the changes made to LUCIFER have been the subject of much controversy

<sup>&</sup>lt;sup>5</sup>This means that it costs more to implement the attack than the information is worth.

<sup>&</sup>lt;sup>6</sup>This is now being replaced by a new standard known as the Advanced Encryption Standard (AES).

<sup>&</sup>lt;sup>7</sup>Now known as the National Institute of Standards and Technology (NIST).

even to the present day. The most notable of these was the key size. LUCIFER used a key size of 128 bits however this was reduced to 56 bits for DES. Even though DES actually accepts a 64 bit key as input, the remaining eight bits are used for parity checking and have no effect on DES's security. Outsiders were convinced that the 56 bit key was an easy target for a brute force<sup>8</sup> attack due to its extremely small size. The need for the parity checking scheme was also questioned without satisfying answers.

Another controversial issue was that the S-boxes used were designed under classified conditions and no reasons for their particular design were ever given. This led people to assume that the NSA had introduced a "trapdoor" through which they could decrypt any data encrypted by DES even without knowledge of the key. One startling discovery was that the S-boxes appeared to be secure against an attack known as *Differential Cryptanalysis* [4] which was only publicly discovered by Biham and Shamir in 1990. This suggests that the NSA were aware of this attack in 1977; 13 years earlier! A detailed description of DES is given in appendix A and is required for an understanding of the next chapter.

DES of course isn't the only symmetric cipher. There are many others, each with varying levels of complexity. Such ciphers include: IDEA, RC4, RC5, RC6 and the new Advanced Encryption Standard (AES) known as Rijndael. These ciphers are of no concern in this thesis as the DUT wasn't running them. However AES has been under intense scrutiny with regard to side channel attacks because it must be able to withstand them if it is to be the next cryptographic standard. For more information on the first three of these ciphers, the interested reader is referred to [2] and for Rijndael see [5].

One of the main problems with secret key cryptography is key distribution. For this form of cryptography to work, both parties must have a copy of the secret key. This

<sup>&</sup>lt;sup>8</sup>See section 1.2

would have to be communicated over some secure channel which, unfortunately, is not that easy to achieve. As will be seen in the next section however, public key cryptography provides a solution to this.

#### 1.1.2 Public Key Cryptography

Public key cryptography was considered a major achievement in the field, as it offered an excellent solution for the old time problem of key distribution. It was invented by Whitfield Diffie and Martin Hellman in 1976<sup>9</sup> and was such a milestone, that the term *modern cryptography* is often used to refer to cryptography after this date.

Diffie and Hellman produced the first public key algorithm [6]. Unfortunately, it was only useful for key distribution. An algorithm was needed that would allow both encryption and digital signatures. In 1977, Ron Rivest, Adi Shamir and Leonard Adleman fulfilled this requirement with the algorithm known as RSA (an anagram of the first letters from each of the inventors surnames), the first fully fledged public key algorithm. It was, and is still is, the most popular public key algorithm available.

Public key cryptography uses a different technique than secret key cryptography. Instead of using only one cryptographic key, it uses two keys - a private key¹¹¹ and a public key. The private key is kept private and the public key is kept in a public database where anyone can access it. To accomplish this, a variation of a function known as a one-way function is used. This is a function that is easy to calculate one way, but extremely difficult (ideally impossible) to reverse. Encryption using such a function would be easy, but decryption would be impossible. Of course an ideal one-way function is of no use because this would then mean that the intended recipient would be unable to decipher the message. Instead, the variation used, allows decryption only if a

<sup>&</sup>lt;sup>9</sup>It was also independently invented by Ralph Merkle [2].

<sup>&</sup>lt;sup>10</sup>The term "private key" is generally used instead of "secret key" to distinguish it from the key used in symmetric key cryptography (of which there is only one). Both the secret key in symmetric cryptography and the private key in asymmetric cryptography must not be revealed to anyone however.

certain parameter is known (i.e. the private key). This is known as a *trapdoor one-way* function. See [2,7,8] for more details.

A secure communication or transaction takes place by encrypting intended data with the public key and then transferring the information to the intended recipient. The recipient will then decrypt the data with the private key that is paired with public key. This idea is depicted in figure 1.2 where the public key is given the symbol  $K_u$  and the private key  $K_r$ . The keys always come in pairs and are thus referred to as a *key pair*.

Figure 1.2: Public key encryption.

There have been quite a few algorithms proposed to implement the public key scheme. However, due to either insecurities or impracticalities, most have been rejected. Of the ones that have been accepted, most are good for either encryption or digital signatures, but not both. Only three are considered to work well for both methods and only one of these three has been widely excepted. The three are RSA, ElGamal and Rabin, with RSA being the most widely accepted. RSA has not yet been proven to be secure, however it gets it's wide acceptance from the fact that nobody has succeeded in breaking it. Details on all three ciphers can be found in [2] and an overview of RSA is given in appendix C.

A lot of public key algorithms (including RSA) use concepts from an area of mathe-

matics known as *Number Theory*<sup>11</sup>. One of the main ideas in number theory is *modular* arithmetic and specifically, *modular exponentiation*. Modular exponentiation is used by many public key algorithms to perform encryption and decryption. It is similar to ordinary exponentiation except that the result is not the value of the exponentiation itself, but of the remainder when this value is divided by a number called the modulus. Considering RSA specifically, the equation to calculate the ciphertext from the plaintext is

$$C = M^e \bmod n \tag{1.1}$$

where C is the ciphertext, M is the plaintext and the set  $\{e, n\}$  constitute the public key,  $K_u$ .

The original message M can be reconstructed by decryption which is of a similar form,

$$C^d \bmod n = M^{ed} \bmod n = M \bmod n \tag{1.2}$$

where the set  $\{d, n\}$  constitute the private key  $K_r$ , and the other variables are as before. It might appear rather strange that  $M^{ed} \mod n = M \mod n$  however, there are strict rules that govern the choice of e, d and n which must be adhered to in order for this equality to be true (an explanation is given in appendix C where an overview of RSA is given).

The problem with modular exponentiation is that it is computationally intensive and can severely affect the performance of modern e-commerce servers. A solution to the problem is to assign the encryption to a dedicated high speed cryptoprocessor such as the one being reviewed here.

<sup>&</sup>lt;sup>11</sup>An overview of number theory is given in appendix B.

#### 1.2 Security of cryptosystems

The following is taken from [9]:

"A secure coprocessor is a general-purpose computing environment that withstands physical attacks and logical attacks. The device must run the programs that it is supposed to, unaltered. You must be able to (remotely) distinguish between the real device and application, and a clever impersonator. The coprocessor must remain secure even if adversaries carry out destructive analysis of one or more devices . . . You need a device you can trust even though you can't control its environment."

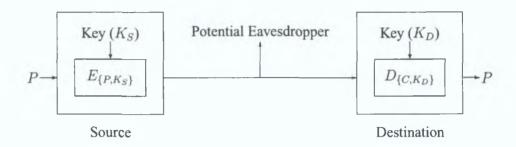

Traditionally, cryptographic systems have been represented only as mathematical models. Figure 1.3 shows an example of one of these models. In this scenario, an encrypted communication takes place by encrypting some plaintext with a particular cipher, and transferring it through and insecure channel to which some intruder may be connected. On receiving this information, the recipient decrypts it in the usual manner. It is assumed in this case that the security of the entire cryptosystem rests with the particular algorithm used, and that the eavesdropper will only have some plaintext-ciphertext pairs to work with 12.

Algorithms in cryptography are designed to keep information secure. An algorithm is considered secure if there is no attack that can reveal the secret information with less than  $2^N$  tries where N is the number of bits in the cryptographic key (in other words, the security of a cryptosystem should depend on the cryptographic key used and not on the algorithm itself).

An attack where every possible key is tried until the correct one is found is known as a Brute force attack. As there are  $2^N$  possible values (known as the key space) for an N

<sup>&</sup>lt;sup>12</sup>A knowledge of the particular algorithm is always assumed. This is known as Kerckhoff's law.

Figure 1.3: Classical model of a cryptographic communication system.

bit number, then generally a brute force attack will take  $2^N$  attempts to find the key<sup>13</sup>. A cryptographic cipher is said to have been *broken* if it is vulnerable to attacks with less effort than a brute force attack (even if the attack is not practical).

There is only one algorithm that has been proven to be completely secure<sup>14</sup> (if used correctly) and is known as the *one time pad*. This is a symmetric cipher where there are as many key bits as plaintext bits. It uses a different key for every encryption and the key set is truly random<sup>15</sup>

Each bit of the plaintext is encrypted with each bit of the key using the exclusive-OR operation  $(\oplus)$ . As the key is truly random, this means that the ciphertext produced will also be truly random and is therefore equally likely to correspond to any plaintext message of the same size as the original. It's security rests on the fact that these random keys are never used more than once. Of course, the person decrypting the message would need to know the keys, and the problem of how best to provide a copy of them is still an issue today. This is the case even with public key cryptography as if this is used to transfer the keys, then the one time pad is only as strong as the public key system used. The one time pad is not a very practical system and is rarely used in real world applications.

<sup>&</sup>lt;sup>13</sup>On average however, it will only take half this or  $2^{N-1}$  tries.

<sup>&</sup>lt;sup>14</sup>Even against brute force attacks.

<sup>&</sup>lt;sup>15</sup>This basically means that there is no way of knowing one key from any combination of the others.

Despite the fact that all practical ciphers are theoretically vulnerable to a brute force attack, it is generally impossible to successfully implement brute force attacks due to the sheer size of the keys. Other attacks which aim to reduce this level of difficulty, by manipulating vulnerabilities in the algorithm itself, generally come up against the problem that most of the algorithms have a very strong theoretical base. However, researchers have demonstrated ways in which a cryptosystem can be compromised without having to attack the algorithm itself [10, 11].

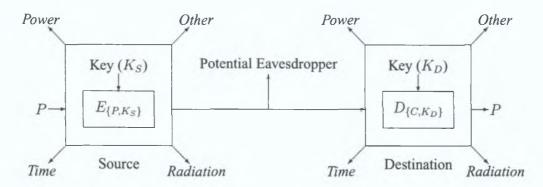

Every cryptographic cipher has to be implemented in one form or another in hardware. Due to the fundamental laws of physics governing this hardware, emissions will be produced that may or may not reveal information about the operations it is running. These emissions can take different forms such as electromagnetic radiation, power fluctuations or timing fluctuations. Some can even be induced by an attacker using a technique known as *fault induction*. As stated already, any emission that can be used to reveal secret information is known as a compromising emission. These emissions have proven to be a serious threat to the security of cryptosystems and are discussed in more detail next.

#### 1.2.1 Compromising Emissions

Compromising Emissions are normally referred to as Compromising Emanations in military and NSA documents. One definition is as follows and is taken from [12]:

"Compromising Emanations: Unintentional signals that, if intercepted and analyzed, would disclose the information transmitted, received, handled, or otherwise processed by information systems equipment".

These signals can be conducted, radiated, reactively coupled, exposed through power and timing fluctuations or even acoustically transmitted. In fact, any way a signal

can be intercepted beyond its intended channels would be considered compromising (assuming that the information is of a sensitive nature).

Power and timing fluctuations are different from the rest in the sense that power and time are resources required by the implementation circuitry to perform its functions. The others are only by-products of its actual operation, and are not required resources. For example, it is not necessary that the device emit electromagnetic radiation in order to operate (assuming it does not use some form of wireless communication) however, it is necessary that the device receive varying amounts of power and time. Reduction of the radiated emissions will not hinder the device in any way, and may even improve it's operation in some instances. On the other hand, reduction of power consumption below its required level will ultimately make the device inoperable.

Whether the signal is a "by-product" emission or a power fluctuation, it is necessary to know how the signal can move from one point to another within a system or between two systems. There are three main physical mechanisms by which a signal can propagate from its original source. These may act together or they may act independently and their effects will be different depending on the systems themselves and on the distance from the source.

- Conduction- Conducted propagations are generated by actual physical connections either within a system or from one system to another or to its power supply.

These are most effective at frequencies below 30 MHz. Above this frequency substantial attenuation takes place and it becomes the least dominant mechanism.

- Reactive Coupling- This can exist within a single system or between two systems. There are a number of factors which affect the amount of reactive coupling and these include, orientation of the systems or subsystems, distance, earthing

etc. Reactive coupling comes in the form of either capacitive or inductive coupling. The fact that high voltages (or high impedances) give rise to a large electric (E) field accounts for the capacitive coupling between wires, whereas high currents (or low impedances) will give rise to large magnetic (H) fields which account for inductive coupling. This latter statement can be seen from Faraday's law:

$$\xi = -N \frac{d\phi_B}{dt} \tag{1.3}$$

where it can be seen that the EMF  $(\xi)$  induced in a coil is proportional to the negative of the time rate of change of the magnetic flux cutting the coil  $(\phi_B)$ . This changing magnetic flux would generally be set up by current fluctuations in a nearby circuit/system.

3. Radiation- Most electronic devices will have some part of their circuit forming a loop or a dipole, and it is configurations such as this that will cause the radiation of electromagnetic energy. As was mentioned, conductive emissions tend to be substantial below 30 MHz. Above this frequency these emissions become less noticeable in relation to the radiated emissions which become dominant.

The problem of compromising radiation is not improving with technology but is actually getting worse. As more and more manufacturers begin to use wireless technology and the frequency of processors in personal computers (PC's) increase, the level of radiation emanating from a system will also increase. If some of the information signal being processed by the system happens to get coupled onto a loop or dipole type arrangement in the circuit, there is a good chance that it will modulate the radiated signal. This can sometimes be demodulated with something as simple as an average AM radio receiver [13]. This problem will be studied in more detail in chapter 3.

These are all methods which can be fatal to a systems security. It is necessary when designing secure systems that each of these mechanisms be reduced as much as possible.

Another mechanism by which information can be obtained is through a technique known as fault induction. If one can induce faults into a system, then these faults may leak information. For example, a system might only send ciphertext depending on whether or not a certain bit in a register is set or clear. If the bit is set, then the system might encrypt the data, however if it is clear then it might send the plaintext in an ordinary manner. If an attacker could find a way of changing the value of this bit, then the system could be easily compromised. This is a fairly simple example but it demonstrates the idea.

Having discussed some of the physical mechanisms through which information can leak from a system, it is clear that the traditional model of figure 1.3 needs to be reviewed. Figure 1.4 shows an updated version which incorporates the above side channels. The emission "other" might include sound or light (e.g. diodes flashing on and off) but also incorporates emissions that have yet to be identified. In fact, there appears to be another form which has not yet been disclosed by the US government. This can be seen in [14] under the section 'Introduction to TEMPEST' where a list of compromising emanations is given with one item redacted and replaced by x's. This may be something to bear in mind for designers of cryptosystems. It is also stated in the same document that the majority of compromising emanations are generated in electromagnetic field form which is probably the reason the US Government has directed considerable resources into the classified TEMPEST program.

Figure 1.4: Updated model of a cryptographic communication system incorporating side channel emissions.  $K_S$  may or may not equal  $K_D$  depending on the cryptographic scheme used.

#### 1.2.2 Tamper Resistance

Tamper resistance is the name given to any mechanism which aims to prevent secret information within a physical device from being compromised whilst inside that device. Tamper resistance has been in use for centuries [15]. Techniques such as weighted naval code books (that would sink if required), codes printed in water-soluble ink, and Russian one-time pads printed on cellulose nitrate (this has an explosive flammability and would destroy the pads within seconds if lit) have all been used. Even with these methods in place, a lot of systems have been compromised simply due to the fact that the operators were not vigilant enough. As a result, most modern tamper resistance techniques rely on technology and not on the operator. For example, tamper sensing meshes are placed within the casing of cryptographic devices to detect if an intruder is attempting to drill a hole and enter the system. Building a perfectly tamper resistant device seems like an elusive goal but it is an active area of research at present [16–18].

#### 1.3 FIPS Standards

The main motivation for this thesis is a standard taken from a set of US government standards known as FIPS. The FIPS must be complied with by all US federal government agencies and government contractors processing sensitive but non-classified information. As mentioned already, FIPS is an anagram for Federal Information Processing Standards. The specific standard of concern for this thesis is FIPS 140-2 - "Security Requirements for Cryptographic Modules". The FIPS 140-2 outlines the security requirements that all federal government owned cryptographic modules, processing sensitive data, should comply with. It is a revision of the FIPS 140-1 and supersedes it as of May 2002. However, the FIPS 140-1 still remains valid but no devices have been tested against it since this date.

It might prove useful to have a brief look at the revisions FIPS 140-2 makes reference to [19]:

- Allow separation of plain text from other types of input or output through physically and logically separate ports.

- Strengthen authentication mechanisms and address minimum probabilities for guessing, false acceptance error rates and restrictions on feedback to users.

- Replace the old trusted Computer System Evaluation Criteria with Common Criteria for Information Technology Security Evaluation

- Add requirements for over-the-air re-keying for radio cryptographic modules

- Require four statistical random-number generator tests during self-testing instead of one, with higher statistical limits for random-number generation

- Cover new types of cryptographic attacks that use power or timing analysis or fault induction.

It is the last item on this list that is of concern here. These "new" attacks also cover the area of TEMPEST as mentioned, and all will be discussed in different levels of detail throughout this thesis.

The FIPS 140 set of standards defines 4 different security levels, each more stringent than the preceding one. Level 1 is the lowest and level 4 the highest. Generally the requirements of each level are supersets of each of the levels below it. It is possible for a cryptographic module to meet different levels for different operations, however the overall certified level is taken as the lowest one the module complies with.

The program that validates modules to these cryptographic standards is the Cryptographic Module Validation Program (CMVP) and the laboratories that carry out this validation have to be National Voluntary Laboratory Accreditation Program (NVLAP) accredited. A list of accredited laboratories can be found at [20].

The specific section of this standard under review in this thesis is section 4.11 and is entitled "Mitigation of other attacks". This is a completely new section and provides information about several new types of attacks (each of which has already been discussed). It was developed as a direct result of numerous public comments which suggested that they should be included in the revised standard (i.e. FIPS 140-2). The attacks were included following these comments, however no test procedures were given and in fact are not tested against in the general case. If the vendor of a cryptographic module states in it's security policy that mitigation techniques have been implemented, then the NVLAP laboratory has to test that claim [21]:

"An additional area concerned with the mitigation of other attacks is currently not tested but the vendor is required to document implemented controls (e.g., differential power analysis, and TEMPEST)."

This research aims to determine the vulnerability of the DUT to these attacks so that

pending tests (of which there are guaranteed to be a few) can be approached with a certain degree of confidence.

#### 1.4 Motivation and thesis aims

In the past decade research on side channel attacks has increased dramatically. Most of the results provided have turned out to be worrying for designers of systems such as smart cards. These are low power, minimal circuitry devices containing a microprocessor and some memory for storage of items such as cryptographic keys and personal information. Smartcards may not be the only devices at risk and it must be considered also that more complex cryptographic systems may also be vulnerable.