## The Development and Characterization of Novel Pd/Sn Ohmic Contacts to n-type GaAs

Thesis

Submitted to Dublin City University for the degree of

Doctor of Philosophy (PhD)

by

MD SHAFIQUL ISLAM, B Sc Eng, M Sc Eng

School of Electronic Engineering Dublin City University

> Research Supervisor Dr Patrick J McNally

> > February, 1997

ł

#### **DECLARATION**

I hereby certify that this material, which I now submit for assessment on the programme of study leading to the award of Doctor of Philosophy is entirely my own work and has not been taken from the work of others save and to the extent that such work has been cited and acknowledged within the text of my work.

Signed: ms. Mam Date: 25 February 1997.

#### ACKNOWLEDGEMENTS

I like to express my sincere appreciation to my supervisor Dr Patrick J McNally for his friendly and encouraging guidance for this work. He is a man of in depth knowledge in my research field and I am very grateful for his patience and discussions we shared during this course and also in writing this thesis. In real sense, Dr McNally introduced me in the world of Ohmic contact technology for GaAs devices

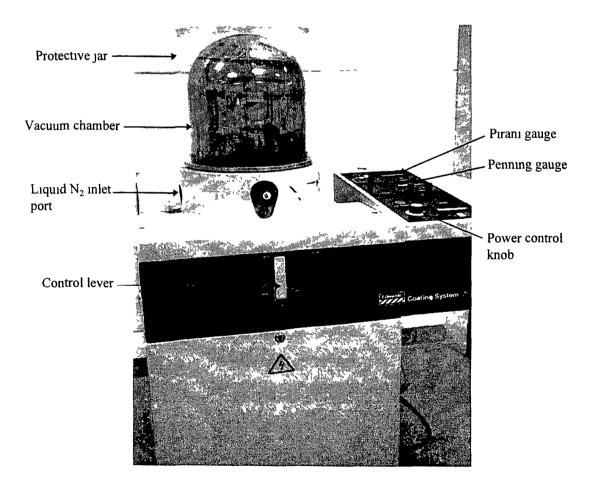

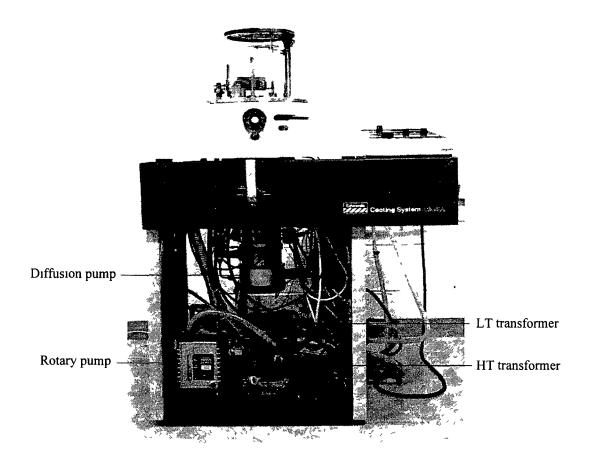

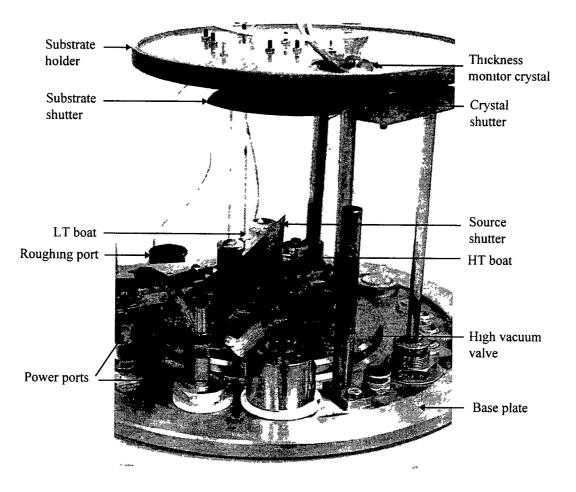

I am also indebted to my co-supervisor Dr David C Cameron for his knowledgeable and friendly help in the Edward Vacuum Coating system For his sincere guidance, I was able to familiarize with this system within a couple of months I appreciate him for his discussions during this work

I am very grateful to my wife Pew, for her constant inspiration, love, sacrifice, patience and understanding particularly during the cource of my research I remain in debt to her I am indebted to my mum who brought me in this beautiful world and cherished me perfectly

I am grateful to my elder brother Mr Rafiqul Alam, for his tireless support and encouragement to build up my career and to do this work I also thank to all other relatives and friends in Bangladesh for their well wishes for my work

I like to thank Professor M S J Hashmi and Professor Charles McCorkell for their encouragement and financial support during my research Thanks to Dr Tony Herbert, Plasma Ireland Ltd, for his co-operation m doing some of my experiments at the National Microelectronics Research Centre (NMRC), Cork, Ireland Also thanks to Dr Simon Romani for his assistance with SIMS at NMRC I am also grateful to Mr Paul Rozengrave, NMRC, Cork and Mr David John, Central Electron Microscope Unit, Trinity College, Dublin for their friendly assistance with SEM

I would like to thank John Whelan, Liam Meany, Conor Maguire, Paul Wogan, Peter McGorman and Stephen Neville of Electronic Engineering school for their help and co-operation throughout this work Thanks to Dr John Curley, Microelectronics Res Lab, for his encouragements in my research I am also grateful to Al Devine, School of Physical Sciences, DCU, who helped me a lot in taking photographs of my equipments and some of the experimental results He also helped me m scanning the photographs for my thesis

Finally, I like to thank all Bangladeshi students here in DCU and relatives in Ireland for their hospitality and encouragements in the last three years.

### **DEDICATION**

To my parents and To my wıfe

٤

\_

# **Contents**

| Acknowledgements |                       |                                            |    |  |  |

|------------------|-----------------------|--------------------------------------------|----|--|--|

| Li               | List of Symbols v     |                                            |    |  |  |

| Li               | List of Abbreviations |                                            |    |  |  |

| Al               | Abstract              |                                            | Х  |  |  |

| 1                | Introduct             | ion                                        | 1  |  |  |

|                  | 1.1 Introdu           | uction                                     | 1  |  |  |

|                  | 1.2 Ohmic             | contact formation mechanisms               | 4  |  |  |

|                  | 1.3 Recent            | t developments of Ohmic contacts           | 7  |  |  |

|                  | 1.3.1                 | Pd/Ge and Ge/Pd metallizations             | 8  |  |  |

|                  | 1.3.2                 | Pd/Ge/Ti/Pt metallizations                 |    |  |  |

|                  | 1.3.3                 | Pd/AuGe/Ag/Au metallizations               |    |  |  |

|                  | 1.3.4                 | Pd/Si metallizations                       |    |  |  |

|                  | 1.3.5                 | Pd/In metallizations                       |    |  |  |

|                  | 1.3.6                 | AuGe/Ni metallizations                     | 14 |  |  |

|                  | 1.3.7                 | Multilayer Au/Ge/Au/Ni/Au metallizations   | 17 |  |  |

|                  | 1.3.8                 | Ni/AuGe/Ag/Au metallizations               | 18 |  |  |

|                  | 1.3.9                 | Au/Ni/NiSn metallizations                  | 19 |  |  |

|                  | 1.3.10                | NiInW metallizations                       | 19 |  |  |

|                  |                       | Ni-based non-gold metallizations           |    |  |  |

|                  | 1.3.12                | Au-Ge metallizations                       | 23 |  |  |

|                  | 1.3.13                | Au/Te/Au metallizations                    | 24 |  |  |

|                  | 1.3.14                | High-temperature refractory metallizations |    |  |  |

|                  |                       | InAs-based metallizations                  |    |  |  |

|                  | 1.4 Applic            | cations of Ohmic contacts to n-GaAs        | 29 |  |  |

|                  |                       | usions                                     |    |  |  |

|                  | 1.6 Organ             | isation of this thesis                     |    |  |  |

| 2                | •                     | s of this research                         | 34 |  |  |

|                  | 2.1 Introdu           | uction                                     | 34 |  |  |

|     | 2 2 Objec                      |                                                         | 35       |

|-----|--------------------------------|---------------------------------------------------------|----------|

|     | 2 3 Chara                      | cterization of the contacts                             | 36       |

|     |                                |                                                         |          |

| 3   | Optımıza                       | ition of Pd and Sn evaporation rates for better surface |          |

|     | morphol                        | ogy of the Pd/Sn contacts                               | 37       |

|     | 3 1 Introd                     | luction                                                 | 37       |

|     | 3 2 Exper                      | riments                                                 | 38       |

|     | 3 3 Resul                      | ts                                                      | 38       |

|     | 3 4 Sumn                       | nary                                                    | 44       |

| 4 - | Pd/Sn Ohmic contacts to n-GaAs |                                                         | 45       |

|     | 4 1 Introd                     | luction                                                 | 45       |

|     | 4 2 Conve                      | entional TLM (cTLM) method                              | 45       |

|     | 4 3 Exper                      | riments                                                 | 47       |

|     | 4 4 Resul                      | ts and discussions                                      | 48       |

|     | 441                            | Electrical characteristics                              | 48       |

|     | 442                            | Surface profilometry measurements                       | 50       |

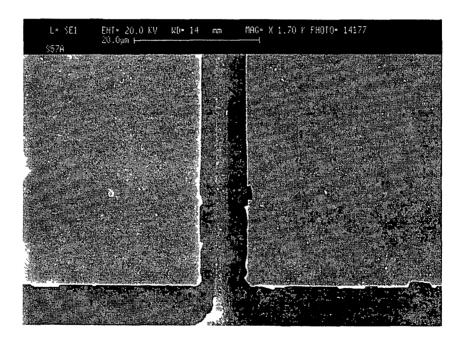

|     | 443                            | Surface morphology using SEM                            | 52       |

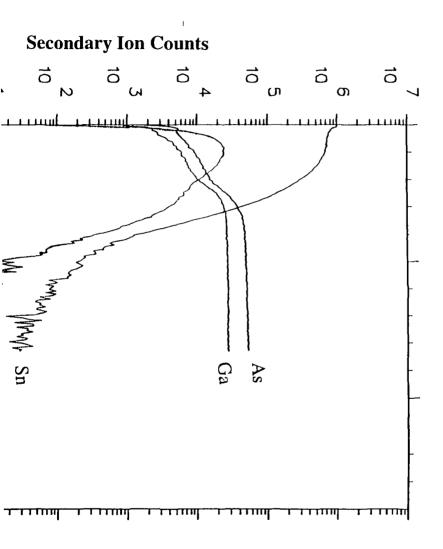

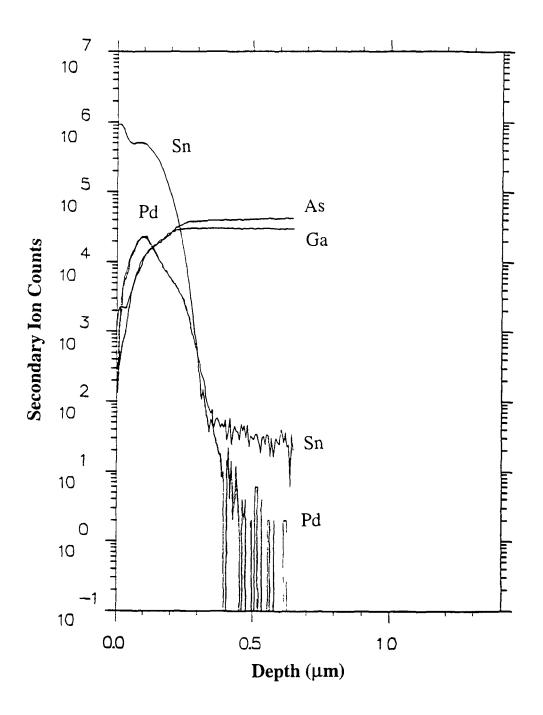

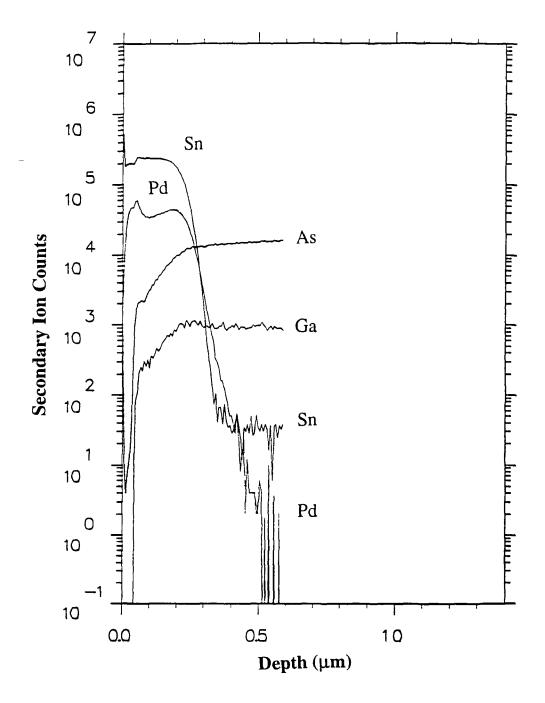

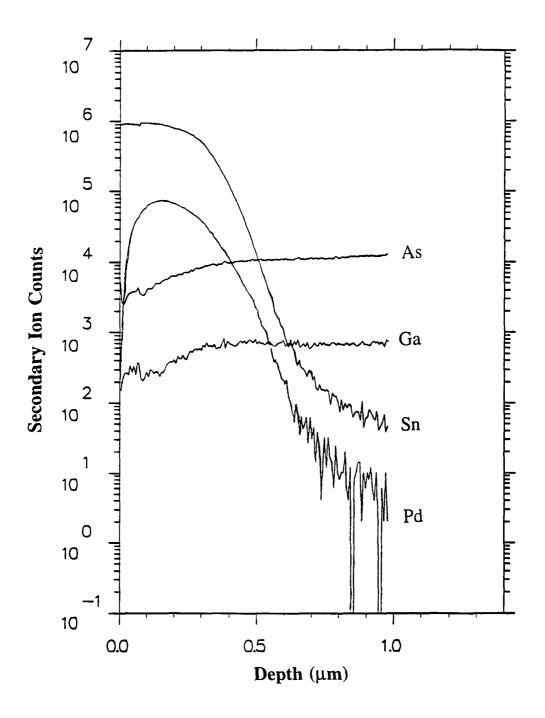

|     | 444                            | Contact depth profiles using SIMS                       | 54       |

|     | 445                            | Mass spectrometer analysis                              | 60       |

|     | 446                            | Correlation between Ga signal and contact behaviour     | 62       |

|     | 447                            | Effect of layering sequence                             | 64       |

|     | 448                            | Effects of two-step annealing on the characteristics of |          |

|     |                                | Pd/Sn Ohmic contacts                                    | 65       |

|     | 4 5 Sumn                       | nary                                                    | 69       |

| 5   |                                | f Au overlayers on the characteristics of Pd/Sn Ohmic   |          |

|     |                                | to n-GaAs                                               | 71       |

|     | 5 1 Introduction               |                                                         | 71       |

|     | 5 2 Experiments                |                                                         | 71       |

|     | 5 3 Results and discussions    |                                                         | 72       |

|     | 531                            | Electrical characteristics                              | 72       |

|     | 532                            | Surface profilometry measurements                       | 74       |

|     | 533                            | Surface morphology using SEM                            | 76       |

|     | 534                            | Contact depth profiles using SIMS                       | 79       |

|     | 535                            | Mass spectrometer analysis                              | 81<br>84 |

|     | 5 4 Conclusion                 |                                                         |          |

-

| 6 | Comparison of Pd/Sn, Pd/Ge, Pd/Sn/Au and alloyed Au-Ge/N1       |     |  |  |

|---|-----------------------------------------------------------------|-----|--|--|

|   | Ohmic contacts to n-GaAs                                        |     |  |  |

|   | 6 1 Introduction                                                |     |  |  |

|   | 6 2 Experiments                                                 |     |  |  |

|   | 6 3 Results and discussions                                     |     |  |  |

|   | 6 3 1 Electrical characteristics                                | 86  |  |  |

|   | 6 3 2 Surface morphology using SEM                              | 87  |  |  |

|   | 6 4 Conclusion                                                  | 89  |  |  |

| 7 | Thermal and long-term stability of the Pd/Sn and Pd/Sn/Au Ohmic |     |  |  |

|   | contacts to n-GaAs                                              |     |  |  |

|   | 7 1 Introduction                                                | 91  |  |  |

|   | 7 2 Experiments                                                 | 91  |  |  |

|   | 7 3 Results and discussions                                     | 92  |  |  |

|   | 7 3 1 Thermal stability at 410 $^{0}$ C                         | 92  |  |  |

| 1 | 7 3 2 Long-term stability at 300 $^{\circ}$ C                   | 95  |  |  |

|   | 7 4 Conclusion                                                  | 98  |  |  |

| 8 | Fabrication of GaAs MESFETs using Pd/Sn and Pd/Sn/Au            |     |  |  |

|   | Ohmic contacts                                                  | 100 |  |  |

|   | 8 1 Introduction                                                | 100 |  |  |

|   | 8 2 Experimental procedures                                     | 100 |  |  |

|   | 8 2 1 Level 1 - Mesa isolation                                  | 100 |  |  |

|   | 8 2 2 Level 2 - Ohmic contacts                                  | 101 |  |  |

|   | 8 2 3 Level 3 - Schottky (Gate) contacts                        | 102 |  |  |

|   | 8 3 Results and discussions                                     | 103 |  |  |

|   | 8 3 1 Ohmic contacts                                            | 103 |  |  |

|   | 8 3 2 MESFET characterization                                   | 104 |  |  |

|   | 8 4 Conclusion                                                  | 115 |  |  |

| 9 | Conclusions and suggestions for future research                 |     |  |  |

|   | 9 1 Conclusions                                                 |     |  |  |

|   | 9 2 Suggestions for future research                             |     |  |  |

|   | References                                                      |     |  |  |

|   | Appendix A Resistance heating (thermal) evaporator              | A1  |  |  |

|   | Appendix B Graphite strip annealer                              | B1  |  |  |

| Appendıx C | Original STM photographs of the Pd/Sn<br>contacts to GaAs(SI) |    |

|------------|---------------------------------------------------------------|----|

| Appendıx D | Calculation of pinch off voltage                              | D1 |

| Appendix E | Publications based on this work                               | E1 |

---

1

~

# **List of Symbols**

| A                | contact area                                              |

|------------------|-----------------------------------------------------------|

| Å                | metallization thickness                                   |

| d                | channel depth                                             |

| E <sub>C</sub>   | conduction band minimum                                   |

| E <sub>F</sub>   | Fermi level                                               |

| Ev               | valence band maximum                                      |

| $E_{g}$          | band gap                                                  |

| Eoo              | tunneling parameter                                       |

| g <sub>m</sub>   | transconductance                                          |

| $g_m(int)$       | intrinsic transconductance                                |

| 8 max            | maximum transconductance                                  |

| h                | Planck's constant                                         |

| I <sub>GS</sub>  | gate current                                              |

| $I_{DS}$         | dram current                                              |

| I <sub>DSS</sub> | drain saturation current                                  |

| J                | current density                                           |

| k                | Boltzmann constant                                        |

| L                | separation between the contacts                           |

| $L_c$            | contact length                                            |

| $L_T$            | transfer length                                           |

| $L_G$            | gate length                                               |

| $L_{GS}$         | gate-to-source distance                                   |

| L <sub>GD</sub>  | gate-to-drain distance                                    |

| m                | electron effective mass                                   |

| m                | Sn to Pd thickness ratio                                  |

| $N_D$            | donor concentration                                       |

| q                | electronic charge                                         |

| R <sub>c</sub>   | contact resistance                                        |

| $R_T$            | total resistance                                          |

| R <sub>sh1</sub> | sheet resistance of the active layer under the contact    |

| R <sub>sh2</sub> | sheet resistance of the active layer between the contacts |

| $R_p$            | resistance of the interconnect wires                      |

- R<sub>a</sub> average surface roughness

- $R_S$  series resistance

- T temperature

- TIR maximum peak-to-valley distance of the scanned surface

- T<sub>m</sub> melting point

- T<sub>an</sub> annealing temperature

- V voltage

- $V_P$  punch off voltage

- $V_B$  built in potential

- $V_{DS}$  drain-to-source voltage

- $V_{GS}$  gate-to-source voltage

- $V_F$  diode forward voltage

- W contact width

- $\rho_c$  contact resistivity

- $\Delta \rho_c$  measurement error

- $\Omega$  resistance

- $\phi_B$  barrier height

- $\epsilon$  dielectric constant of the semiconductor

- $\phi_m$  metal work function

- $\phi_s$  semiconductor work function

# **List of Abbreviations**

| AES     | Auger Electron Spectroscopy                              |

|---------|----------------------------------------------------------|

| CHINT   | Charge injection transistor                              |

| cTLM    | Conventional transmission line model                     |

| DI      | De-10n1zed                                               |

| EDAX    | Energy Dispersive Analysis of X-rays                     |

| FE      | Field emission                                           |

| FEM     | Field Emission SEM                                       |

| HEMT    | High electron mobility transistor                        |

| HBT     | Heterojunction bipolar transistor                        |

| I-V     | current-voltage                                          |

| LPMOCDV | Low pressure organometallic chemical vapor deposition    |

| LED     | Light emitting diode                                     |

| MESFET  | Metal semiconductor field-effect transistor              |

| MQW     | Multiple quantum-well                                    |

| MODFET  | Modulation doped field-effect transistor                 |

| MOVPE   | Metal-organic vapor phase epitaxy                        |

| NERFET  | Negative differential resistance field-effect transistor |

| RTA     | Rapid thermal annealing                                  |

| RTP     | Rapid thermal processing                                 |

| SEB     | Scanned electron beam                                    |

| SLS     | Strained layer superlattice                              |

| SD      | Switching diode                                          |

| STM     | Scanning Tunneling Microscopy                            |

| SEM     | Scanning Electron Microscopy                             |

| SIMS    | Secondary Ion Mass Spectrometry                          |

| SI      | Semi-insulating                                          |

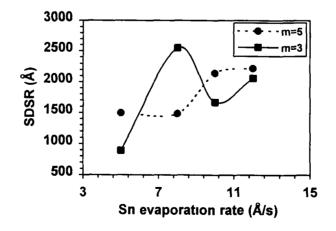

| SDSR    | Standard deviation of surface roughness                  |

| TE      | Thermionic emission                                      |

| TFE     | Thermionic field emission                                |

| TEM     | Transmission Electron Microscopy                         |

| TLM     | Transmission line model                                  |

| 2DEG    | Two-dimensional electron gas                             |

| XRD     | X-ray diffraction                                        |

|         |                                                          |

### The Development and Characterization of Novel Pd/Sn Ohmic Contacts to n-type GaAs

#### MD. SHAFIQUL ISLAM

#### Abstract

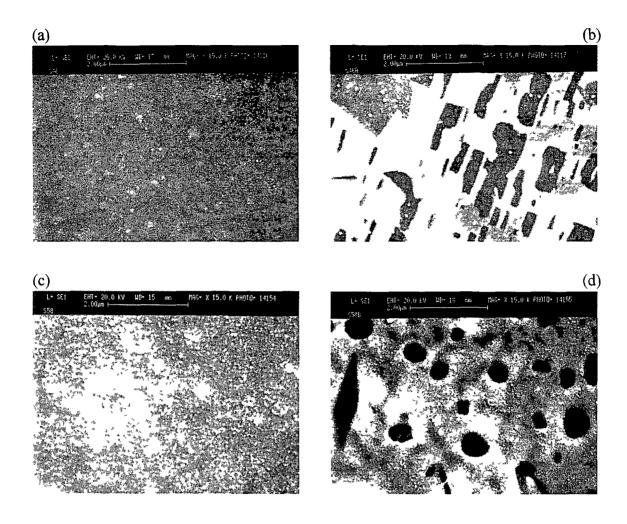

A novel Ohmic contact system comprising of Pd/Sn metallizations has been developed for n-GaAs and systematically characterized using Scanning Tunneling Microscopy (STM), Scanning Electron Microscopy (SEM), Surface Profilometry measurements, Secondary Ion Mass Spectrometry (SIMS), Energy Dispersive Analysis of X-rays (EDAX) and current-voltage (I-V) measurements. Contact resistivities,  $\rho_c$ , of the proposed metallizations are measured utilizing a conventional Transmission Line Model (cTLM) method. The Pd/Sn metallizations show lowest  $\rho_c$  in the range of low 10<sup>-5</sup>  $\Omega$ -cm<sup>2</sup> on Si-doped (2x10<sup>18</sup> cm<sup>-3</sup>) n-GaAs. A Au overlayer improves the characteristics of the Pd/Sn Ohmic contacts. The Pd/Sn/Au contacts display lowest  $\rho_c$  in the range of low 10<sup>-6</sup>  $\Omega$ -cm<sup>2</sup>. The Pd/Sn and Pd/Sn/Au contacts exhibit improved characteristics when compared with alloyed Au/Ge/Au/Ni/Au contacts.

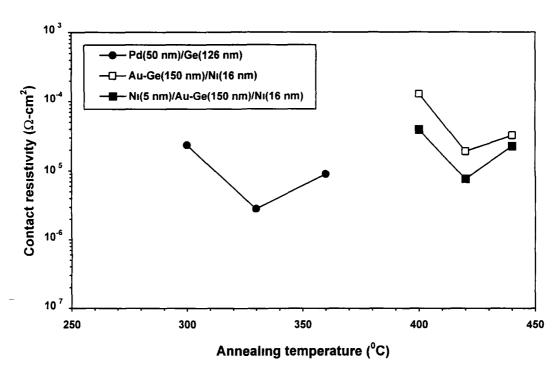

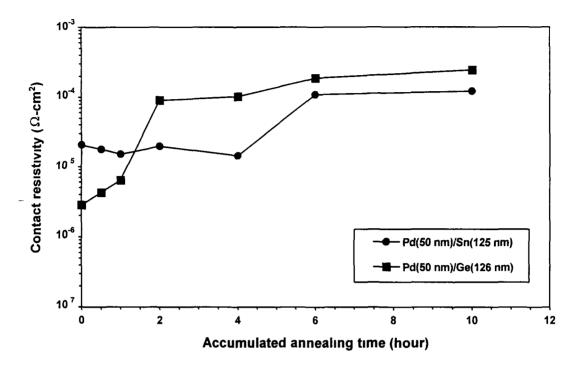

The Pd/Sn and Pd/Sn/Au metallizations show better thermal stability at 410  $^{0}$ C than non-alloyed Pd/Ge contacts. The Pd/Sn/Au metallizations also display better thermal stability than alloyed eutectic Au-Ge/Ni and Ni/Au-Ge/Ni contacts. However, at this temperature thermal stability of the Pd/Sn/Au metallizations is comparable to that of alloyed Au/Ge/Au/Ni/Au contacts. Long-term stability of the Pd/Sn/Au metallizations at 300  $^{0}$ C is comparable to non-alloyed Pd/Ge contacts. No change in surface morphology is observed after having been annealed at 300  $^{0}$ C for 400 h. At 300  $^{0}$ C, the Pd/Sn/Au metallization exhibits  $\rho_{c}$  which is slightly higher than those of the alloyed Au-Ge/Ni, Ni/Au-Ge/Ni and Au/Ge/Au/Ni/Au contacts.

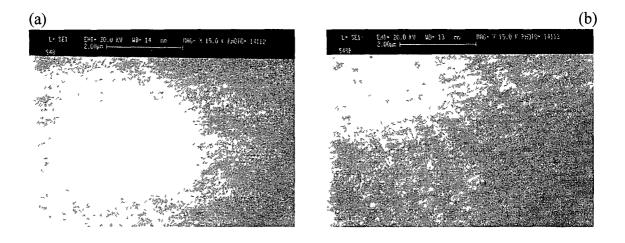

GaAs Metal Semiconductor Field-Effect Transistors (GaAs MESFETs) have been fabricated using Pd/Sn and Pd/Sn/Au metallizations as source/drain contacts. MESFETs fabricated with Pd/Sn/Au Ohmic contacts display improved characteristics when compared to Pd/Sn contacts. MESFETs fabricated with Pd/Sn/Au contacts show comparable edge uniformity to non-alloyed Pd/Ge metallizations which is very important for VLSI GaAs devices. The newly developed, thermally stable, Pd/Sn and Pd/Sn/Au metallizations appear to be promising candidates for future GaAs device technology.

# CHAPTER 1 Introduction

### **1.1 Introduction**

The purpose of an Ohmic contact to a semiconductor is to allow electrical current to flow into or out of the semiconductor. The contact should have a linear I-V characteristic, be stable over time and temperature, and contribute as little resistance as possible. Simply placing a metal in contact with a wide bandgap III-V compound semiconductor, such as GaAs generally results in a rectifying contact (a diode) rather than an Ohmic one. Therefore, achieving a stable, low-resistance Ohmic contact has been as much technical art as science, and this problem generated a large amount of research over several decades.

Recent remarkable progress in semiconductor technology has made it possible to fabricate high performance GaAs devices [1] Although many useful contact schemes have been developed, further improvements in contact resistance are still necessary in order to keep pace with developments in the novel device design. The primary requirements of Ohmic contacts are a low contact resistivity, an insignificant contact metal diffusion into the semiconductor both laterally and vertically, reproducibility, thermal stability and reliability

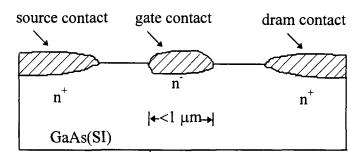

Advances in ultra-fast electronics and optoelectronics have considerably accelerated demand for GaAs devices in recent years. This has been achieved through an improvement in GaAs device fabrication and processing techniques, new device structures and new circuit designs. The need for a reliable and well-controlled Ohmic contact is central to the successful operation of almost all GaAs devices. Achieving a low resistance Ohmic contact to GaAs is not trivial, and requiring in addition that the contact be thermally stable during subsequent processing at temperatures up to 400 °C (about 800 °C if the contact is to be used as a mask for dopant implants), morphologically uniform on the 0.1  $\mu$ m scale and compatible with conventional lithographic patterning techniques, presents a formidable challenge. Yet the development of low resistance contacts that meet these requirements is necessary for further miniaturization of devices such as the GaAs metal-semiconductor field-effect transistor (MESFET) shown in Fig 1.1 In this device, lateral encroachment of the

source and drain Ohmic contacts towards gate contact can occur during the contact annealing treatment, thereby limiting the minimum gate-to-source and gate-to-drain separation

Fig 1.1 Schematic diagram of sub- $\mu$ m GaAs-MESFET illustrating the demands on contact metallizations [2]

In the MESFET, the source and dram resistances are key parameters that determine its performance. The source resistance strongly affects the device transconductance and noise figure. An increase in both source and dram resistances tends to increase the power consumption and slow down device operation. Low contact resistivity is also required in efficient optoelectronic devices both from the point of view of power consumption and heat dissipation.

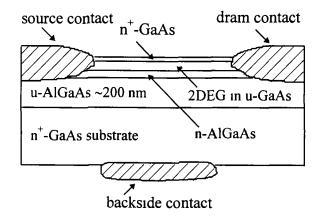

Fig 1.2 Schematic diagram of the NERFET illustrating the demands on contact metallizations [3]

The scaling of GaAs devices to submicrometre dimensions imposes more stringent requirements on the electrical and metallurgical characteristics of Ohmic contacts The morphological constrains on low resistance contacts are even more severe for heterojunction devices in which the current is confined in the form of a two-dimensional electron gas (2DEG) at the buried interface (e g GaAs-Al<sub>1-x</sub>Ga<sub>x</sub>As) For example, the source and dram contacts in the negative differential resistance field-effect transistor (NERFET) [3] (Fig 1 2) must make contact with the buried 2DEG without

penetrating the thin (about 200 nm)  $Al_{1-x}Ga_xAs$  barrier layer Even a localized penetration will introduce a path for excessive leakage current and render the device inoperable

Smaller intrinsic resistances make the problem of low contact resistivity more acute For Gunn diodes and LEDs, contact resistivity,  $\rho_c = 10^{-3} \cdot 10^{-5} \Omega \cdot cm^2$  has been adequate since the Ohmic contacts employed in these devices are realtively large in area and the resulting contact resistivity can easily be smaller than a few Ohms For MESFETs with 1 µm gate, a  $\rho_c$  of mid 10<sup>-6</sup>  $\Omega$ -cm<sup>2</sup> may suffice, but for sub-µm devices, where the semiconductor channel resistance is lower by more than a factor of two, the  $\rho_c$  should be reduced to low 10<sup>-6</sup>  $\Omega$ -cm<sup>2</sup>

From the point of view of metallurgical characteristics, requirements for fine pattern capability and precise control of the penetration depth of the Ohmic contact have become crucial Modern device designs require contacts with morphological uniformity such that lateral depth definition and depth of penetration of the metallization can be controlled to within tens of nanometres Fine pattern capability is necessary for minimizing gate-to-source spacing in all types of field-effect transistors To realize the high dc current gam, high speed and high microwave cut-off frequency capabilities of thin base heterojunction bipolar transistors (HBTs), vertical scaling of the Ohmic contact is necessary to avoid contact penetration into the adjacent active region of the HBT. In the case of a high electron mobility transistor (HEMT), a rigid control is required on the vertical scaling of source and drain contacts providing an Ohmic contact directly to the 2DEG channel [1]

It is clear therefore that with ongoing miniaturization and integration of GaAs devices, the ever-increasing demand for high performance Ohmic contacts is one of the more challenging problems in GaAs IC technology Many reports describing Ohmic contacts to GaAs already exist in literature, including a number of reviews The reviews by Rideout [4], Popovic [5] and Piotrowska [6] present a theoretical treatment as well as a summary of research activities prior to 1983 Shen et al [7] very concisely treated a number of basic issues related to Ohmic contacts on GaAs The role of mterfacial reactions in Ohmic contact formation is described by Piotrowska [8] and Sands [2] Additionally, information regarding Ohmic contacts can also be found in a number of reference books [9-12]

$\mathbf{n}$

The remainder of this chapter is concerned with a brief discussion of Ohmic contact formation mechanisms. This will be followed by a detailed review of recent and important research activities related to Ohmic metallizations for n-GaAs. Different

Ohmic contact schemes will also be summarized for various GaAs device applications The relative advantages and disadvantages of each contact scheme will be pointed out Finally, the organisation of this thesis will be presented

### **1.2 Ohmic Contact Formation Mechanisms**

An Ohmic contact is defined as a metal-semiconductor (M-S) contact that has a linear current-voltage (I-V) characteristics and also has a negligible contact resistance relative to the bulk or spreading resistance of the semiconductor A satisfactory Ohmic contact should not significantly perturb device performance and it can supply the required current with a voltage drop that is sufficiently small compared with the drop across the active region of the device If  $R_c$  is the contact resistance and A is the contact area then the contact resistivity  $\rho_c$  is given by the product of  $R_c$  and A When evaluated at zero bias, this  $\rho_c$  is an important figure of merit for Ohmic contacts A formal definition of  $\rho_c$  is usually given as

$$\rho_c = \left\{ \left( \frac{\partial J}{\partial V} \right)_{V=0} \right\}^{-1} \quad (\Omega-\mathbf{cm}^2), \tag{11}$$

where J=current density (ampere/cm<sup>2</sup>) and V=applied voltage across the contact (volts)

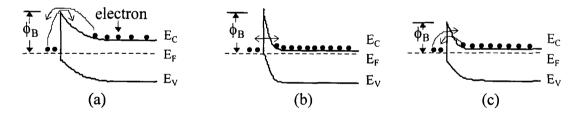

Fig 1.3 Ohmic contact formation mechanisms (a) TE, (b) FE and (c) TFE The conduction band minimum, Fermi level and valence band maximum are indicated by  $E_C$ ,  $E_F$  and  $E_V$ , respectively

Basically, there are three mechanisms [9] which govern the current flow in a M-S contact These mechanisms are described below very concisely

Thermionic emission (TE): dominant in moderately doped semiconductors, N<sub>D</sub><(~10<sup>17</sup> cm<sup>-3</sup>) In this case, the width of depletion region is relatively wide, implying that the probability of electrons tunneling through the barrier is rather small If the barrier height (φ<sub>B</sub>) is small, the electrons can easily surmount the top of the low barrier by thermionic emission (Fig 1 3(a)) For low doped or high-barrier semiconductors, the vast majority of electrons are unable to overcome this barrier in either direction and result in non-Ohmic (rectifying) contacts

- Field emission (FE): effective in heavily doped semiconductors,  $N_D > (\sim 10^{18} \text{ cm}^{-3})$ For this situation, the depletion region is so narrow that electrons can easily tunnel through the barrier and tunneling is the dominant transport mechanism (Fig 1 3(b))

- Thermionic-field emission (TFE): applicable for intermediately doped semiconductors, (~10<sup>17</sup> cm<sup>-3</sup>)<N<sub>D</sub><(10<sup>18</sup> cm<sup>-3</sup>) Both thermionic and tunneling are significant as shown m Fig 1 3(c)

For each of these three mechanisms, the contact resistivity  $\rho_c$  can be calculated with the help of a very useful parameter  $kT/E_{oo}$  introduced by Yu [13], where

$$E_{oo} = \frac{qh}{4\pi} \sqrt{\frac{N_D}{\epsilon m^{*}}}$$

(12)

$E_{oo}$  is the tunneling parameter, q is the electronic charge, h is the Planck's constant,  $N_D$  is the donor concentration,  $\varepsilon$  is the dielectric constant of the semiconductor, and  $m^*$  is the electron effective mass

For  $kT/E_{oo} >> 1$ , i.e. for moderate  $N_D$ , the TE mechanism dominates the current conduction and the contact resistivity is given by

$$\rho_c \propto \exp \frac{q \phi_B}{kT} \tag{13}$$

From eqn (1 3), it is clear that the contact resistivity is dependent on temperature At higher temperatures, the thermionic emission current increases resulting m a smaller  $\rho_c$  For  $kT/E_{oo}\approx 1$ , i.e. for intermediate  $N_D$ , a mixure of both thermionic and tunneling mechanisms (TFE) is observed and the contact resistivity is

$$\rho_{c} \propto \exp \frac{q \phi_{B}}{E_{oo} \coth \frac{E_{oo}}{kT}}$$

(14)

It is seen that the contact resistivity depends on both the temperature and the transmission coefficient for tunneling

For  $kT/E_{oo} \ll 1$ , i.e for heavy doping concentrations, contact resistivity becomes

$$\rho_{\iota} \propto \exp \frac{q \phi_{B}}{E_{oo}} \tag{15}$$

In this case,  $\rho_c$  depends strongly on doping concentration and the field emission (FE) mechanism prevails As the doping concentration is increased further, the depletion width of the Schottky junction decreases resulting in an increase of the tunneling transmission coefficient Hence, even a metal with a high barrier to the semiconductor can form an Ohmic contact

If a large number of surface states exists in the semiconductor, the Fermi level is pinned and the barrier height is independent of the metal work function. This is the Bardeen limit [14] which stands in contrast to the Schottky limit where the metalsemiconductor contact is assumed ideal and the surface states are ignored. In practice, the surface Fermi levels of most III-V compound semiconductors are pinned somewhere in the gap, which is what determines the barrier height. It can then be concluded that the barrier height depends not only on the gap of the semiconductor, but also on the surface state density.

Three mam approaches have been used to obtain low  $\rho_c$  Ohmic contacts on n-GaAs These three approaches are described below very briefly

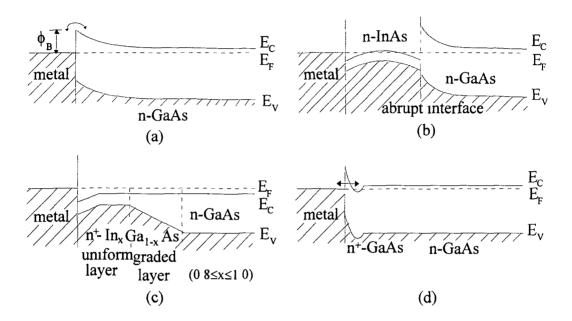

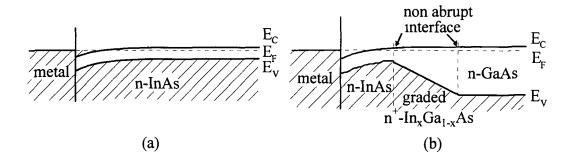

- Contacts to very small band gap semiconductors: When a metal is brought into contact with a semiconductor, the Fermi levels in the metal and semiconductor must align under equilibrium conditions (Fig 1 4(a)) If the work function of the metal  $(\phi_m)$  is smaller than the work function of the semiconductor  $(\phi_s)$ , the Fermi levels are aligned by transferring electrons from the metal to the semiconductor. This raises the semiconductor electron energy relative to the energy of electrons in the metal at equilibrium. The Fermi level is pinned in the conduction band of the small band gap material, for example InAs ( $E_g \sim 0.36 \text{ eV}$ ) (Fig 1 4(b)), therefore, the junction has a very small  $\rho_c$ , in the range of  $10^{-7}$ - $10^{-8} \Omega$ -cm<sup>2</sup> (TE mechanism) [15]

- Contacts in the case of low barrier height and heavily doped semiconductors: This approach is also successful for attaining low ρ<sub>c</sub> (TFE mechanism) For example, contacts made on n<sup>+</sup>-InGaAs (E<sub>g</sub>~0.75 eV)/GaAs exhibit a contact resistivity in the range of 10<sup>-6</sup>-10<sup>-8</sup> Ω-cm<sup>2</sup> (Fig 1.4(c)) [16,17]

- Contacts in the case of heavily doped semiconductors: The heavier the doping at the semiconductor surface, the thinner the barrier width, and carriers can tunnel more easily between the metal and the semiconductor (FE mechanism) (Fig 1 4(d)) Contacts made on GaAs (E<sub>g</sub>~1 42 eV) with a surface doping of 10<sup>18</sup>-10<sup>20</sup> cm<sup>-3</sup> fall into this category Contact resistivities in the range of 10<sup>-5</sup>-10<sup>-7</sup> Ω-cm<sup>2</sup> are generally obtained [18-21]

In particular, the contact resistivity depends greatly on the doping level in the semiconductor, the barrier height of the metal-semiconductor combination, carrier effective mass, dielectric constant and temperature

In practice, the most widely used Ohmic contacts to GaAs today involve multicomponent metallization systems prepared by conventional deposition and annealing techniques Heat treatment is used to drive a suitable dopant from the metallization into the GaAs surface region to form a tunneling junction and/or to fabricate, in contact reaction, a suitable heterojunction with low effective barrier height

Fig 1.4 Schematic diagrams of band bending for various metal/semiconductor interfaces The conduction band minimum, Fermi level and valence band maximum are indicated by  $E_c$ ,  $E_F$  and  $E_v$ , respectively

- (a) The typical band line-up for metals deposited on air exposed n-GaAs {100} Under bias, electrons are transported by thermionic emission over the ~0 8 eV energy barrier [2]

- (b) Band diagram for metal/n-InAs/n-GaAs [7]

- (c) Band diagram for metal/n<sup>+</sup>-In<sub>x</sub>Ga<sub>1-x</sub>As (0  $8 \le x \le 1$  0)/n-GaAs [17]

- (d) Band diagram for metal/ $n^+$ -GaAs (heavily doped) [2]

### 1.3 Recent Developments of Ohmic Contacts

The most important areas of recent investigations into Ohmic contacts to n-GaAs are those involving the use of rapid thermal annealing (RTA) or rapid thermal processing (RTP), scanned electron beam (SEB) annealing, electroless deposition of metals, the  $\delta$ doped epilayer technique, development of refractory metallizations and the application of heavily doped and/ or small band gap materials [17, 18, 22-28] Metallizations containing dopant elements, such as Si, Ge and Sn for n-GaAs are preferred in order to form heavily doped surface layers that are essential for low  $\rho_c$  contacts [19, 20, 29, 30] At high temperatures, out-diffusion of GaAs constituents occur Therefore, it is necessary to incorporate a barrier layer to reduce this outdiffusion A variety of materials have been used as barrier layers refractory metals (platinum, palladium, chromium, molybdenum, tungsten, etc.) and related alloys (TiW, MoW, etc.), and above all, low resistivity compounds (borides, nitrides, silicides, etc.) [27, 31-35]

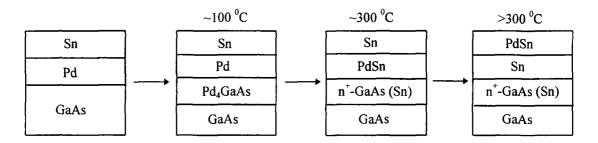

#### 1.3.1 Pd/Ge and Ge/Pd metallizations

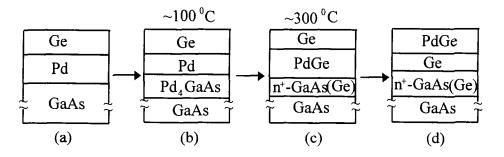

The Pd/Ge metallization scheme can provide Ohmic contacts with a low  $\rho_c$  similar to that obtained in AuGeNi contact systems Furnace annealing at 325 °C for 30 min is usually used to form Pd/Ge Ohmic contacts [18] However, it is often desirable to use an annealing process with shorter duration. The Ohmic contact formation mechanism for the non-alloyed Pd/Ge or Ge/Pd contact can be explained by a solid-phase regrowth mechanism [19,36]. The regrowth process begins with a limited low-temperature (~100 °C) reaction between the Pd and GaAs substrate to produce an intermediate Pd<sub>4</sub>GaAs phase (Figs 1 5(a) and 1 5(b)). A subsequent reaction at a high temperature (~300 °C) between the Ge overlayer and the intermediate Pd<sub>4</sub>GaAs phase results in the decomposition of the Pd<sub>4</sub>GaAs phase and the epitaxial regrowth of a Ge-doped n<sup>+</sup>-GaAs surface layer (Fig 1 5(c)). The excess Ge is then transported across the PdGe layer and epitaxially grows on the GaAs substrate (Fig 1 5(d)).

Fig 1 5 Shematic diagram of the regrowth mechanism using the Pd/Ge system [20]

Since Ge creates an n<sup>+</sup> doping on the GaAs surface upon annealing and Pd can decompose Ga and As oxides, Pd/Ge or Ge/Pd metallization systems have been extensively investigated on n-GaAs as possible Ohmic contacts [18, 20, 22, 31, 32, 37-49] There are additional but less notable advantages such as a lower barrier height for Ge/GaAs heterojunctions (~0 5 eV), compared to Pd/n-GaAs junctions where the Fermi level is generally pinned at ~0 8 eV In general, research has concluded that for a doping level in the low 10<sup>18</sup> cm<sup>-3</sup> range and a heat treatment of 325-375 °C up to 30 mm, a solid-phase reaction takes place producing contacts with  $\rho_c \sim 10^{-6} \Omega \cdot cm^2$  RTA or

RTP was reported to form good Ge/Pd and Pd/Ge contacts, having better surface morphology, better edge definition, lower  $\rho_c$ , high reliability for aging and exhibiting a shallow (non-spiking) nature [22, 37, 38].

Since Ge and Pd form compounds at low temperatures, the Pd/Ge or Ge/Pd contacts also exhibit  $\rho_c \sim 10^{-6} \Omega \cdot cm^2$  for doping concentrations of  $\sim 10^{18}$  cm<sup>-3</sup> [18, 40, 41, 44, 50]. The addition of a Au overlayer reduces sheet resistance of the metallization and facilitates Au wire bonding [51]. An optimum Ge/Pd metallization thickness with excess Ge (Pd~500Å, Ge~1265Å) can result in better  $\rho_c$  [18]. The same author found an increase in  $\rho_c$ , about one order of magnitude when the contacts were treated at 400 °C for 5 h. Scanned electron beam (SEB) annealing contacts [23, 52] gave better results than those of furnace annealing.

A number of fabrication techniques have been reported for improving the thermal stability of Ohmic contacts to GaAs. These approaches invariably depend on the use of a suitable Au diffusion barrier such as TiN [33], TiW [27], WSi [34], WN [35] and Pd [23]. Thermal stability and long-term stability of Pd/Ge Ohmic contacts have been studied by many authors [23, 31, 32, 38, 44, 51]. Ti/Pt/Au [31, 32], WN/Au [31], Ti/Pd/Au [53] and Ti/Au [21] overlayers improve the thermal stability of the Pd/Ge metallization. The Ge/Pd contact [44] was found to be stable at 300 °C for at least 50 h. An interdiffusion degradation model of this contact [44] was also proposed. Long-term stability was investigated by annealing the Pd/Ge/Au and Ge/Pd/Au contacts at 180 °C for 280 h [51]. No change in contact resistance or surface morphology was observed. The SEB annealed Au/Pd/Ge Ohmic contact exhibited good thermal stability after 25 h of aging at 500 °C [23]. Tsuchimoto et al. [38] investigated the long-term stability of Pd/Ge contacts and observed an increase in  $\rho_c$  from 1x10<sup>-5</sup> to 1.2x10<sup>-5</sup>  $\Omega$ cm<sup>2</sup> at 300 °C after 1000 h. This degradation is equivalent to a 10% deterioration in 109 years at 70 °C. Another model for the aforementioned degradation was also proposed [42].

The presence of Ni in Au/Pd/Ge contacts results in a reduction in the  $\rho_c$  and good surface morphology [23, 52]. This is because Ni by itself forms some Ni-Ge intermetallics and is known to enhance Ge diffusion into GaAs [54]. In addition, Ni prevents any interaction between Pd and Ge thereby enabling the Pd layer to effectively act as a Au diffusion barrier. The effectiveness of polyimide and rf sputtered SiO<sub>2</sub> passivation layers on the stability of a Au/Pd/Ni/Ge Ohmic contact [52] shows that both types of passivation provide good thermal stability. The operating life of this Ohmic contact for an eightfold increase in  $\rho_c$  is in excess of 100 000 h at room temperature (300 K) High-temperature (800-900 °C) RTA is used to form Ge/Pd/W/Au Ohmic contacts [55] which are compatible with ion implantation activation processes

#### 1.3.2 Pd/Ge/Ti/Pt metallizations

Pd/Ge/T1/Pt appears to be an excellent candidate as an Ohmic contact for both n- and p-GaAs [56, 57] Contact resistivities in the range of mid  $10^{-7} \ \Omega$ -cm<sup>2</sup> are obtained for both n- and p-GaAs using RTA. The T1 was added to the Pd/Ge contact primarily to promote the adhesion of the Pt to the contact and act as a diffusion barrier for the Pt. The Pt layer was protected from the Pd and Ge layers so that it would not participate in the contact forming reactions and would therefore retain its smooth morphology. Thermal stability of the contacts has also been studied [56, 57]. The contact is stable at 300 °C for 20 h, but at 400 °C it is stable for only about 35 s.

#### 1.3.3 Pd/AuGe/Ag/Au metallizations

Shallow Ohmic contacts have been developed using Pd/AuGe/Ag/Au metallizations [58,59] The structure offers low resistivity ( $\rho_c \sim 2x10^{-6} \ \Omega - cm^2$ ) Ohmic contacts with good adherence to the substrate in the temperature range from 400 to 500 °C The limited metal-GaAs reaction and the uniform interface morphology make the structure very attractive in large-scale integrated circuits The same metallization can be used for Al<sub>x</sub>Ga<sub>1-x</sub>As [58] which is very important for light-emitting diodes, laser diodes and other heterostructures

#### 1.3.4 Pd/Si metallizations

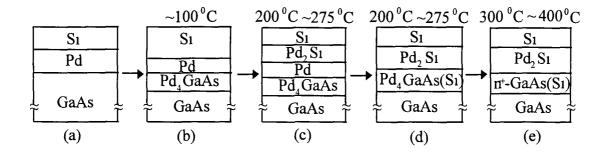

This metallization system is in many ways similar to Pd/Ge, including a low  $\rho_c \sim 10^{-6}$   $\Omega$ -cm<sup>2</sup> for similar doping levels if the Si/Pd ratio is equal to or greater than 0.65 [19] The Ohmic contact formation mechanism is described by many authors [2,7,8,19,40,44] The regrowth mechanism can be briefly summarized as shown in Fig 1.6 With a layer structure of Si/Pd/GaAs (Fig 1.6(a)), the regrowth mechanism begins with a low-temperature (~100 °C) reaction between a Pd layer and GaAs to form a stable Pd<sub>x</sub>GaAs (x~4) ternary compound (Fig 1.6(b)) The reaction

$$xPd + GaAs \rightarrow Pd_xGaAs \tag{16}$$

starts at the Pd/GaAs interface and at higher temperatures (about 200-275  $^{\circ}$ C) the reaction

$$Si + 2Pd \rightarrow Pd_2Si$$

(17)

starts at the SI/Pd interface (Fig 1 6(c)) Since  $Pd_xGaAs$  and  $Pd_2Si$  have almost identical crystal structures, the ternary compound is loaded with Si via diffusion of Si atoms (Fig 1 6(d)) When  $Pd_xGaAs$  and  $Pd_2Si$  meet, the thermal stability of  $Pd_2Si$  then drives the reaction

$$2Si + Pd_4GaAs \rightarrow 2Pd_2Si + GaAs \tag{18}$$

to the right in the presence of excess S1 at the subsequent higher temperatures ( $\geq 300 \ ^{\circ}$ C) This reaction results in the epitaxial regrowth of a thin GaAs layer as a product of the above reaction on the GaAs substrate [36] During the regrowth process, S1 atoms incorporated in the Pd<sub>4</sub>GaAs layer are carried along into the GaAs lattice in this process In this manner, the regrowth layer 1s doped with S1 atoms Equation (1.8), thus, 1s modified to be

$$2S\iota + Pd_4GaAs(S\iota) \rightarrow 2Pd_2S\iota + GaAs(S\iota) \tag{19}$$

where  $Pd_4GaAs(S_1)$  and  $GaAs(S_1)$  signify the doping of S<sub>1</sub> in these layers (Fig 1 6(e)) The thickness of this regrown layer is about 100Å In order for this regrown layer to be strongly n-type ( $\geq 2x10^{19}$  cm<sup>-3</sup>), S<sub>1</sub> atoms must preferentially occupy Ga vacant sites

Fig 1 6 Schematic diagram of the regrowth mechanism using the Pd/Si system [40]

In terms of this regrowth mechanism, the significance of excess S1 is evident Significant interaction between Pd<sub>2</sub>S1 and GaAs was observed at temperatures above 400 °C for the samples without excess S1 [60] However, the presence of excess S1 tends to drive eqn (1 9) to the right hand side, thus leading to Ohmic behaviour as well as forming a stable contact by preventing the Pd<sub>2</sub>S1 layer from reacting with GaAs The major difference between the S1/Pd/GaAs and Ge/Pd/GaAs systems is that epitaxial Ge is in contact with GaAs in the Ge/Pd/GaAs system, whereas Pd<sub>2</sub>S1 is in contact with GaAs in the S1/Pd/GaAs system However, both systems can result in Ohmic contact behaviour on n-GaAs with  $\rho_c$  in the range of 10<sup>-6</sup>  $\Omega$ -cm<sup>2</sup> on 1x10<sup>18</sup> cm<sup>-3</sup> n-GaAs From this fact, it is clear that the epitaxial Ge (or a possible low barrier height at the Ge-GaAs heterojunction) is not essential for the Ohmic behaviour, but it may be responsible for reducing the contact resistance

The Pd/S1 contact 1s stable at 300 °C for at least 50 h [44] The final layer sequence of S1/Pd/GaAs system 1s S1/Pd<sub>2</sub>S1/GaAs The thermal stability of this system 1s related to the stability of the Pd<sub>2</sub>S1/GaAs interface The importance of excess S1 in the Pd/S1 metallization 1s also reported [44] Excess S1 is needed to form the n<sup>+</sup> layer for the contact to become Ohmic Excess S1 also stabilizes the Pd<sub>2</sub>S1/GaAs interface The excess S1 may also stop the Ga and As out-diffusion because S1 has been shown to be a good annealing cap for implanted GaAs [61]

#### 1.3.5 Pd/In metallizations

The mam motivation for considering In-based metallization is the resultant formation of the small band gap material InGaAs on GaAs which can improve  $\rho_c$  However, the reaction between In and GaAs without surface oxides starts above the melting point of In (156 °C), hence, formation of the liquid phase and possible oxides may lead to poor interface and surface morphologies Palladium forms several refractory compounds with Indium, such as InPd, In<sub>3</sub>Pd, and In<sub>3</sub>Pd<sub>2</sub>, whose melting points lie between 700 °C and 1300 °C [62,63] Thus the thermal stability and morphology of Pd/In metallizations are improved Moreover, palladium deposited on GaAs increases the out-diffusion of gallium when heated, which facilitates the in-diffusion of doping species like Zn or Ge The same behaviour is expected for indium [47,63,64]

Ohmic contacts to n-GaAs based on Pd/In metallizations are reported by many authors [50, 65-69] The Ohmic contact formation mechanism of Pd/In metallization starts at low temperatute (~100 °C) At this temperature, a limited reaction occurs between Pd and GaAs to form Pd<sub>4</sub>GaAs and between Pd and In to form PdIn<sub>3</sub> During subsequent exposure to high temperatures (>550 °C), the high melting point phase, PdIn, nucleates The reaction continues at higher temperatures to form PdIn resulting in the extraction of Pd from the mterfacial layer of Pd<sub>4</sub>GaAs and the regrowth of In<sub>x</sub>Ga<sub>1-x</sub>As The sequence of solid-phase reactions are as follows

$$4Pd + GaAs \rightarrow Pd_4GaAs \tag{110}$$

(~100 °C, at the Pd/GaAs interface) and

$$3In + Pd \rightarrow PdIn_3 \tag{111}$$

(~100 °C, at the Pd/In interface). At higher temperatures (≥300 °C)

$$PdIn_{3} + Pd_{4}GaAs \rightarrow PdIn + In_{x}Ga_{1-x}As.$$

(1.12)

(The In fraction x is significantly greater than 0 only above ~550 °C). Equation (1.12) is not balanced since the exact stoichiometry of the ternary compound  $Pd_4GaAs$  and the growth  $In_xGa_{1-x}As$  layers are not known, although x is estimated to be ~0.4 for temperatures above 550 °C.

The effect of a thin Ge layer (2 nm) on Pd in Pd/In Ohmic contacts was investigated by Wang et al. [65]. Both contacts with and without Ge are stable in the low  $10^{-6} \Omega$ -cm<sup>2</sup> range at 400 °C for 48 h. Since the localized oxides prior to In deposition represent a problem, the use of a Pd, Ni, or Pt thin film to reduce the oxides has met with good results [66,67]. Formation of small band gap InAs on the GaAs was found in one In/Pt contact study [67]. A thermal study of the Pd/In contact [66] was carried out and the contact was seem to be relatively stable during anneals at 400 °C. A unique electroless method [63] which co-deposits Au-Pd-In and Pd-In onto an n-GaAs substrate has also lead to Ohmic contacts with  $\rho_c \sim 6x10^{-6} \Omega$ -cm<sup>2</sup> in this case only for Pd-In after annealing at 470 °C for 2 min. A  $\rho_c$  of the order of  $\sim 10^{-6} \Omega$ -cm<sup>2</sup> was obtained using both SEB and RTA processed Pd/In Ohmic contacts [68] with SEB annealed contacts exhibiting a superior surface morphology and thermal stability.

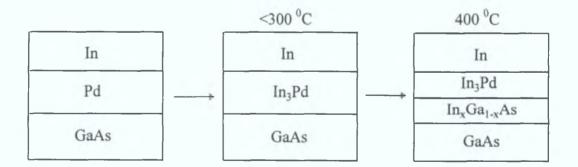

Fig.1.7.Schematic diagram of alloying sequence of Pd/In metallization to n-GaAs [70].

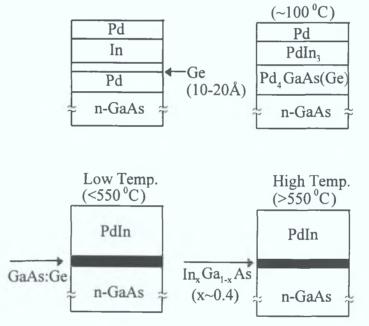

Very recently, Ma et al. [70] presented a growth mechanism for Pd/In contacts as depicted in Fig.1.7. Below 400 °C, it is proposed that In first reacts with Pd, developing a stable  $In_3Pd$  compound on the GaAs layer. This reaction continues until the Pd is entirely consumed. At 400 °C, solid-state diffusion occurs as excess In diffuses through the  $In_3Pd$ , forming a low resistive  $In_xGa_{1,x}As$  compound with GaAs. The In<sub>x</sub>Ga<sub>1-x</sub>As compound is believed to form an abrupt heterojunction with GaAs which restricts carrier transport more than the metal-In<sub>x</sub>Ga<sub>1-x</sub>As barrier and hence reduces the  $\rho_c$  values. Wang et al. [69] investigated Pd-In-Ge non-spiking Ohmic contacts to n-GaAs (10<sup>18</sup> cm<sup>-3</sup>). They observed that a layered structure of Pd/In/Pd/n-GaAs with 10-20Å of Ge embedded in the Pd layer adjacent to the GaAs can lead to a hybrid contact. When the Ohmic formation temperature was above 550 °C, a layer of In<sub>x</sub>Ga<sub>1-x</sub>As doped with Ge was formed between the GaAs structure and the metallization. When the annealing temperature was below 550 °C, a regrown layer of GaAs doped with Ge was formed at the PdIn/GaAs interface, giving rise to an n<sup>+</sup> surface layer and a tunneling junction as shown in Fig.1.8. The  $\rho_c$  of (2-3)x10<sup>-7</sup>  $\Omega$ -cm<sup>2</sup> for this contact structure is nearly independent of the contact area from 900 to 0.2  $\mu$ m<sup>2</sup>. This contact has been shown to be thermally stable up to a temperature as high as 600 °C.

Fig.1.8. Schematic diagram showing the solid-phase reaction of the Pd/In/Pd(Ge) contact [69].

#### 1.3.6 AuGe/Ni metallizations

Among Ni-based metallizations, eutectic AuGe/Ni is the most common contact material for n-GaAs [52, 71-80]. In this contact system, Ge serves to increase the surface doping, while Ni forms a barrier and a conductive NiAs compound. Two-stage annealing techniques can improve the overall performance of AuGeNi-based Ohmic contacts [71]. A pre-anneal can remove the inhomogeneity of the metal/GaAs interface [71]. Melting has been attributed to the  $\beta$ -AuGa phase modified by the other elements present. The addition of a Ti/Au cap also improves the topography of the annealed metallization but contact resistivities are poorer [71]. RTP (RTA) is also a popular means to improve Aubased contacts [78-80]. AuGe/Ni non-alloyed Ohmic contacts have been formed on heavily doped n-GaAs layers activated by  $SiO_xN_y$ -capped infrared rapid thermal annealing (RTA) [78]. A further reduction in  $\rho_c$  has been accomplished by lowtemperature (300 °C) alloying without melting the AuGe eutectic. Both conventional annealed and RTA AuGe/Ni contacts [80] have identical  $\rho_c$  values, but the interface reacted layer was wider for the first process.

Scanned electron beams (SEBs) have also been used for the alloying of AuGe/Ni metallization [52,77]. Capped alloyed AuGe/Ni contacts were found to have a higher resistance to degradation than uncapped alloyed AuGe/Ni contacts [52]. Capped AuGe/Ni contacts also exhibited longer operating life than uncapped contact structures for twofold, fourfold and eightfold increases in their  $\rho_c$  values. Cohen et al. [77] fabricated AuGe/Ni Ohmic contacts utilizing furnace and SEB annealing techniques. They observed that SEB-alloyed contacts exhibited less redistribution of contact constituents compared with furnace-alloyed contacts.

The importance of Ni to Ge ratio and of annealing cycle for the resistivity and morphology of AuGeNi Ohmic contacts to n-GaAs was investigated by Procop et al. [73]. The morphology of the contact layer at the minimum  $\rho_c$  was determined by the selected annealing cycle and by the Ni to Ge ratio. Goronkin et al. [72] used Ni/Ge/Au Ohmic contacts on GaAs and GaAs/AlGaAs. They did not observe any melting and lateral encroachment of the Ohmic metals alloyed at 460 °C. The use of Ni/Ge/Au Ohmic contacts on GaAs/AlGaAs with 460 °C, 8 min alloying cycles produced low-resistance contacts, no lateral encroachment, and sharp edge acuity. The AuGe/Ni contacts to n-GaAs [74] have mixed structure, composed of about 84% of n<sup>+</sup> n-contact and about 16% of the Schottky contact. The results obtained with AuGe/Ni and Ni/AuGe/Ni Ohmic contacts [75] indicate that the incorporation of Ge into GaAs occurs via solid-state diffusion and Ge distribution within the metallization layer differs in the two systems.

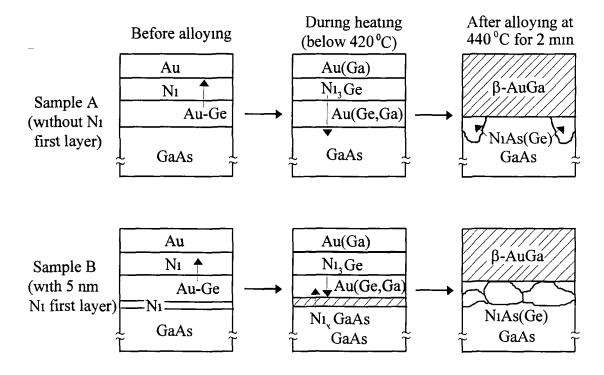

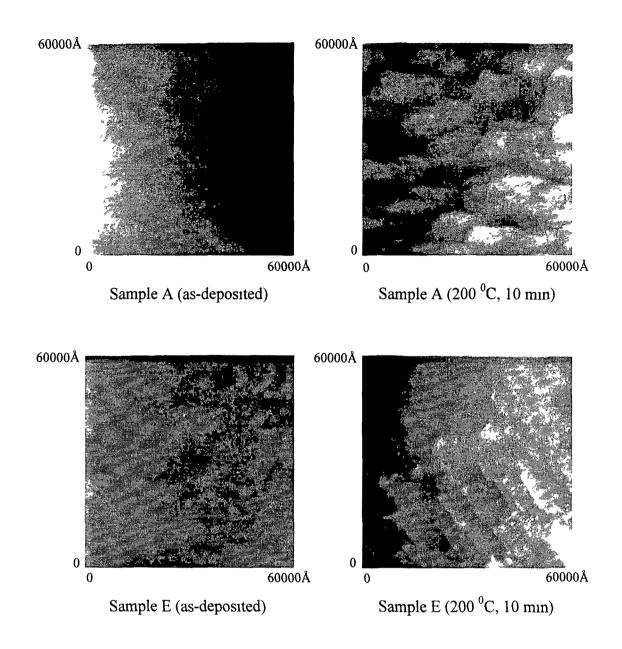

The effect of Ni as a first layer in the AuGeNi Ohmic contact was also reported [81]. The uniformity of the interface structure was greatly improved by the deposition of a 5 nm-thick Ni first layer due to its effects on kinetics of the alloying reaction (Fig.1.9). For sample A (without an initial Ni layer) Ni<sub>3</sub>Ge is formed between AuGe and Au at temperatures below 420 °C. When the annealing temperature is higher than 440 °C, a reaction between Au and GaAs is initiated, followed by the diffusion of Ni<sub>3</sub>Ge or the remaining Ni to the GaAs interface and the formation of a protruded NiAs(Ge) phase. The top layer is binary Au-Ga consisting of  $\beta$ -AuGa and  $\beta'$ -AuGa

phases with melting points of 375 °C and 347 °C, respectively The interface in this particular sample is nonplanar By contrast, in sample B (with an initial Ni first layer), the first layer Ni reacts with GaAs and forms Ni<sub>2</sub>GaAs or Ni<sub>3</sub>GaAs compounds at ~200 °C Above 400 °C, NiGa and NiAs develop An initial Ni layer clearly optimizes the alloying kinetics Alloying at a higher temperature, such as 600 °C, causes NiAs(Ge) grains to grow, resulting in dilution of Ge in the grains which then causes an increase in  $\rho_c$  The effect of the AuGe thickness in this metallization was also reported to have an impact on  $\rho_c$  [82] The same metallization has been utilized to find out the effect of AlAs mole fraction (x) on Al<sub>x</sub>Ga<sub>1-x</sub>As [43]

Fig 1.9 Schematic illustration of the sequence of alloying reactions for sample A and B, respectively [81]

A novel theoretical model for electron transport has been presented by Shenai [29] and extremely low  $\rho_c$  is reported using Ni/Ge/Au metallizations in Sn-doped n<sup>+</sup>-GaAs layers The Ni/Ge/Au contact revealed extensive GaAs consumption [50] The  $\rho_c$  of Au/AuGeNi contacts formed by rapid electron-beam annealing [83] is much lower than that formed by other techniques The contacts formed by this technique are found to be considerably stable with thermal aging Ion beam mixing has been utilized to produce morphologically improved Ohmic contacts to n-GaAs using Ge/Ni/Au metallization [84] The values of  $\rho_c$  depend both on ion dose and ion implant temperature.

Solid-state and alloyed AuGeN<sub>1</sub>/ZrB<sub>2</sub>/Au Ohmic contacts to n-In<sub>0 53</sub>Ga<sub>0 47</sub>As have been investigated for optoelectronic integrated circuits [85] ZrB<sub>2</sub> acted as a diffusion barrier in these contacts Non-alloyed, high-temperature stable Ge-N<sub>1</sub>-Au Ohmic contacts to n-GaAs with a LaB<sub>6</sub> diffusion barrier are also reported [86] The stable WSiN diffusion barrier (against gold) in Au/WSiN/(Au,Ge,N<sub>1</sub>) metallization [87] resulted in alloying depth less than 10 nm and values of  $\rho_c$  in mid 10<sup>-7</sup>  $\Omega$ -cm<sup>2</sup> range The influence of the internal layer (Au,Ge,N<sub>1</sub>) sequences on  $\rho_c$  is optimized and it is found that a combination of 25 nm Au, 5 nm N<sub>1</sub>, 20 nm Ge resulted in lower  $\rho_c$  values Reproducible and thermally stable non-alloyed Ohmic contacts are achieved by interposing a W<sub>60</sub>N<sub>40</sub> diffusion barrier between the Ni/Ge and the Au in Ni/Ge/Au system [35]

Both the contact uniformity and the resistivity of Ge/Au/Ni/Au Ohmic contacts may be greatly improved when a thin Ti/Au layer is deposited on the GaAs wafer backside prior to alloying [88] Ti/Au cap also improves the topography of Ni/AuGe/Ni/Au metallization [71] Very small area Ge/Au/Ni/Au contacts on GaAs have been reported [89] The proportions of Ni and AuGe in RTA AuGe/Ni/Au Ohmic contacts have also been optimized for low-temperature annealing [90] The annealing temperature for forming low  $\rho_c$  contacts to thin n<sup>+</sup> GaAs epilayers can be reduced from the standard 420 °C to 300-320 °C by varying the percentage of Ni in the contact Nonalloyed and alloyed low resistance Ni/Ge/Au/Ti/Au Ohmic contacts with good morphology for GaAs using a graded InGaAs cap layer have been developed [91] A low  $\rho_c$  of 4x10<sup>-8</sup>  $\Omega$ -cm<sup>2</sup> for a Ni/Au-Sn/Ni contact on n-GaInAs has also been obtained and compared with a Ni/Au-Ge/Ni contact [92] The Au-Ge contact shows better results than that of Au-Sn contact The contact resistivity and thermal stability of NiGe(Au)W Ohmic contacts were studied as a function of the Au layer thickness between 0 and 75 Å [93] A gold layer of ~60 Å produced a minimum contact resistance of 0 15  $\Omega$ -mm

#### 1.3.7 Multilayer Au/Ge/Au/Ni/Au metallizations

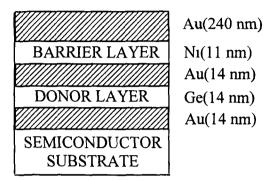

A five-layer Ohmic contact structure [41,94] (Fig 1 10) annealed at 425 <sup>o</sup>C for 60 s using a RTA has the following advantages compared to conventional approaches

- The donor/acceptor layer is separated from the barrier layer. This prevents undesired chemical reactions between the dopants and the barrier.

- Evaporation of eutectic alloys containing the dopants is not necessary Thus fractional distillation in the evaporation process is avoided and the resulting contacts show better reproducibility.

- The top gold layer is sufficiently thick to permit bonding A post evaporation of gold over the alloyed area is not needed

• Only three metal evaporation sources are required to create the five-layer structure Using this metallization contact resistivities in the  $10^{-7} \Omega$ -cm<sup>2</sup> range on both n- and p-type materials are obtained. This metallization technique is applicable for fabricating a wide variety of microwave and lightwave devices including switching diodes and field effect transistors.

Fig 1 10 Cross-sectional view of five-layer Au/Ge/Au/Ni/Au metallization [94]

#### 1.3.8 Ni/AuGe/Ag/Au metallizations

Silver (Ag) barrier Ohmic contacts are very important for GaAs based HEMT structures, such as AlGaAs/GaAs, AlGaAs/InGaAs and AlInAs/InGaAs It has been found that the Ohmic contact to GaAs based HEMTs requires high alloying temperature because the Ohmic metal has to penetrate the high band gap AlGaAs to reach the low band gap GaAs (or InGaAs) channel layer The conventional AuGe based Ohmic schemes (N1/AuGe/Au) can not withstand high temperatures above 450 °C The sample alloyed at high temperature, in order to diffuse Ohmic metal deeply into the HEMT layer, may exhibit very rough morphology and high contact resistivity due to the interdiffusion between the top Au layer and substrate [95] To allow higher temperature alloying, researchers have added different diffusion barriers such as silicon nitride, TiW and silver to this alloyed metal system Among them the Ag diffusion barrier is one of the most popular approaches and has been used in most of the reported state-of-the-art HEMTs [96-99] Low resistance ( $\leq 0.1 \Omega$ -mm) Ohmic contacts to the lower band gap material in both AlGaAs/GaAs and AlInAs/GaInAs MODFET structures can be fabricated using slightly different metallizations based on AuGeNi/Ag/Au [100] Ag in an AlGaAs/GaAs MODFET creates an Ag/Au alloy that reduces Ga outdiffusion from the semiconductor at temperatures up to ~570 °C In this way the GaAs stochiometry beneath the metallization is well maintained

#### 1.3.9 Au/Ni/NiSn metallizations

These metallizations are electroplated to n-GaAs. Kelly and Wrixon [101] developed low temperature electroplated alloyed Au/SnNi/Au Ohmic contacts in 1978. They observed that layer thicknesses of 4000Å Au, 5000Å SnNi and 3500Å Au gave minimum  $\rho_c$  after alloying at 300 °C for 3 min. Tin (Sn) in a shallow donor and is 0.006 eV from the edge of conduction band in GaAs. This results in a barrier with a high tunneling probability. A SnNi/Ni/Au Ohmic contact scheme to n-GaAs has also been proposed [102]. Inclusion of a Pt layer to reduce Au (acceptor) diffusion into the contact results in higher  $\rho_c$ . In Au/Ni/SnNi/GaAs junctions, Sn is expected to diffuse into Au-induced Ga vacancies thereby producing an excess electron concentration [103]. Ni is expected to provide good wetting so that Sn does not "ball up" during the alloying process. This process is similar to that occuring for Au/Ni-Ge/GaAs contacts with Sn taking the place of Ge. The addition of Sn to Au/Ni/n-GaAs system lowers  $\rho_c$ by at least two orders of magnitude [103].

Fig.1.11. Schematic illustration of alloying sequence of Ni/Ni-In/Ni/W metallizations to  $n^+$ -GaAs [105].

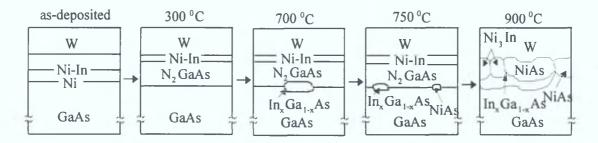

#### 1.3.10 NilnW metallizations

Rough surfaces and deteriorated contact edge profiles are observed in AuGeNi Ohmic contacts after annealing in forming gas at 440 °C for 2 min needed to form an Ohmic contact [81,104]. This limits extendability of this contact for use in submicron devices. NiInW Ohmic contacts have been developed which are very attractive for GaAs MESFETs because of improved morphology and thermal stability after Ohmic contact formation [105-109]. A typical example of the alloying sequence in the Ni/Ni-In/Ni/W metallization system [105] is illustrated in Fig.1.11. Initially, Ni from the upper layer diffuses into the Ni-In layer, forming a mixture of amorphous Ni-In and polycrystalline Ni phases. Under heat treatment at 300 °C for 30 min, an epitaxial Ni<sub>2</sub>GaAs phase forms at the Ni/GaAs interface while In partially intermixes with W and Ni<sub>2</sub>GaAs. At 700 °C, broad areas of In<sub>x</sub>Ga<sub>1-x</sub>As phase, with x=0.6, form at the Ni<sub>2</sub>GaAs/GaAs interface.

Heating to 750 °C produces additional NiAs precipitates under Ni<sub>2</sub>GaAs Further annealing at 900 °C leads to interfacial microstructures with large grains of regrown In<sub>x</sub>Ga<sub>1-x</sub>As with x=0 3 covering ~90% of the interface, the other 10% comprising of NiAs phase Ni<sub>3</sub>In forms on top of the In<sub>x</sub>Ga<sub>1-x</sub>As phase, while the W layer remains above the NiAs and Ni<sub>3</sub>In phases The W layer is usually inert and causes no electromigration problems in applications

A reduction in  $\rho_c$  for the NiInW metallizations has been obtained by adding donors to the contact material The Ni(Si)InW contacts with various Si concentrations were prepared and annealed at temperatures in the range of 750-900 °C for 2 s The lowest  $\rho_c$  value reached  $8x10^{-7} \Omega$ -cm<sup>2</sup> at 5% Si and an approximately 50% increase in the Si doping at the In<sub>x</sub>Ga<sub>1-x</sub>As (x=0 4) layer was believed to be achieved [106] Excellent stability in MESFETs with the NiInW Ohmic contacts was observed [105] No deterioration was observed at 400 °C for 180 h, 450 °C for 18 h and 500 °C for 2h The role of Ni on NiInW contacts was investigated [107] and it was found that Ni contributed to both a reduction of  $\rho_c$  and to improved thermal stability

The unreacted In after annealing is of great concern for thermal stability The unreacted In melts above 156 °C and the electrical properties of the contacts deteriorate To deposit In at the critical thickness is extremely difficult and is not practical. The addition of an element which forms high melting point  $(T_m)$  compounds with the unreacted In improves thermal stability after contact formation and is attractive from the view point of the fabrication process. Nickel is observed to form various Ni<sub>x</sub>In<sub>y</sub> compounds which have  $T_m$  higher than 900 °C. Ni<sub>3</sub>In ( $T_m$ =908 °C), NiAs ( $T_m$ =962 °C) and  $In_xGa_{1-x}As$  ( $T_m$ >900 °C) were observed in the Ni/Ni-In/Ni/W contacts and no evidence for the existence of unreacted In was obtained [107]. A very low  $\rho_c$  in the range of 10<sup>-7</sup>  $\Omega$ -cm<sup>2</sup> was obtained with NiInW metallizations after annealing under As overpressure [108]. Glas et al. [109] reported a Ni<sub>4</sub>(GaAs)<sub>3</sub> annealing product for the first time in NiInW contacts.

#### 1.3.11 Ni-based non-gold metallizations

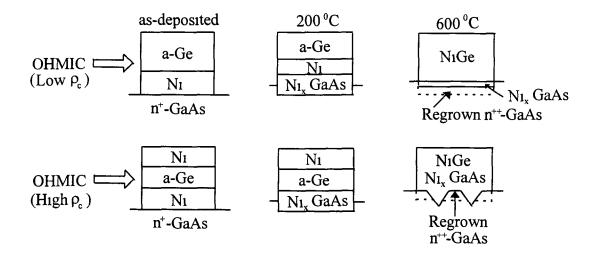

Thermal instability is of serious concern for AuGeN1 contacts utilized in very large scale integration (VLSI) devices As previously noted, this undesirable instability is due to formation of low melting point ( $T_m \sim 375$  °C)  $\beta$ -AuGa phases during contact annealing In order to improve the thermal instability of the AuGeN1 contacts, N1-based non-gold Ohmic contacts have been developed [110,111] The removal of Au from the AuGeN1 contacts is effective in improving the thermal instability after contact formation as seen in NiGe contacts [110] The thermal stability of NiGe contacts is

strongly influenced by the compounds that are formed at the interface between the NiGe and the GaAs after contact annealing The compound formation is controlled by the Ge concentration in the NiGe contacts and the annealing temperature A contact with 38% Ge prepared by annealing at 600 °C had a smooth surface and yielded good thermal stability at 400 °C, which was due to the formation of refractory NiGe compounds with a melting point (T<sub>m</sub>) of 850 °C

Fig 1 12 Schematic illustration of microstructural changes of NiGe Ohmic contacts, where a-Ge represents amorphous Ge [110]

A model for the electron transport mechanism through the GaAs/NiGe interface was also proposed by correlating the electrical properties and the microstructure. The interfacial microstructure of the NiGe Ohmic contact with low  $\rho_c$  is discussed by referring to Fig 1 12. At the initial stages of annealing at 200 °C, Ni reacts with GaAs to form a ternary Ni<sub>x</sub>GaAs compound by

$$xNi + GaAs \rightarrow Ni_{x}GaAs \tag{113}$$

The thickness of the N<sub>1<sub>x</sub></sub>GaAs layer increases with increasing the thickness of the N<sub>1</sub> layer deposited directly on the GaAs After annealing at temperatures above 300 °C, N<sub>1</sub> and Ge start to react, forming NiGe compounds When N<sub>1</sub> in the Ni<sub>x</sub>GaAs layer reacts with Ge, the thickness of the Ni<sub>x</sub>GaAs layer reduces, leaving the regrown GaAs layer as shown by a dashed line in the bottom of Fig 1 12 This reaction is expressed by

$$N_{i_x}GaAs + Ge \rightarrow N_iGe + GaAs \text{ (regrowth) [110]} (1.14)$$

When N<sub>1</sub> reacts with GaAs forming the N<sub>1<sub>x</sub></sub>GaAs layer, a small amount of Ge atoms diffuse to this ternary layer. Some of the Ge atoms remain in the regrown GaAs,

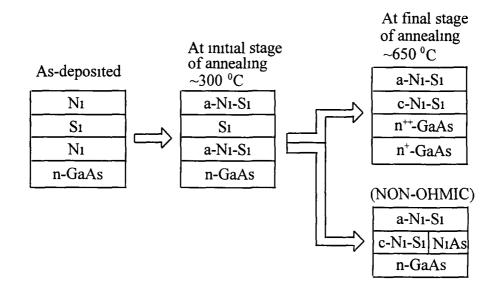

resulting in formation of a n<sup>++</sup>-GaAs layer The Ge-doped n<sup>++</sup>-GaAs layer enhances carrier tunneling probability and Schottky behaviour transforms to Ohmic behaviour, leading to a reduction in  $\rho_c$  Thermally stable NiSiW Ohmic contacts to n-GaAs have been developed [111] Ohmic behaviour was found to have dependencies on the Si concentration of the NiSiW contacts and the annealing condition Ohmic contacts with 40% Si, prepared by annealing at 650 °C, had smooth surfaces and yielded excellent thermal stability during subsequent annealing at 400 °C after contact formation The cross sections of the NiSiW Contacts are annealed at temperatures above 300 °C, the Si atoms diffuse into the crystalline Ni layers to form amorphous nickel-silicon layers (indicated by a-Ni-Si) At higher temperatures, the a-Ni-Si layer close to the GaAs surface transforms into the crystalline structure that is indicated by c-Ni-Si The best candidate for this crystalline structure as determined by XRD measurements and TEM observation is  $\delta$ -Ni<sub>1</sub>Si

Fig 1 13 Schematic illustration of microstructural changes of NiSiW Ohmic contacts, where a-Ni-Si and c-Ni-Si indicate amorphous-nickel-silicon and crystalline-nickel-silicon, respectively [111]

The N<sub>1x</sub>GaAs phases were not detected in the N<sub>1</sub>S<sub>1</sub>W Ohmic contacts even at the initial stages ( $\cong$ 300 °C) of RTA Therefore, the n<sup>++</sup>-GaAs layers for the N<sub>1</sub>S<sub>1</sub>W Ohmic contacts were believed to be formed by in-diffusing S<sub>1</sub> atoms The growth of the N<sub>1</sub>As compounds results in non-Ohmic behaviour, which is schematically shown in Fig 1 13 The formation of N<sub>1</sub>As is found to be suppressed by increasing the S<sub>1</sub> concentration and decreasing the annealing time using RTA The top W layer reduces the sheet resistance of the contact metal, improves the surface morphology of the N<sub>1</sub>S<sub>1</sub> contacts and also reduces the formation of N<sub>1</sub>As compounds

The kinetic effects of a layering sequence in Al-Ge-Ni Ohmic contact components on (001)GaAs were investigated by Lampert et al. [112]. Al-Ge-Ni metallizations have been successfully fabricated on both n- and p-type GaAs [113]. For n-type GaAs, the thickness of Ge deposited and the alloying time have a large influence over the degree of Ohmicity observed. The contact interface is extremely flat and uniform with a continuous single phase polycrystalline layer of Al<sub>3</sub>Ni adjacent to the semiconductor. Kalkur et al. [79] have analyzed the microstructure of Al-Ge-Ni RTA Ohmic contacts. Epitaxial GaAs/NiAl/GaAs heterostructures consisting of buried NiAl layers and GaAs overlayers that are monocrystalline and well aligned were also reported [114].

The Al-Sn-Ni [115] metallizations can produce Ohmic contacts to both n- and ptype GaAs and they have morphological characteristics superior to the Al-Ge-Ni contacts [79, 112, 113]. It is easy to pattern Al-Sn-Ni with the lift-off process and the surface remains remarkably smooth and planar after alloying. Contact resistivities in the range of  $10^{-4} \Omega$ -cm<sup>2</sup> are obtained for both n- and p-type GaAs [115]. The homogeneity of alloyed Ni-Sn Ohmic contacts to n-GaAs was investigated by Nikolaev et al. [116]. They reported intermediate phases NiAs, NiGa, and SnAs for the inhomogeneity of these contacts. Similarly, the role of Ge in NiAs/n-GaAs, NiAs/Ge/n-GaAs and Ge/NiAs/n-GaAs structures have been investigated [117].

#### 1.3.12 Au-Ge metallizations

Most commonly employed Ohmic contacts to n-type GaAs are based on the Au-12wt.%Ge eutectic alloy [118,119]. A minimum  $\rho_c$  of 9x10<sup>-7</sup>  $\Omega$ -cm<sup>2</sup> is obtained for an epilayer doping of 3x10<sup>17</sup> cm<sup>-3</sup> after annealing at 450 °C for 2½ min [119]. Melting of this eutectic alloy at a temperature of about 360 °C causes the localized dissolution of GaAs (presumably at pinholes in the native oxide). The higher solubility of Ga in the Au-Ge melt encourages the solidification of As-rich GaAs during cooling. Ge is thus incorporated preferentially on the Ga site in the precipitated GaAs, resulting in n-type GaAs and a tunneling Ohmic contact. Iliadis and Singer [119] observed that the role of Ge in Au-Ge metallization is not simply as dopant, but it is also the key element in initiating the melting. Barrier height reduction in Au-Ge metallization is investigated by Iliadis [118]. A massive reduction in barrier height [ $\phi_B$  (TFE)=0.34 eV] at a 300 °C heat treatment is due to the large fraction of Ge atoms that is not accommodated in Ga vacant sites and indiffuses along with the Au atoms.

Recently, non-alloyed Au-Ge Ohmic contacts to n-GaAs have gamed significant research interest [120-123] Low emperature, non-alloyed Au-Ge contact formation is a multi-step process [121] Ohmic behaviour was observed after 3 hrs of annealing at 320 °C and a Au<sub>2</sub>Ga phase was found at this stage Samples annealed with  $Si_3N_4$  cap layers to prevent As sublimation resulted in higher  $\rho_c$  values than uncapped samples [121] A novel model was presented for single crystal, non-alloyed epitaxial Au-Ge Ohmic contacts in Ref [120] According to this model, Au first comes in contact with the GaAs at points where the Ge layer is either very thin or nonexistent. It reacts with the GaAs to form AuGa phases which results in the formation of free As and/or vacancies in the GaAs lattice The Ge then rapidly mdiffuses substantially via Ga vacancies forming GeAs related phases Heavy Ge doping may then occur, leading to Ohmic contact formation Isothermal regrowth of doped, smooth and planar Ohmic contacts with low  $\rho_c$  using Au-Ge metallization has also been reported [122] This procedure is suitable for forming Ohmic contacts on shallow junction devices Extremely low resistance non-alloyed Au-Ge Ohmic contacts on  $\delta$ -doped GaAs have also been developed [123] and recently, properties of Au-Ge Ohmic contacts after the alloying process have been studied [124]

#### 1.3.13 Au/Te/Au metallizations

In Au/Te/Au metallizations, Te is used as the dopant to form an Ohmic contact to n-GaAs Te atoms become electrically active donors only when occupying As sites Therefore, As vacancies must be created during metallization Although reports on Au/Te/Au/GaAs contacts are scarce, several mechanisms have been invoked to explain their Ohmic behaviour In particular, Wuyts and co-workers attributed the formation of an Ohmic contact to the formation of either a metal/Te/Ga<sub>2</sub>Te<sub>3</sub>(Au)/GaAs or a metal/(Te)/Ga<sub>2</sub>Te<sub>3</sub>(As)/GaAs heterostructure [125-127]

Munder et al [128] investigated pulsed laser beam and furnace annealed Au/Te/Au metallizations For furnace annealed contacts the mechanism responsible for the Ohmic behaviour was dominated by the formation of a Ga<sub>2</sub>Te<sub>3</sub>, polycrystalline Te and a highly disordered GaAs layer [125,129] For laser annealed contacts electron tunneling through the potential barrier involving localized gap states was postulated for Ohmic behaviour The effects of an Al<sub>2</sub>O<sub>3</sub> cap on the structural and electrical properties of Au/Te/Au contacts on n-GaAs were also ameliorated [130,131] Contacts annealed without the capping layer became Ohmic after annealing at 420 °C for 3 mm with a  $\rho_c$  of ~1 6x10<sup>-4</sup>  $\Omega$ -cm<sup>2</sup> [130] In the uncapped system, the contact reaction is dominated by the Au-GaAs interaction, as indicated in TABLE I by the appearance of Au<sub>7</sub>Ga<sub>2</sub> phase and large arsenic losses

Annealing under a capping layer changes the kinetics of the contact reaction. For sealed GaAs/Au/Te/Au contacts, the losses of both Te and As are limited. Suppression of As vapourisation restrains the Au-GaAs reaction, while reduction of Te sublimation activates the Te-GaAs reaction. Ga<sub>2</sub>Te<sub>3</sub> and As<sub>2</sub>Te<sub>3</sub> are the main products of the interaction, apart from unreacted Au. Such interactions, however, do not lead to the formation of Ohmic contacts to n-GaAs. The results indicated do not support the heterojunction model of Ohmic contact, but rather testify in favour of the doping model.

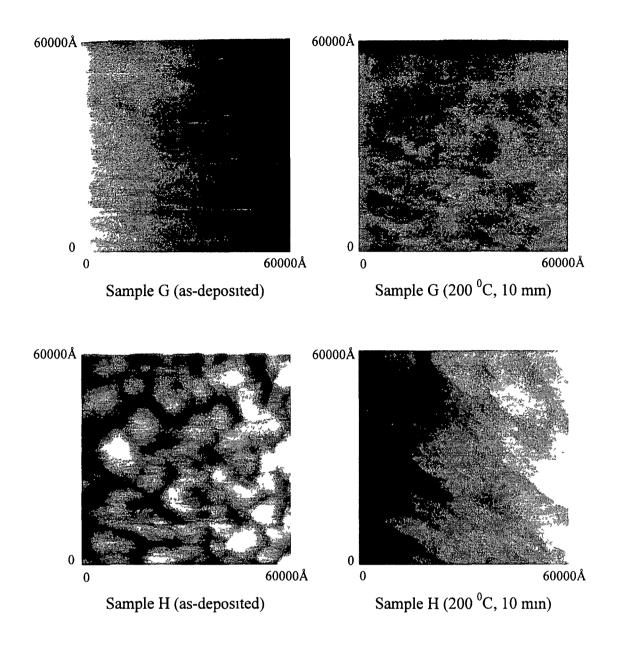

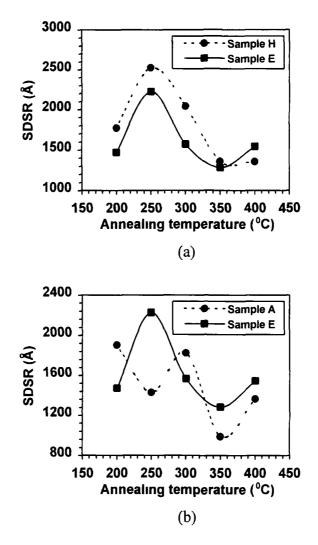

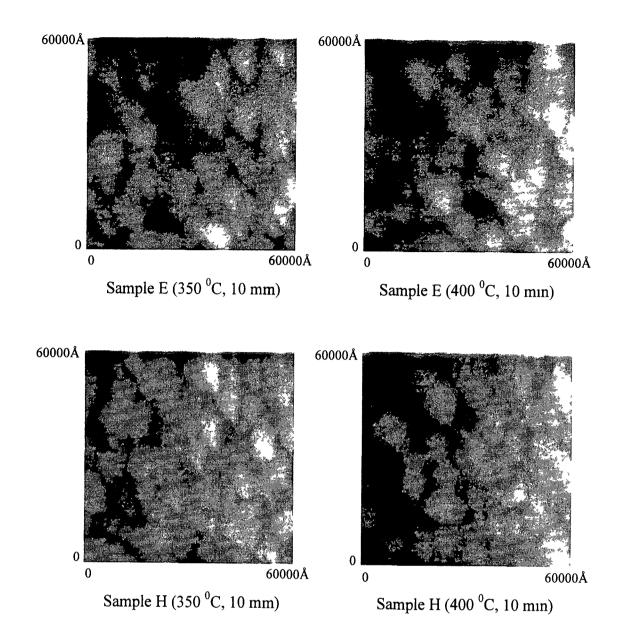

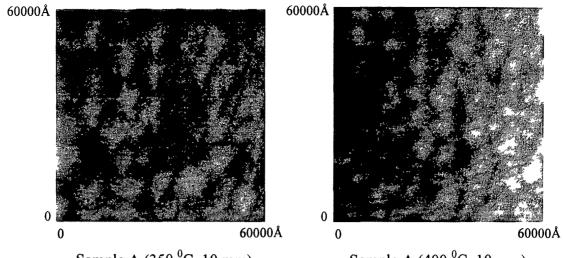

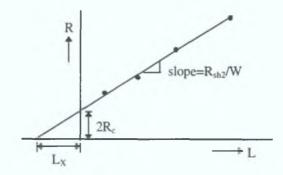

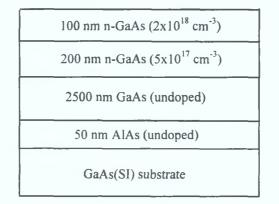

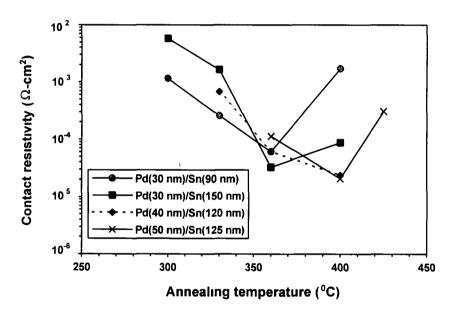

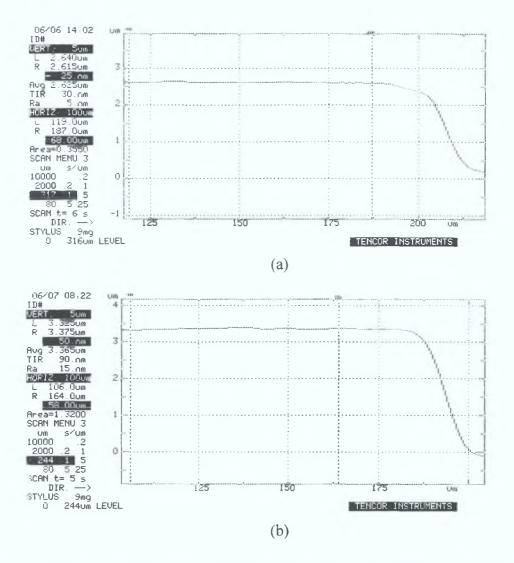

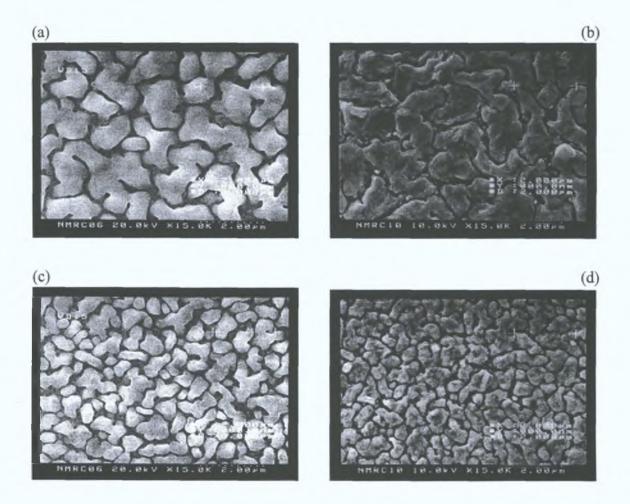

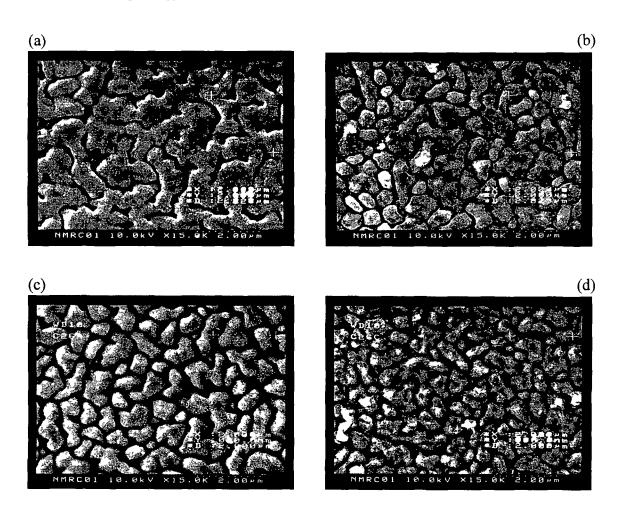

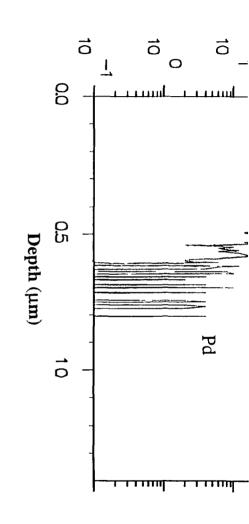

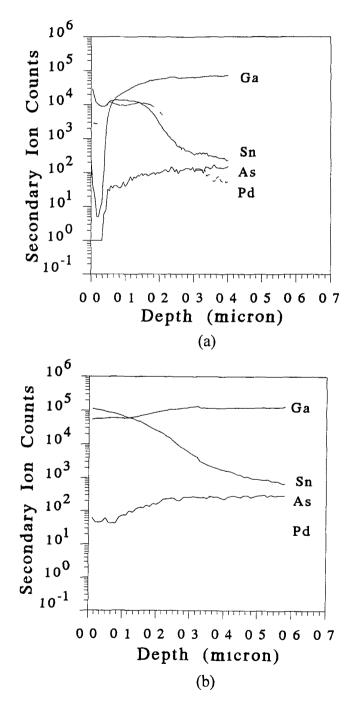

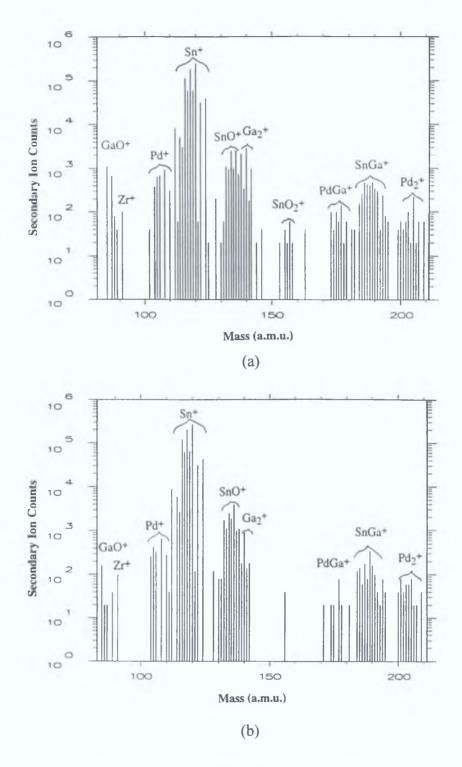

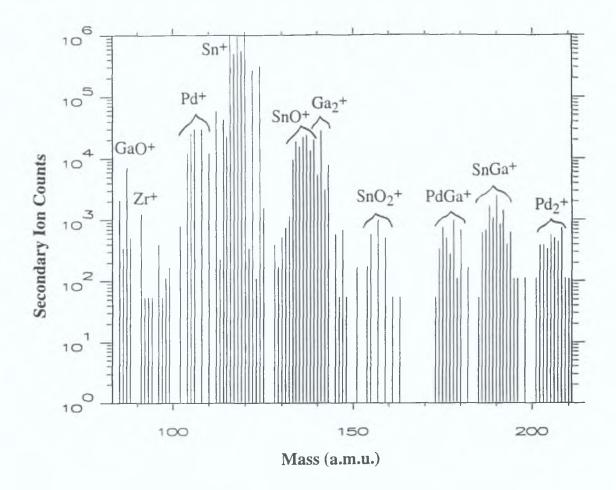

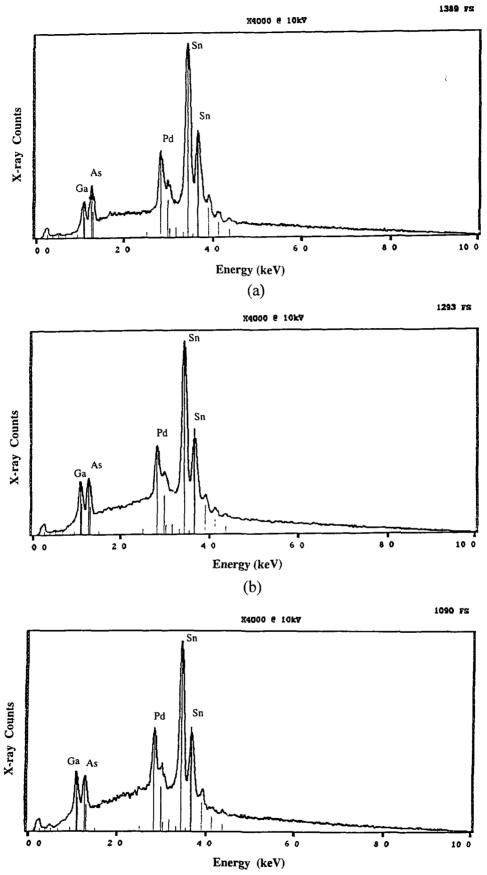

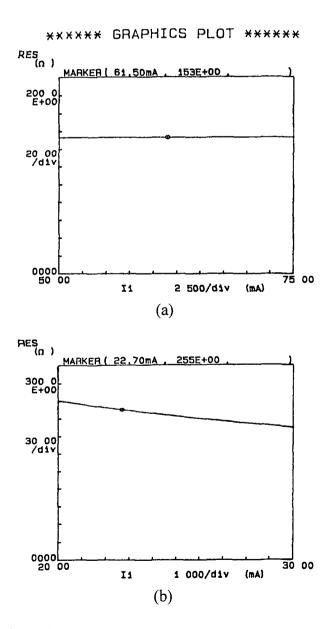

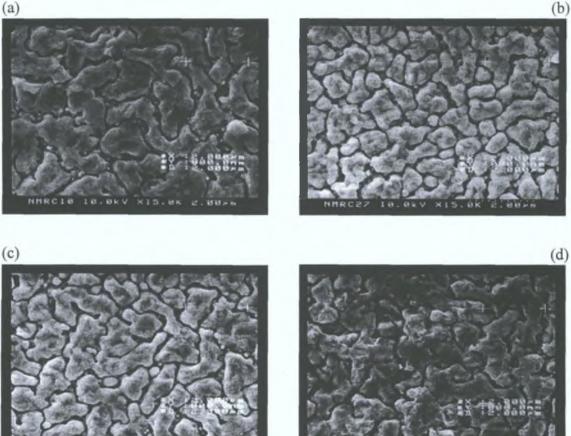

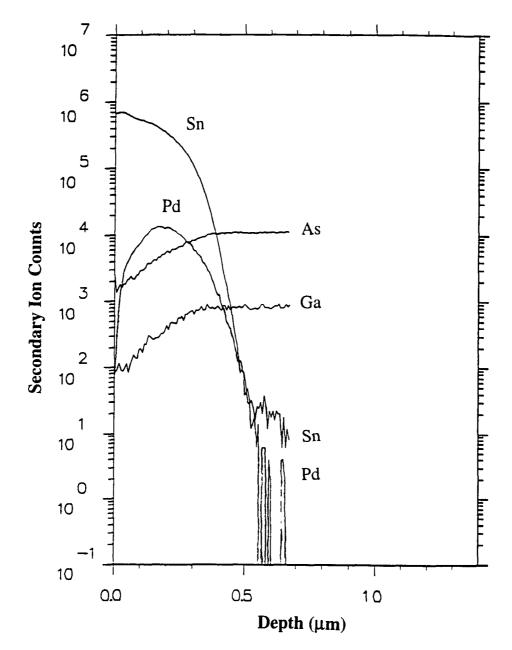

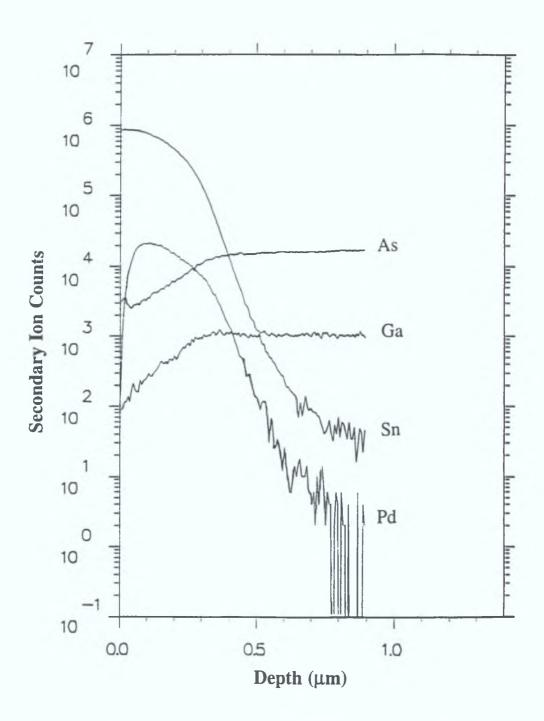

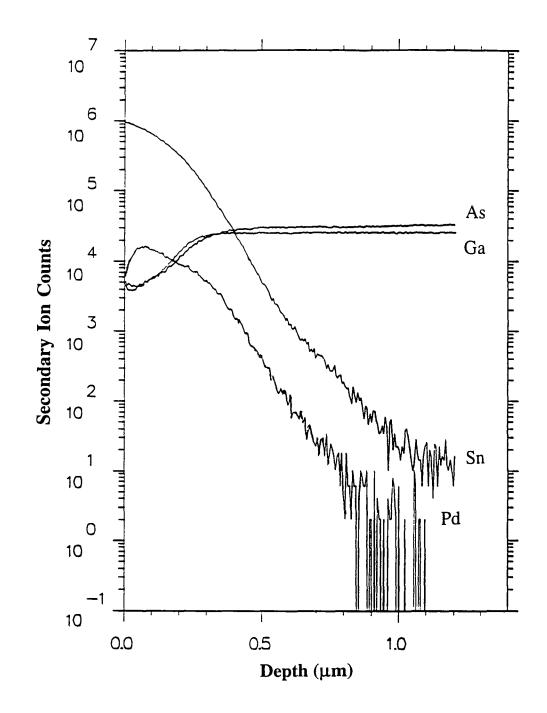

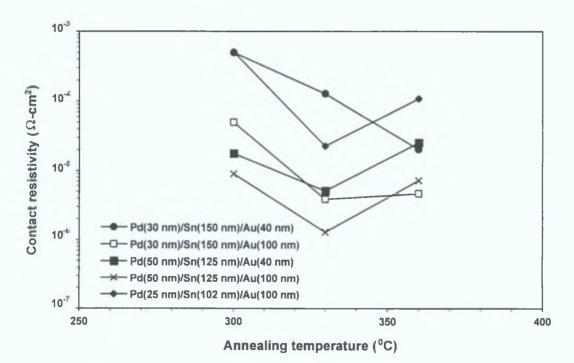

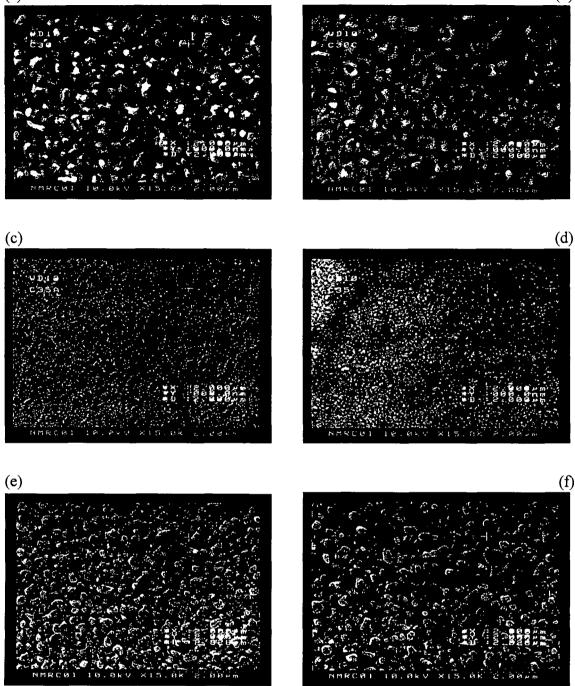

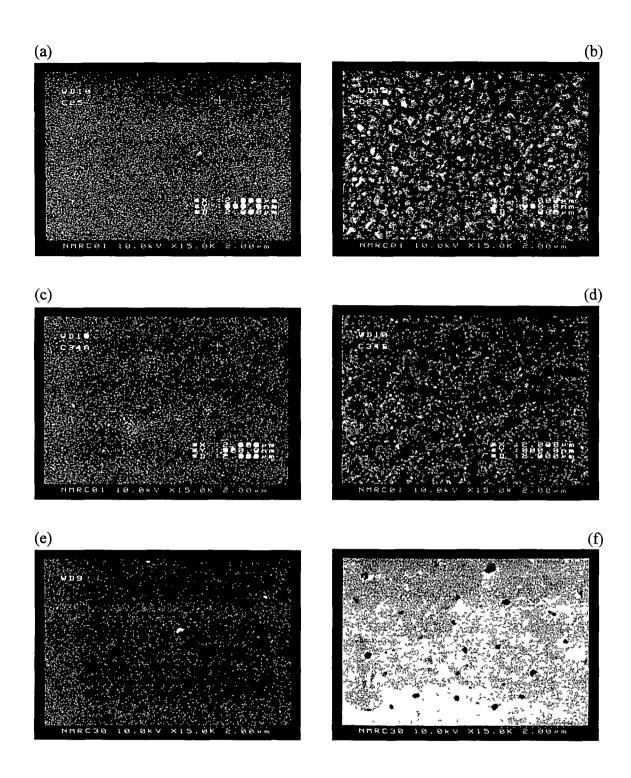

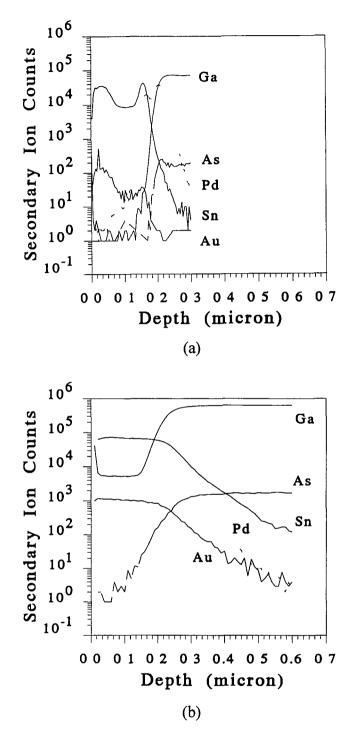

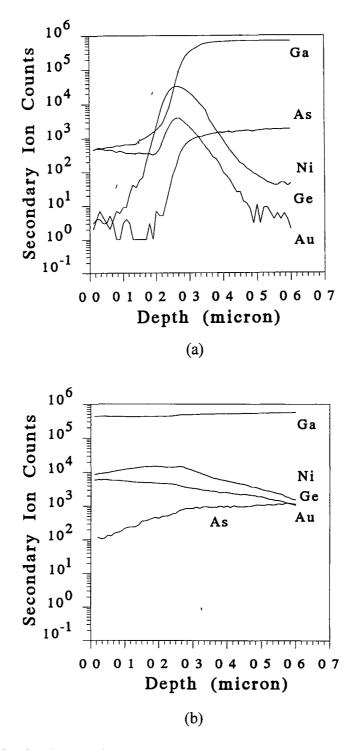

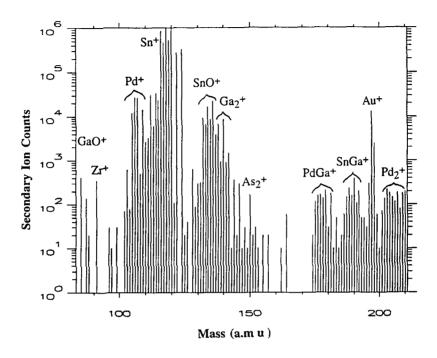

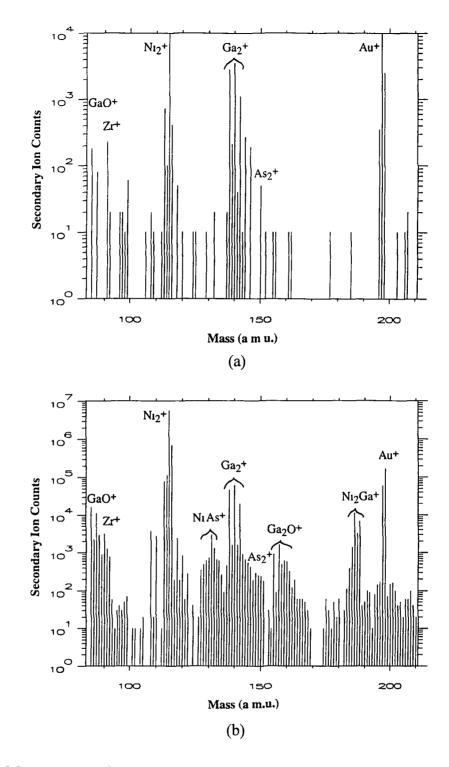

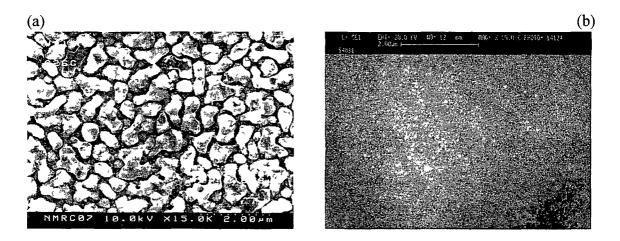

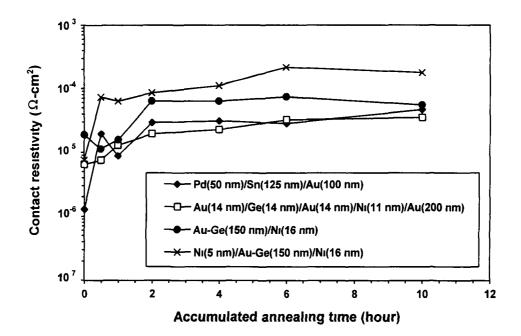

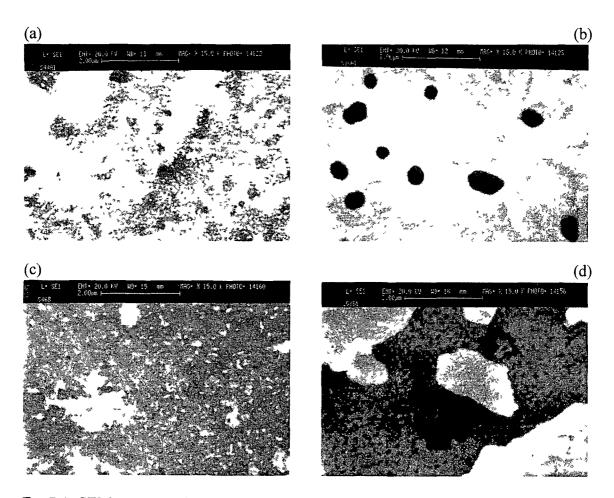

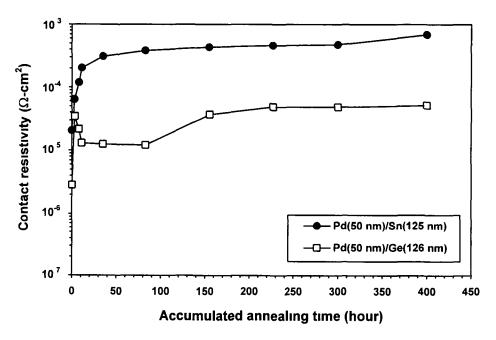

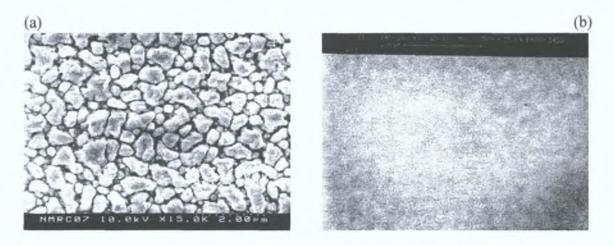

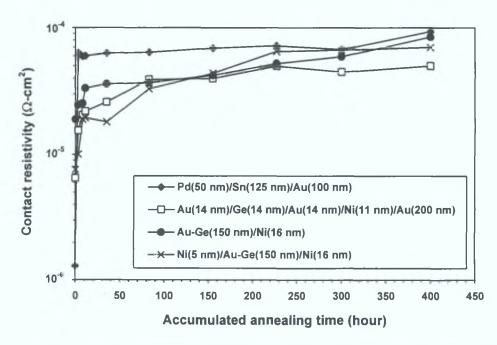

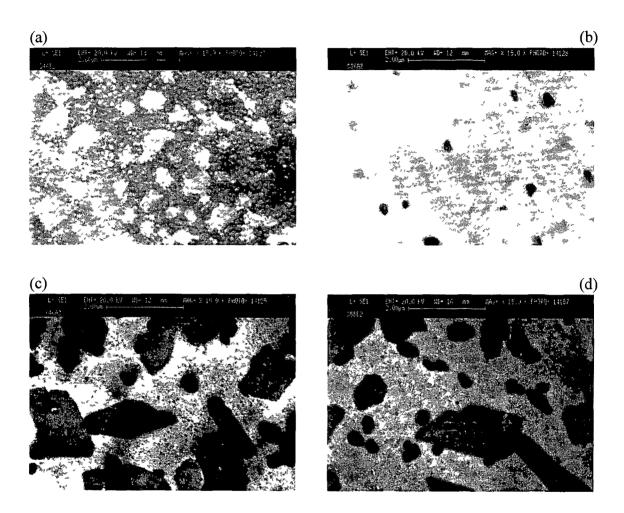

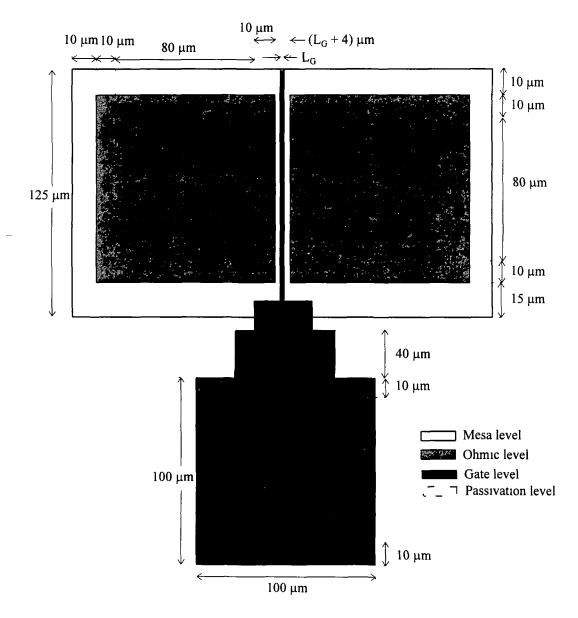

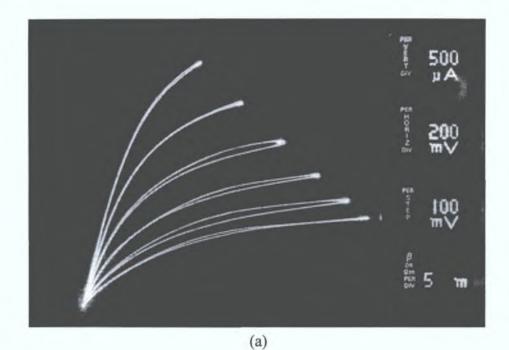

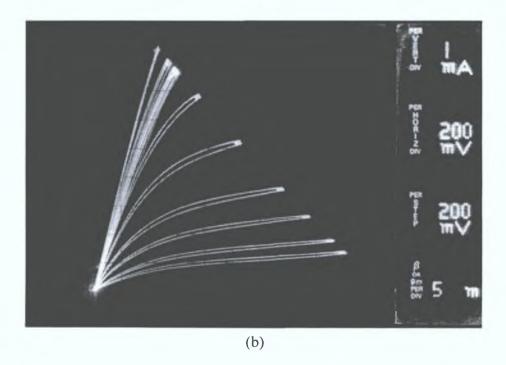

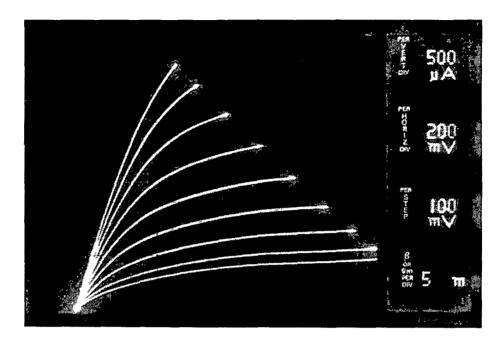

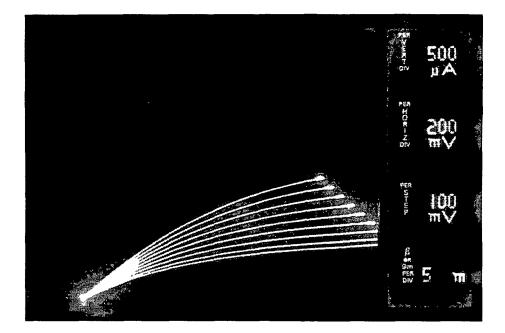

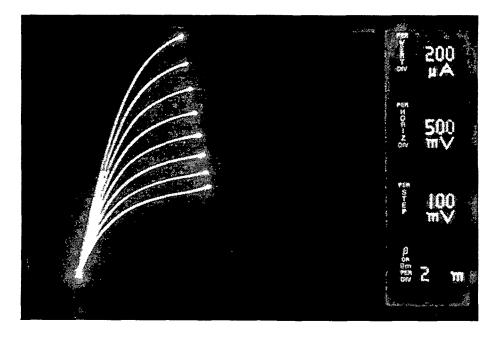

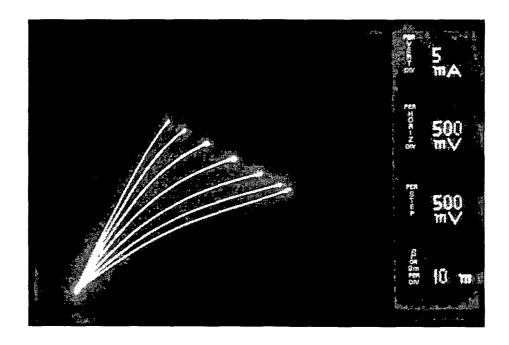

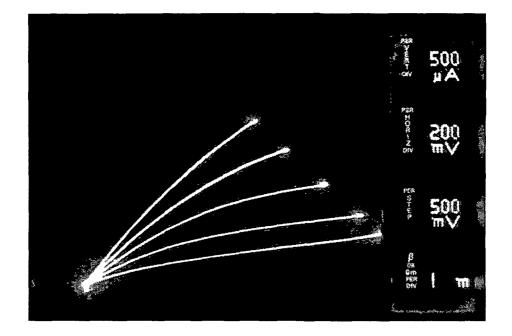

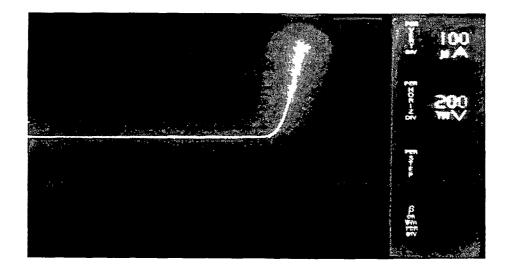

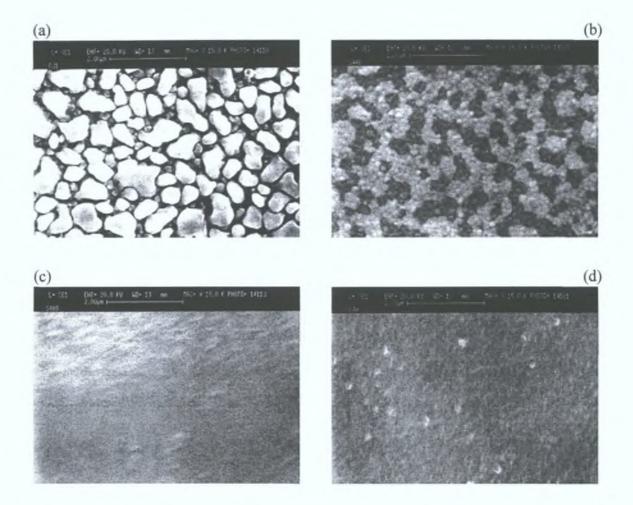

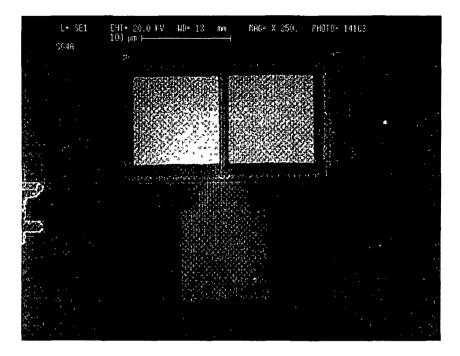

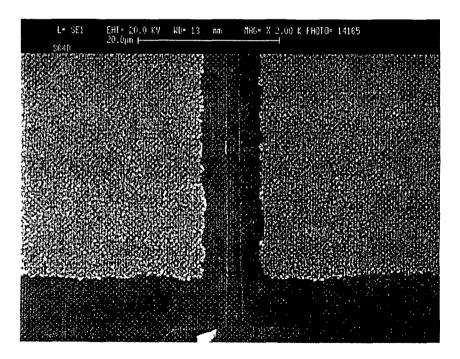

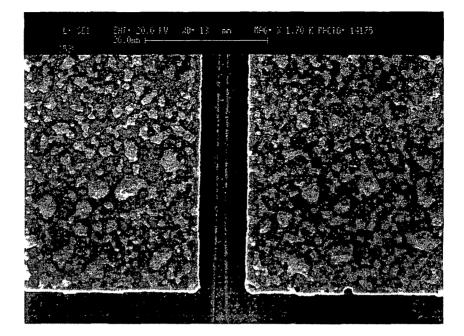

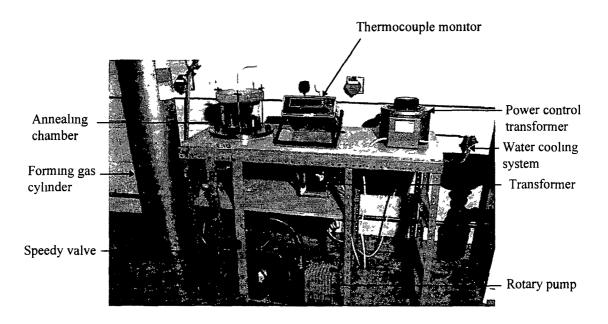

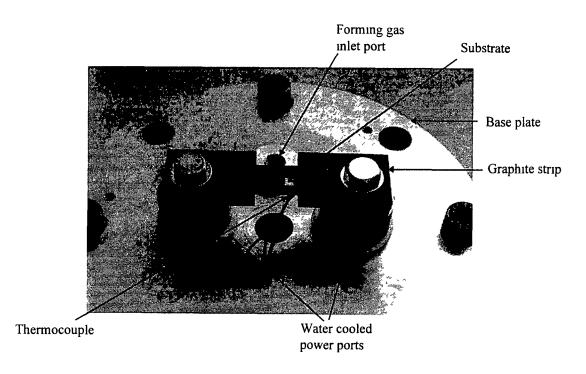

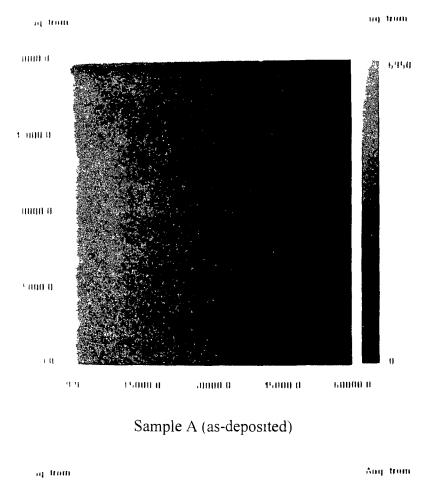

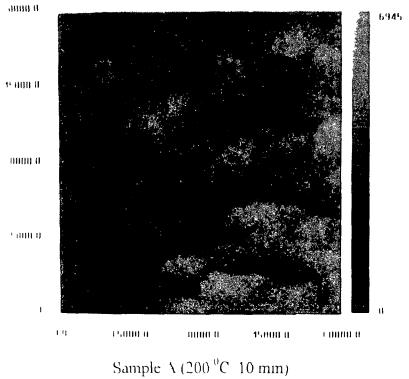

| Contact<br>material               |        |        | Phase<br>composition               | As loss                           | Te loss                 |