# Efficient Hardware Architecture for Scalar Multiplications on Elliptic Curves over Prime Field

Khalid Javeed

BEng, MEng

A Disertation submitted in fulfilment of the requirements for the award of Doctor of Philosophy (Ph.D.)

**DUBLIN CITY UNIVERSITY**

SCHOOL OF ELECTRONIC ENGINEERING

Supervisors: Dr. Xiaojun Wang and Dr. Mike Scott

September 2016

# **Declaration**

I hereby certify that this material, which I now submit for assessment on the programme of study leading to the award of Ph.D is entirely my own work, that I have exercised reasonable care to ensure that the work is original, and does not to the best of my knowledge breach any law of copyright, and has not been taken from the work of others save and to the extent that such work has been cited and acknowledged within the text of my work.

| Signed: ——           | <del></del> |

|----------------------|-------------|

| Candidate ID No: ——— |             |

| Date:——              |             |

## Acknowledgement

I would like to express my sincere gratitude to my supervisor Dr. Xiaojun Wang for his continuous support in technical and non-technical matters related to my Ph.D studies, research work and thesis writing. I am also very thankful to Dr. Mike Scott for helping in understanding elliptic curve cryptography.

I thank my all fellow lab mates for their help and support. Due to their company, my stay at Dublin City University was comfortable and enjoyable.

Last but not the least, I would like to pay my humble but full of emotion gratitude to my parents without their prayers and assistance this would not have been possible. I would also like to thank my entire family for providing me courage which I required most of the time during this work. Lastly, I am very thankful to my loving wife, my lovely daughter Meerab and son Abdul Hadi for their love, support and patience.

# Contents

| L1 | st of 1 | rigures |                                            | X   |

|----|---------|---------|--------------------------------------------|-----|

| Li | st of   | Tables  |                                            | xii |

| 1  | Intr    | oductio | on                                         | 1   |

|    | 1.1     | Thesis  | Motivation                                 | 1   |

|    | 1.2     | Thesis  | : Aim                                      | 3   |

|    | 1.3     | Thesis  | Contributions                              | 5   |

|    | 1.4     | Thesis  | Organization                               | 8   |

| 2  | Bac     | kgrour  | nd                                         | 9   |

|    | 2.1     | Symm    | etric-Key Cryptography                     | 9   |

|    | 2.2     | Public  | -Key Cryptography                          | 10  |

|    | 2.3     | Crypto  | ographic Key Sizes                         | 12  |

|    | 2.4     | Finite  | Field                                      | 14  |

|    |         | 2.4.1   | Groups                                     | 14  |

|    |         | 2.4.2   | Rings                                      | 14  |

|    |         | 2.4.3   | Finite Fields                              | 15  |

|    |         | 2.4.4   | Prime Field Arithmetic                     | 16  |

|    | 2.5     | Introd  | uction to Elliptic Curves                  | 17  |

|    |         | 2.5.1   | Elliptic Curve Scalar Multiplication       | 17  |

|    |         | 2.5.2   | Elliptic Curve Group Operations            | 18  |

|    |         | 2.5.3   | Order of an Elliptic Curve                 | 19  |

|    |         | 2.5.4   | EC Crypto Schemes Implementation Hierarchy | 20  |

|    |         | 2.5.5   | Diffie-Hellman Key Exchange                | 20  |

|    |         | 2.5.6   | Standard Projective Coordinates            | 23  |

|   |      | 2.5.7 Jacobian Projective Coordinates                          | 24 |

|---|------|----------------------------------------------------------------|----|

|   | 2.6  | Side Channel Attacks                                           | 25 |

|   | 2.7  | Related Work                                                   | 25 |

|   |      | 2.7.1 Hardware Architectures for EC Scalar Multiplication      | 26 |

|   |      | 2.7.1.1 EC Scalar Multipliers over Standard Prime Fields       | 27 |

|   |      | 2.7.1.2 EC Scalar Multipliers over General Prime Field         | 28 |

|   | 2.8  | FPGA Architecture                                              | 30 |

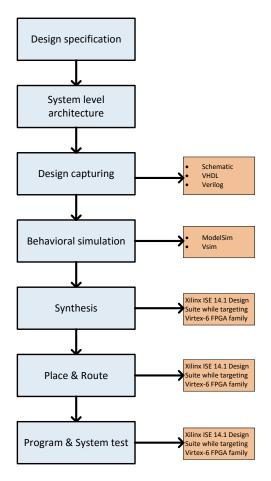

|   |      | 2.8.1 FPGA Implementation Design Flow                          | 32 |

|   | 2.9  | Conclusion                                                     | 34 |

| 3 | Har  | dware Architectures for Finite Field Arithmetic                | 35 |

| _ | 3.1  | Background and Related Work                                    | 36 |

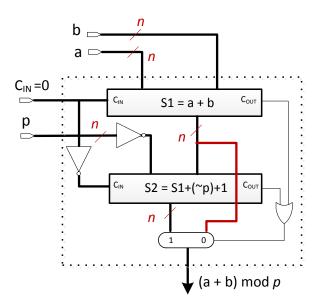

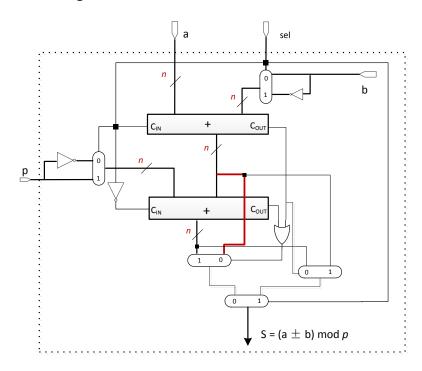

|   | 3.2  | Modular Addition/Subtraction                                   | 39 |

|   |      | 3.2.1 Modular Addition                                         | 39 |

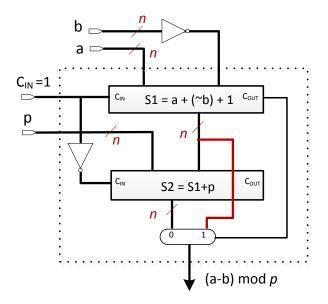

|   |      | 3.2.2 Modular Subtraction                                      | 40 |

|   | 3.3  | Modular Inversion/Division                                     | 41 |

|   |      | 3.3.1 Implementation Results                                   | 44 |

|   | 3.4  | Modular Multiplication                                         | 45 |

|   | 3.5  | Radix-4 BE Interleaved Multiplication                          | 47 |

|   |      | 3.5.1 Hardware Architecture                                    | 50 |

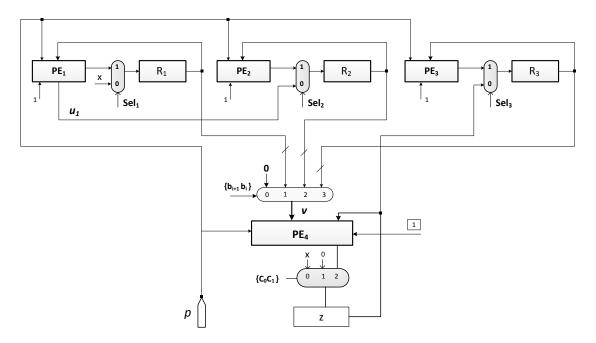

|   | 3.6  | Radix-8 BE Interleaved Multiplication                          | 52 |

|   |      | 3.6.1 Hardware Architecure                                     | 54 |

|   |      | 3.6.1.1 Phase A                                                | 54 |

|   |      | 3.6.1.2 Phase B                                                | 55 |

|   | 3.7  | Implementation and Results                                     | 57 |

|   | 3.8  | Conclusion                                                     | 60 |

| 4 | High | n Performance Parallel Modular Multipliers                     | 61 |

|   | 4.1  | Introduction                                                   | 62 |

|   | 4.2  | Motivation                                                     | 63 |

|   |      | 4.2.1 Montgomery Powering Ladder                               | 64 |

|   | 4.3  | Radix-4 Parallel Interleaved Multiplier (R4PIM)                | 65 |

|   |      | 4.3.1 Hardware Architecture                                    | 66 |

|   |      | 4.3.2 Phase A                                                  | 66 |

|   |      | 4.3.3 Phase B                                                  | 68 |

|   | 4.4  | Radix-4 Booth Encoded Parallel Interleaved Multiplier (R4BPIM) | 70 |

|   |      | 4.4.1 Hardware Architecture                                    | 71 |

|   |      | AAA Dhase A                                                    | 71 |

|   |      | 4.4.3 Phase B                                                  | 71  |

|---|------|----------------------------------------------------------------|-----|

|   | 4.5  | Radix-8 Booth Encoded Parallel Interleaved Multiplier (R8BPIM) | 73  |

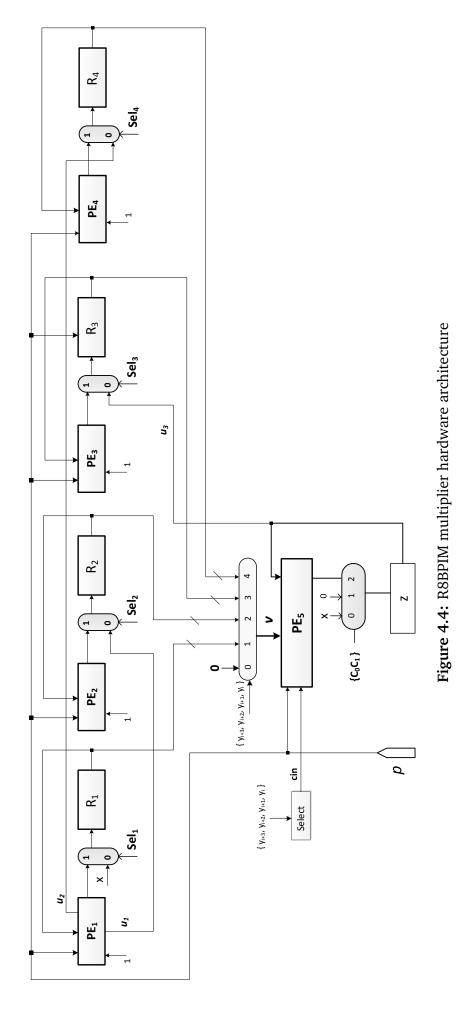

|   |      | 4.5.1 Hardware Architecture                                    | 74  |

|   | 4.6  | Platform Independent Performance Analysis                      | 78  |

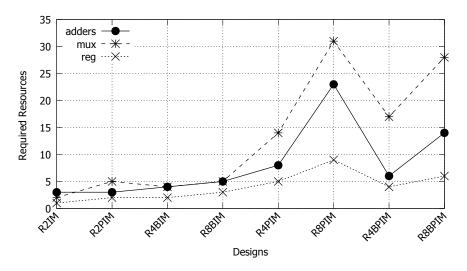

|   |      | 4.6.1 Resource Requirements                                    | 78  |

|   |      | 4.6.2 Critical Path and Latency                                | 79  |

|   | 4.7  | Implementation Results                                         | 80  |

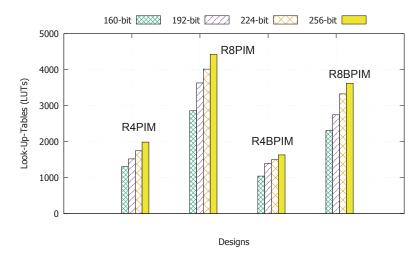

|   |      | 4.7.1 Area Results                                             | 81  |

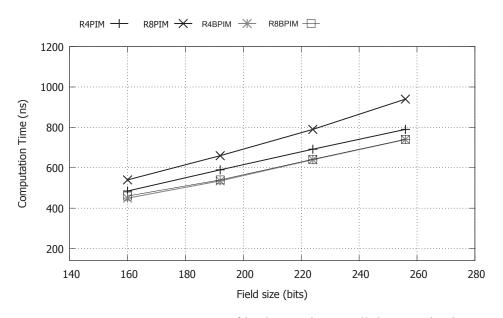

|   |      | 4.7.2 Execution Time Results                                   | 82  |

|   | 4.8  | Performance Evaluation and Analysis                            | 83  |

|   | 4.9  | Throughput and Area-Delay Product                              | 87  |

|   | 4.10 | Conclusion                                                     | 89  |

| 5 | EC S | Scalar Multiplier Architectures                                | 90  |

|   | 5.1  | Introduction And Related Work                                  | 91  |

|   | 5.2  | Elliptic curve scalar multiplication                           | 92  |

|   |      | 5.2.1 EC Point Operations Using Affine Coordinates             | 94  |

|   | 5.3  | EC Scalar Multiplier Architecture in Affine Coordinates        | 95  |

|   |      | 5.3.1 Latency                                                  | 98  |

|   |      | 5.3.2 Using double-and-add (DA) method                         | 98  |

|   |      | 5.3.3 Using double-and-always-add (DAA) method                 | 98  |

|   | 5.4  | Implementation Results                                         | 98  |

|   | 5.5  | EC Point Operations Using Projective Coordinates               | 99  |

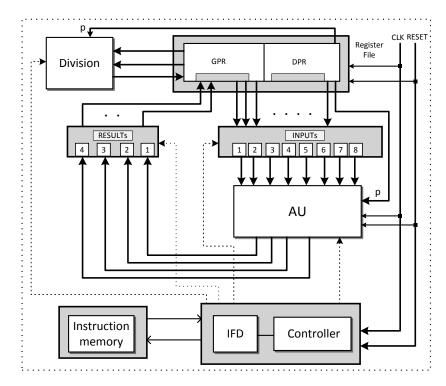

|   | 5.6  | EC Scalar Multiplier Architecture in Projective Coordinates    | 101 |

|   |      | 5.6.1 Arithmetic Unit                                          | 101 |

|   |      | 5.6.2 Scheduling of PD and PA Operations                       | 103 |

|   |      | 5.6.3 Overall Execution                                        | 109 |

|   |      | 5.6.4 Final Conversion                                         | 110 |

|   |      | 5.6.5 Latecny                                                  | 110 |

|   | 5.7  | Implementation and Results                                     | 111 |

|   |      | 5.7.1 Performance Evaluation                                   | 115 |

|   | 5.8  | Conclusion                                                     | 118 |

| 6 | Cor  | nclusion and Future Work                                       | 120 |

|   | 6.1  | Conclusion                                                     | 120 |

|   | 6.2  | Future Work                                                    | 122 |

| A   | App   | endix                                                                                           | <b>124</b> |

|-----|-------|-------------------------------------------------------------------------------------------------|------------|

|     | A.1   | Implementation results of EC scalar multiplier using modular multipliers presented in Chapter 4 | 124        |

| Bil | bliog | raphy                                                                                           | 129        |

# List of Acronyms

**AES** Advanced Encryption Standards

Add Addition

**ASIC** Application Specific Integrated Circuit

**ATB** Area-Time product per bit

**AU** Arithmetic Unit

**BE** Booth Encoding

**CLB** Configurable Logic Block

**DA** Double-and-Add

DAA Double-and-always-add

**DES** Digital Encryption Standards

**DLP** Discrete Logarithm Problem

**Div** Division

**DPA** Differential Power Analysis

**EC** Elliptic curve

**ECC** Elliptic curve Cryptography

**ECDH** Elliptic Curve Diffie-Hellman

**ECDSA** Elliptic Curve Digital Signature Algorithm

**ECDLP** Elliptic Curve Discrete Logarithm Problem

FPGA Field Programmable Gate Array

**Freq** Frequency

**IM** Interleaved Modular Multiplication

**Inv** Inversion

**LUT** Look-Up-Table

MM Modular Multiplication

MMM Montgomery Modular Multiplication

MPL Montgomery Powering Ladder

MR Montgomery Reduction

**Mul** Multiplication

**NAF** Non-Adjacent Form

**NIST** National Institute of Standards and Technology

**PA** Point Addition

PAU Parallel Arithmetic Unit

**PKC** Public Key Cryptography

PD Point Doubling

**PKI** Public Key Infrastructure

**RSA** Rivest Shamir Adleman

**R2IM** Radix-2 Interleaved Modular Multiplication

**R2PIM** Radix-2 Parallel Interleaved Modular Multiplication

**R4BIM** Radix-4 Booth Encoded Interleaved Modular Multiplication

**R8BIM** Radix-8 Booth Encoded Interleaved Modular Multiplication

**R4PIM** Radix-4 Parallel Interleaved Modular Multiplication

**R4BPIM** Radix-4 Booth Encoded Parallel Interleaved Modular Multiplication

**R8PIM** Radix-8 Parallel Interleaved Modular Multiplication

**R8BIM** Radix-8 Booth Encoded Parallel Interleaved Modular Multiplication

**SPA** Simple Power Analysis

## **Sub** Subtraction

TPAR Timing and Power Attacks Resistance

# List of Figures

| 1.1 | Performance evaluation metrics                     | 4  |

|-----|----------------------------------------------------|----|

| 2.1 | Symmetric-Key encryption/decryption                | 10 |

| 2.2 | Public-Key encryption/decryption                   | 11 |

| 2.3 | EC group operations                                | 18 |

| 2.4 | Diffie-Hellman key exchange scheme                 | 21 |

| 2.5 | EC based Diffie-Hellman key exchange scheme        | 22 |

| 2.6 | EC scalar multiplication in projective coordinates | 23 |

| 2.7 | A Generic FPGA Architecture                        | 30 |

| 2.8 | Design steps of FPGA implementation                | 32 |

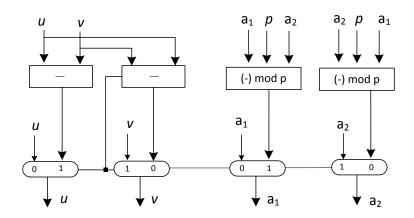

| 3.1 | Modular addition architecture                      | 40 |

| 3.2 | Modular subtraction architecture                   | 41 |

| 3.3 | Modular addition/subtraction architecture          | 41 |

| 3.4 | Overall steps in EEA algorithm                     | 44 |

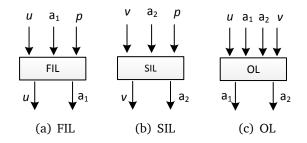

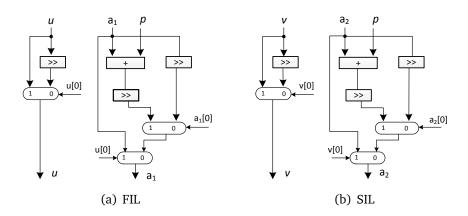

| 3.5 | FIL and SIL internal architecture                  | 44 |

| 3.6 | OL internal architecture                           | 44 |

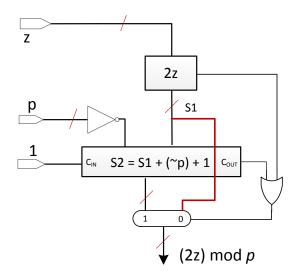

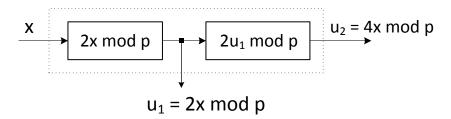

| 3.7 | Modular doubling architecture                      | 46 |

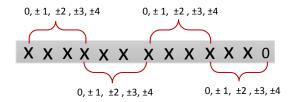

| 3.8 | Radix-4 Booth encoding                             | 48 |

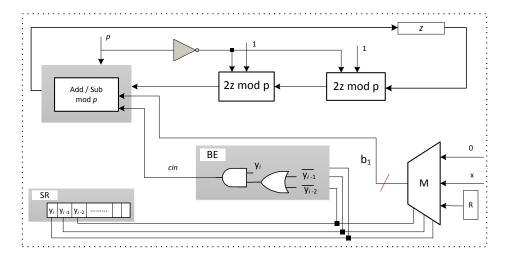

| 3.9  | R4BIM multiplier architecture                                       | 51  |

|------|---------------------------------------------------------------------|-----|

| 3.10 | Radix-8 Booth encoding                                              | 52  |

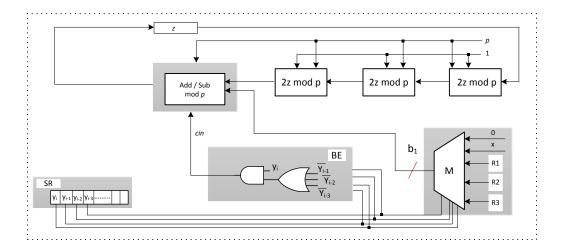

| 3.11 | R8BIM multiplier architecture                                       | 55  |

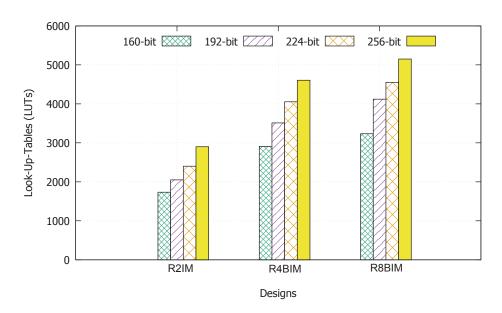

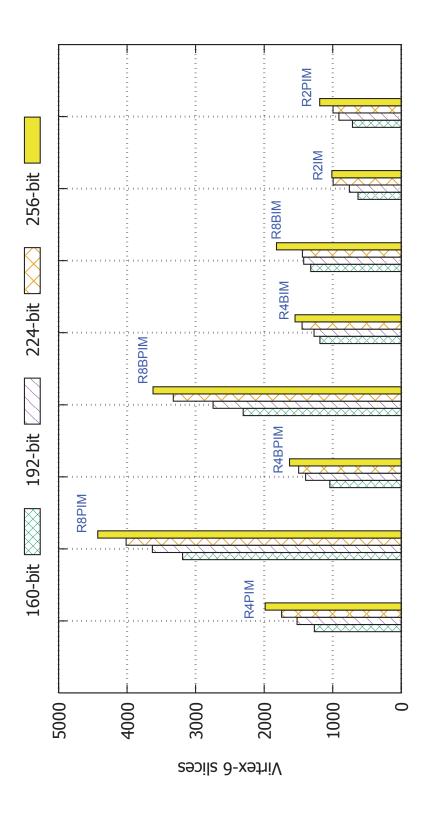

| 3.12 | Area comparisons of IM multipliers                                  | 57  |

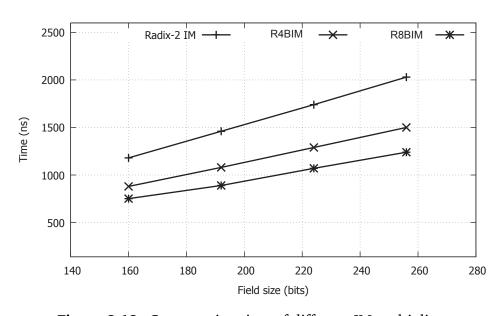

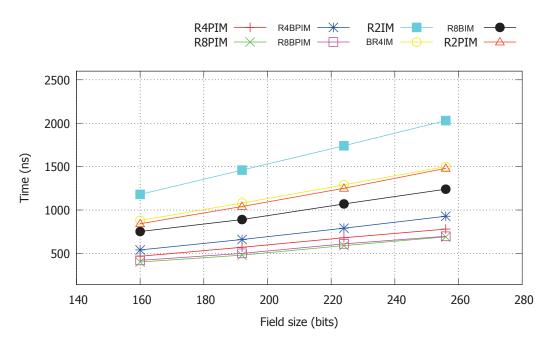

| 3.13 | Computation time of different IM multipliers                        | 59  |

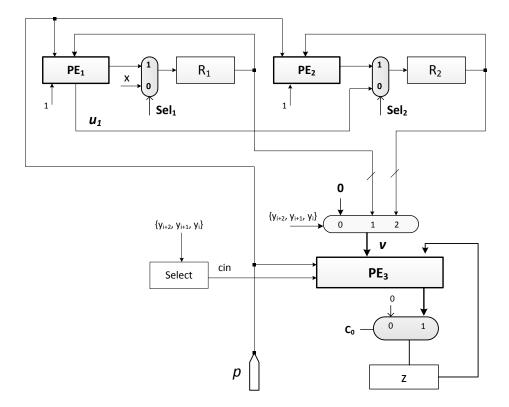

| 4.1  | R4PIM multiplier hardware architecture                              | 67  |

| 4.2  | Internal architecture of first processing element                   | 67  |

| 4.3  | R4BPIM multiplier hardware architecture                             | 72  |

| 4.4  | R8BPIM multiplier hardware architecture                             | 77  |

| 4.5  | Resource requirements of IM multipliers                             | 79  |

| 4.6  | Area comparison of parallel IM multipliers                          | 82  |

| 4.7  | Time comparison of higher-radix parallel IM multipliers             | 82  |

| 4.8  | Time comparison of different IM multipliers                         | 84  |

| 4.9  | Area comparison of different IM multipliers                         | 86  |

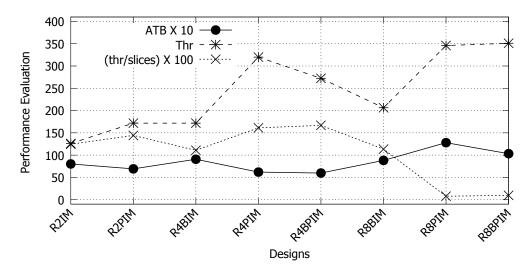

| 4.10 | Performance evaluation of IM multipliers                            | 87  |

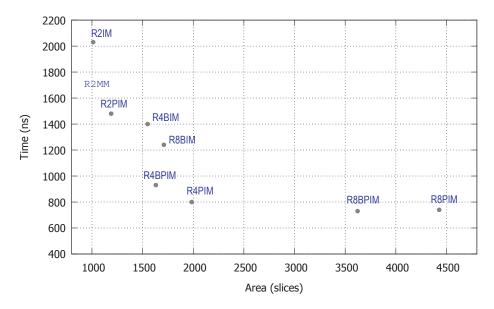

| 4.11 | Comparison of IM multipliers                                        | 89  |

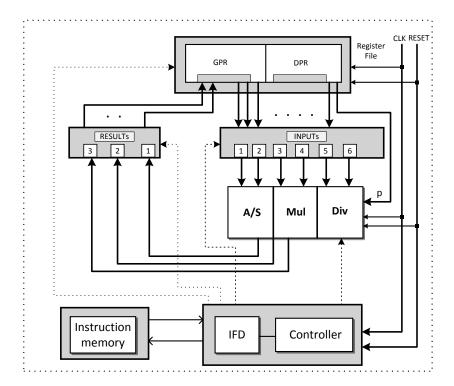

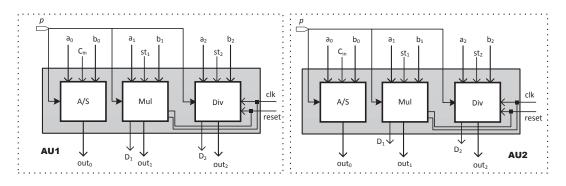

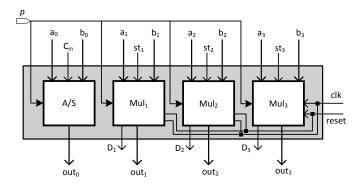

| 5.1  | EC scalar multiplier architecture using affine coordinates          | 96  |

| 5.2  | Arithmetic units for parallel execution of PD and PA operations     | 97  |

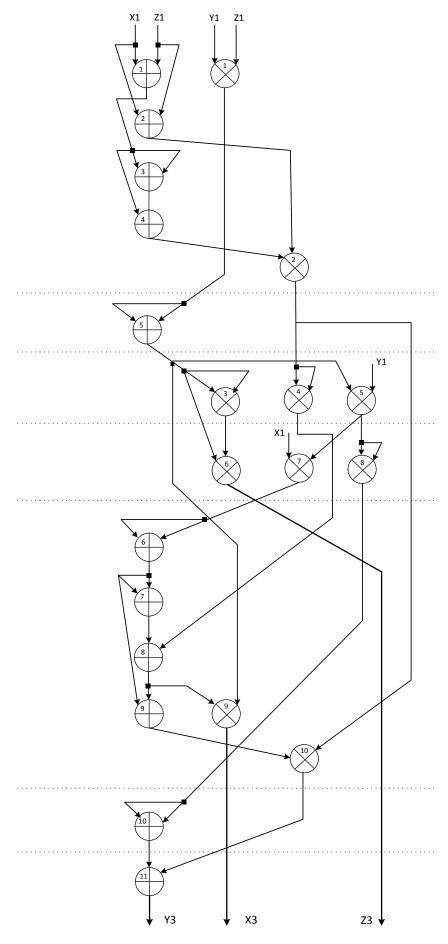

| 5.3  | Proposed arithmetic unit (AU)                                       | 102 |

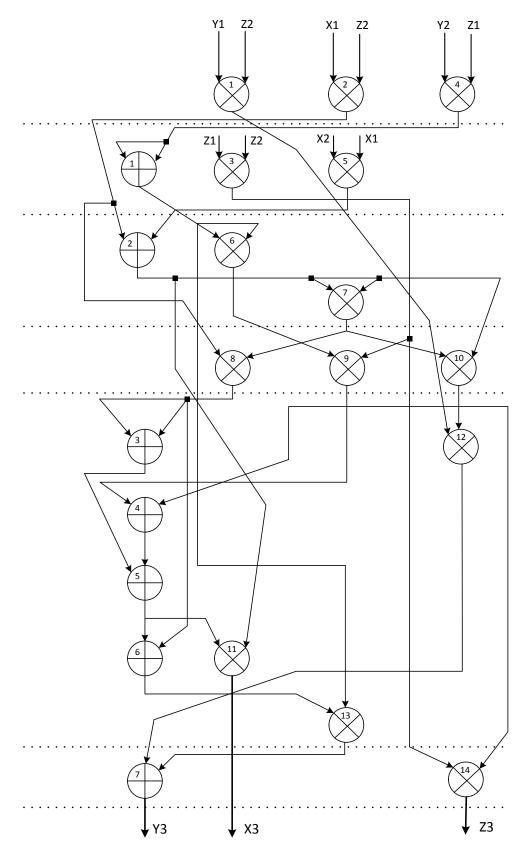

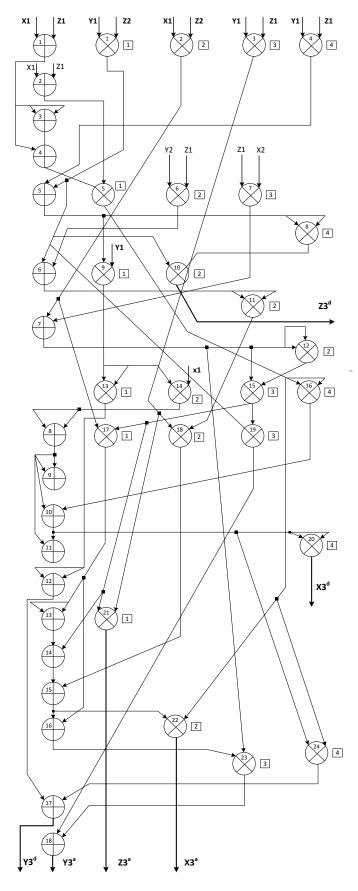

| 5.4  | Data dependency graph of PD operation using three multipliers       | 105 |

| 5.5  | Data dependency graph of PA operation using three multipliers       | 106 |

| 5.6  | Data dependency graph of concurrent PA and PD operations using four |     |

|      | multipliers                                                         | 108 |

| 5.7  | EC scalar multiplier architecture                                   | 109 |

# List of Tables

| 2.1 | NIST Gudielines for Key Sizes 2012                                      | 12 |

|-----|-------------------------------------------------------------------------|----|

| 2.2 | ECRYPT II Recommended key sizes 2012                                    | 13 |

| 2.3 | Implementation Hierarchy of ECC Based Crypto Schemes                    | 20 |

| 2.4 | NIST Recomended Primes                                                  | 27 |

| 2.5 | Virtex-6 FPGA CLB Internal Resources                                    | 31 |

| 3.1 | Modular inversion/division implementation on Virtex-6                   | 45 |

| 3.2 | Radix-4 Booth encoding                                                  | 48 |

| 3.3 | Radix-8 Booth encoding                                                  | 54 |

| 3.4 | Area comparison of IM multipliers implementation on Virtex-6            | 57 |

| 3.5 | Performance of IM multipliers on Virtex-6 for different field sizes     | 59 |

| 4.1 | Operation sequence of modular multiplication on R4PIM multiplier        | 69 |

| 4.2 | Operation sequence of modular multiplication on R4BPIM multiplier .     | 73 |

| 4.3 | Operation sequence of modular multiplication on R8BPIM architecture     | 76 |

| 4.4 | Resource requirements analysis of IM multipliers                        | 78 |

| 4.5 | Latency analysis of IM multipliers                                      | 79 |

| 4.6 | Area results of Virtex-6 FPGA implementation of Parallel IM multipliers | 81 |

| 4.7 | Timing results of Higher-radix Parallel IM multipliers on Virtex-6 FPGA | 83 |

| 4.8  | Virtex-6 FPGA implementation results of different IM multipliers                                           | 85  |

|------|------------------------------------------------------------------------------------------------------------|-----|

| 4.9  | Throughput and area-delay product of different IM multipliers                                              | 88  |

| 5.1  | EC point operations using affine coordinates                                                               | 95  |

| 5.2  | Scheduling of <b>PD</b> operation in affine coordinates                                                    | 97  |

| 5.3  | Scheduling of <b>PA</b> operation in affine coordinates                                                    | 97  |

| 5.4  | Implementation of EC scalar multiplier using affine coordinates                                            | 99  |

| 5.5  | EC PD operation in standard projective coordinates                                                         | 100 |

| 5.6  | EC PA operation in standard projective coordinates                                                         | 101 |

| 5.7  | Field operations on AU unit                                                                                | 102 |

| 5.8  | Scheduling of <b>PD</b> operation using three multipliers in projective coordinates                        | 103 |

| 5.9  | Scheduling of <b>PA</b> using three multipliers in projective coordinates                                  | 104 |

| 5.10 | Scheduling of parallel <b>PD PA</b> operations using four multipliers                                      | 107 |

| 5.11 | No of Clock cycles of EC scalar multiplication in projective coordinates                                   | 110 |

| 5.12 | Latency of EC scalar multiplication in projective coordinates                                              | 111 |

| 5.13 | Implementation results of EC scalar multiplier in projective coordinates                                   | 112 |

| 5.14 | Comparison of FPGA implemented EC scalar multipliers                                                       | 114 |

| A.1  | Number of clock cycles required for EC scalar multiplication in projective coordinates                     | 125 |

| A.2  | Cycle count of EC scalar multiplication using DA algorithm and three multipliers in projective coordinates | 126 |

| A.3  | Cycle count of EC scalar multiplication using DA algorithm and four multipliers in projective coordinates  | 127 |

| A.4  | Implementation of DAA algorithm using four multipliers in projective coordinates                           | 128 |

# List of Algorithms

| 1  | Modular addition                                        | 35 |

|----|---------------------------------------------------------|----|

| 2  | Modular subtraction                                     | 40 |

| 3  | Modular Inversion/Division                              | 43 |

| 4  | Basic Serial radix-2 Interleaved Multiplication (R2IM)  | 46 |

| 5  | Radix-4 BE Interleaved Multiplication (R4BIM)           | 49 |

| 6  | Radix-8 BE Interleaved Multiplication (R8BIM)           | 53 |

| 7  | The Montgomery Powering Ladder for exponentiation       | 64 |

| 8  | Radix-4 Parallel IM Multiplication (R4PIM)              | 65 |

| 9  | Radix-4 BE Parallel IM Multiplication (R4BPIM)          | 70 |

| 10 | Radix-8 BE Parallel IM Multiplication (R8BPIM)          | 74 |

| 11 | Double-and-add (DA) method for EC point multiplication  | 92 |

| 12 | Double-and-always-add (DAA) for EC point multiplication | 92 |

# Efficient Hardware Architecture for Scalar Multiplications on Elliptic Curves over Prime Field

#### Khalid Javeed

#### **Abstract**

Suitable cryptographic protocols are required to meet the growing demands for data security in many different systems, ranging from large servers to small hand-held devices. Many constraints such as computation time, silicon area, power consumption, and security level must be considered by the designers of hardware accelerators of the cryptographic protocols.

Elliptic curve cryptography (ECC) proposed by Koblitz and Miller, has been widely accepted. It is now considered as one of the best Public-Key Cryptography (PKC) algorithms and provides higher security strength per bit than RSA, with considerably smaller key sizes. For example, a 256-bit ECC can provide the same security strength as 3072-bit RSA. Due to its much smaller key sizes, ECC based crypto-systems are better in terms of bandwidth utilization, power consumption, and implementation cost as compared to the traditional RSA based crypto-systems. However, PKC algorithms, especially ECC are relatively expensive as compared to their symmetric-key counterparts in terms of computation time. It is an open area of research to reduce their computation cost, so that they could be used for secure communication in commercial internet based applications. Efficient implementation of elliptic curve cryptography over several new platforms have been explored in the last few decades.

This work presents efficient design strategies to perform elliptic curve scalar multiplication, the fundamental operation in all ECC based crypto-systems. Finite field arithmetic is the bottleneck in the computation of the EC scalar multiplication operation. Especially, finite field multiplication is the most time-critical operation in projective coordinates, a technique which eliminates modular inversion/division from elliptic curve group operations.

Two efficient design strategies to perform finite field multiplication are presented. The first design strategy proposes modifications to the interleaved modular multiplication algorithm using radix-4, radix-8 and Booth encoding techniques to reduce the required number of clock cycles to perform a finite field multiplication. However, higher-radix techniques incur longer critical path delay so performance is limited.

Subsequently, parallel optimization techniques are incorporated in the modified interleaved modular multiplication algorithms which enable concurrent execution of the critical operations. So the higher-radix parallel modular multipliers are optimized in terms of required number of clock cycles and critical path delays. It is observed that using Booth encoding in the parallel modular multipliers can reduce resource requirements with a slight degradation in the speed performance.

Based on the presented finite field multipliers, low latency flexible architectures to perform elliptic curve point multiplication over general prime field GF(p) is developed. On a system level, standard double-and-add and double-and-always-add techniques

are adopted. The implementation results show that the presented elliptic curve scalar multiplier architectures in this work are good trade-offs between performance and flexibility. The presented designs support general prime field so these can be used in many ECC applications.

## **Publications**

This work is based on the following contributions.

- Khalid Javeed and Xiaojun Wang "FPGA Based High Speed SPA Resistant Elliptic Curve Scalar Multiplier Architecture", International Journal of Reconfigurable Computing, Volume 2016 (2016), Article ID 6371403, 10 pages, http://dx.doi.org/10.1155/2016/6371403

- Khalid Javeed and Xiaojun Wang "Design and performance analysis of Modular Multipliers on FPGA Platform." International Conference on Cloud Computing and Security (ICCCS 2016), Nanjing, China.

- <u>Khalid Javeed</u>, Xiaojun Wang "Speed and Area Optimized Higher Radix Modular Multipliers "Cryptology ePrint Archive, Report 2016/053, 2016.

- Khalid Javeed, Xiaojun Wang, and Mike Scott "Serial and Parallel Modular Multipliers over FPGA Platform" in IEEE international Conference on Field Programmable Logic and Applications (FPL 2015), London, United Kingdom.

- Khalid Javeed and Xiaojun Wang "Radix-4 and radix-8 Booth encoded interleaved modular multipliers over general prime field" in IEEE international Conference on Field Programmable Logic and Applications (FPL 2014), Munich, Germany.

- Khalid Javeed and Xiaojun Wang "Efficient Montgomery Multiplier for ECC and Pairing based Cryptography " in IEEE International Symposium on Communication Systems, Networks & Digital Signal Processing (CSNDSP 2014), Manchester, United Kingdom.

# Chapter 1

# Introduction

#### 1.1 Thesis Motivation

Cryptography is the study and design of methods to protect secret information over an insecure channel against adversaries. Cryptographic protocols are imperative to protect files and other information due to the rapid growth of security requirements on the Internet being used as a channel for communication and business in today's society. Billions of people are using the Internet as a tool for communication, e-commerce, internet banking, storage and retrieval of sensitive data from cloud servers, wireless sensors networks, mobile commerce, and many others.

Successful deployment of a data communication network depends largely on the network's ability to counter against different unwanted attackers (users), that is, how secure the network system is in the presence of many fraudulent users. Therefore, Suitable cryptographic schemes are essential to meet the growing demands for data security in many different systems, ranging from large servers to small hand-held devices. Many constraints such as computation time, area consumption, flexibility, and security must be considered by network system designers.

Different systems have different computing powers, resource limitations, and security requirements. For example, a server needs to complete a large number of tasks in a short duration of time, whereas, a more compact design is required to meet security demands in hand-held devices such as smartphones and smartcards because of their resource limitations.

On the other hand cryptanalysis, a reverse operation of cryptography, is the study of methods to break cryptographic systems either by solving the underlying mathematical problem or by exploiting the algorithmic and implementation weaknesses of the crypto-system. With the rapid advancement in technology, cryptanalysis has also flourished. Many new efficient cryptanalysis algorithms and procedures have been figured out to attack cryptographic systems either to reveal sensitive data, to alter sensitive data, or to hack a system to perform a task for which it is not designed for. Thus, security of a system can be compromised at any time. Therefore, the underlying implementation platform must be flexible to adopt new algorithms and security parameters regularly to avoid any security breach.

Dedicated hardware architectures are essential to meet the speed requirements of many real-time applications. Dedicated hardware processors have many advantages over the general purpose processor (GPP). For example, implementation of a crypto scheme on dedicated hardware yields higher performance and lower power consumption results compared to an implementation of the crypto scheme on a GPP. Therefore, in many applications the most computationally intensive tasks are performed on dedicated hardware to boost the overall performance of the systems. However, an implementation on GPP is more flexible than dedicated hardware. Field programmable gate array (FPGA) is a hardware platform that can offer the performance of a dedicated hardware as well as the flexibility of a GPP.

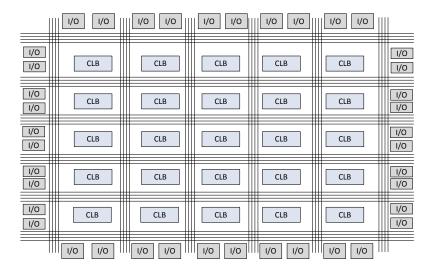

FPGA is a hardware platform which provides the flexibility for users to replace a current design with a new one in-house. FPGA has established itself as a suitable platform for implementation of security algorithms. This is due to its short design cycle time, low cost and re-usability which make it a more attractive choice compared to application specific integrated circuits (ASICs). It should be pointed out FPGA offers flexibility at the cost of lower performance and higher power consumption compared to ASIC. Therefore for applications demanding a balance of performance and flexibility, FPGA implementation is recommended. ASIC implementation is preferable in applications where high performance is the only major requirement.

#### 1.2 Thesis Aim

Many security protocols are designed using Elliptic Curve Cryptography (ECC), RSA and Pairing-based Cryptography. All these are popular types of public key cryptography (PKC) also known as asymmetric cryptography which is discussed in detail in chapter 2.

The complex and elegant mathematics of elliptic curves have attracted many researchers which led to the proposal of ECC by Miller [1] and Koblitz [2] in 1985. It provides relatively high security strength per bit resulting in a reduced bit length compared to RSA [3]. The reduced bit length means elliptic curve cryptosystems require smaller key sizes for a certain security level as compared to the traditional cryptosystems like RSA. For example, to achieve a 128-bit Advanced Encryption Standard (AES) security level, the US National Institute of Standards and Technology (NIST) recommends ECC key sizes of 256 bits. To achieve the same security level with RSA would require key sizes of 3072 bits, which is almost twelve times more than the corresponding ECC key sizes.

As a consequence, this significant reduction in key sizes has led to several new power and memory efficient implementations of ECC schemes in a variety of resource constrained environments such as wireless sensor nodes, smartphones, smartcards and many other hand-held devices and the Internet of Things (IOT).

All elliptic curve (EC) cryptographic schemes depend on a scalar multiplication operation, denoted as Q = dP, where a point P on a suitably chosen elliptic curve is multiplied with a scalar d to obtain another point Q on the same curve. In this scenario points P, Q are public parameters while the scalar d is a secret used to enable a secure communication. To find the scalar d knowing points P and Q is believed to be an intractable problem and widely known as Elliptic Curve Discrete Logarithm Problem (ECDLP), which is the basis of all ECC based schemes.

The overall performance of any ECC scheme depends on the efficient computation of the elliptic curve scalar multiplication operation, which is the most computationally intensive operation. Implementation of EC scalar multiplication on a general purpose processor can not meet performance demands of many time critical real time applications. Hence, there is a need for high speed, flexible, and reconfigurable hardware

accelerators to reduce the computation time of EC scalar multiplication. The implementation of the EC scalar multiplication must be cost effective both in terms of time and space requirements.

The main objective of this research work is to design efficient hardware architectures to compute the EC scalar multiplication operation. The scalar multiplication dP is achieved through a series of EC group operations i.e., EC point addition and EC point doubling. These group operations further rely on finite field arithmetic primitives, i.e., addition, subtraction, multiplication, and inversion/division. Among these filed operations, multiplication and inversion/division are very critical components and their efficient implementation can significantly speed up EC scalar multiplication. One common optimization technique is to eliminate inversion/division operations from EC group operations at the cost of extra modular multiplication operations. Hence, an optimized modular multiplier is very critical in a high performance design of EC scalar multiplier. Therefore, this research work focuses on the design of flexible and low latency modular multipliers over general prime field. There are several scalar multiplication algorithms and many different elliptic curves offering different tradeoffs between computational performance and level of security, therefore flexibility is considered in the proposed designs, which is required in many applications.

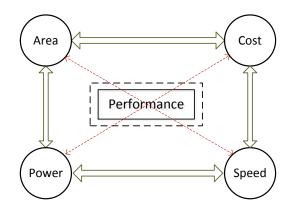

Figure 1.1: Performance evaluation metrics

This research work first explores several hardware design techniques to optimize the finite field arithmetic primitives especially a modular multiplication operation. Subsequently, based on these optimized finite field arithmetic primitives and by exploiting the possible parallelism in EC group operations, the work focuses on the design of high performance hardware architectures to perform EC scalar multiplication operation.

In cryptanalysis, the ECDLP can be bypassed by exploiting several algorithmic and implementation weaknesses termed as side channel attacks (SCA). For example, if one can have somehow gain access to a cryptographic device, then he may be able to reveal the secret scalar d by monitoring timing and power consumption profiles of the device. Simple and most common SCAs are based on the timing and simple power analysis. Therefore, this research work also adopted the most common techniques to resist the timing and simple power analysis attacks.

Figure 1.1 demonstrates that several performance evaluation metrics are interrelated, thus enhancing one of these can affect the others. For example, increasing performance by improving speed (reducing computation time) may increase area, power consumption, and cost requirements, thus, it is very difficult to achieve all design goals at the same time. Therefore, it is important to evaluate different designs optimized to achieve different performance metrics. In this work, we are more focused on flexible and high performance (in terms of computation time) designs without significant increase in area as compared to other contemporary EC scalar multiplier designs.

## 1.3 Thesis Contributions

The contribution of this research work is mainly comprised of efficient hardware architectures for finite field arithmetic primitives including addition, subtraction, multiplication, inversion, and division. Based on these optimized finite field arithmetic primitives, high performance hardware architectures for elliptic curve scalar multiplication over a general prime field are presented. The presented hardware architectures for modular addition, modular subtraction, and modular inversion/division operations are considered as minor contributions while the major contributions of the work are:

- Radix-4 and Radix-8 Booth Encoded Interleaved Modular Multipliers

- The bit serial interleaved multiplication algorithm is modified using radix-4, radix-8 and Booth encoding techniques. The modified radix-4 and radix-8 interleaved multipliers can reduce the number of clock cycles required for one modular multiplication by 50% and 66%, respectively as compared to the bit serial interleaved multipliers while maintaining a competitive critical path delay. Through efficient use of optimized carry chains available in

FPGAs and through exploiting the parallelism among operations, the proposed radix-4 and radix-8 Booth encoded multipliers can compute a 256-bit modular multiplication in  $1.48\mu s$  and  $1.24\mu s$  respectively, which are 26.6% and 39% improvement over the corresponding bit serial interleaved multiplier. A thorough comparison of the radix-4 and radix-8 Booth encoded interleaved multipliers with the bit serial interleaved multipliers shows that the proposed radix-4 and radix-8 interleaved multipliers are optimized for a high throughput rate.

#### • Parallel Radix-4 and Radix-8 Interleaved Modular Multipliers

- This part of the work presents radix-4 and radix-8 parallel interleaved modular multipliers with their efficient hardware architectures. The introduced parallelism helps to execute the critical operations concurrently while radix-4 and radix-8 techniques are incorporated to reduce the iteration count which determines the required number of clock cycles. It is also observed that incorporating Booth encoding logic in the parallel interleaved multipliers can reduce area cost with a slight degradation in the maximum achievable frequencies. The proposed radix-4 and radix-8 parallel interleaved multipliers are implemented in Verilog HDL and synthesized targeting virtex-6 FPGA platform using Xilinx ISE 14.1 Design suite. The radix-4 parallel interleaved multiplier computes a 256-bit modular multiplication in 0.78  $\mu$ s, occupies 1985 slices, at 166 MHz in a cycle count of  $\lfloor n/2 \rfloor + 5$ . The radix-8 parallel interleaved multiplier performs the same bit length operation in 0.69  $\mu$ s, occupies 3622 slices, achieves 123.43 MHz frequency in a cycle count of  $\lfloor n/3 \rfloor + 4$ . The implementation results further reveal that incorporating Booth encoding logic in the radix-4 and radix-8 parallel interleaved multipliers can save 18% FPGA slices without any significant performance degradation.

#### • High Performance Elliptic Curve Scalar Multiplier Architectures

This part of the thesis presents efficient hardware architectures to compute EC scalar multiplication operation in affine and standard projective coordinates. On the top level the double-and-add (DA) method and the double-and-always-add (DAA) method for EC scalar multiplication are used. In affine coordinates low

level field operations required to perform EC group operations are modular addition, subtraction, multiplication and inversion/division. In the case of projective coordinates, to compute the EC group operations only modular addition, subtraction and multiplication operations are required. Strategies to perform these low level field operations are presented in Chapters 3 and 4. The design of EC scalar multiplier architectures making use of the low level field operations are described below.

Using the double-and-add (DA) method one can not perform EC group operations in parallel, as there is very limited scope of parallelism in the low level field operations in affine coordinates. Therefore an arithmetic unit in this case incorporates a single modular adder/subtractor, multiplier and divider units.

On the other hand using the double-and-always-add (DAA) method, EC group operations can be performed concurrently, so dual instances of the arithmetic unit are used in the design of a high speed elliptic curve scalar multiplier architecture in affine coordinates. The proposed architecture for elliptic curve scalar multiplier in affine coordinates is synthesized targeting Virtex-6 FPGA platform for various different field sizes. In the case of a single arithmetic unit, it computes a 256-bit elliptic curve scalar multiplication in 2.51 ms in 330K clock cycles and consumes 4807 Virtex-6 FPGA slices. Whereas in the case of two arithmetic units it takes 1.75 ms, 229.37K clock cycles to compute the same bit length operation and consumes 9213 Virtex-6 FPGA slices. The presented EC scalar multiplier architecture using two arithmetic units also provides a resistance to timing and simple power analysis attacks.

- Using standard projective coordinates one can eliminate field inversion/division operation in the computation of EC group operations at the cost of

more field multiplications. This part presents a high performance hardware

architecture to compute a EC scalar multiplication operation using projective coordinates. It shows that using projective coordinates there are many

possibilities of parallelism in the underlying field operations, therefore the

performance of the presented EC scalar multiplier architecture in projective

coordinates is shown by employing a number of parallel multiplier units.

On the system level again the same algorithms (standard DA and DAA) are adopted as in the case of affine coordinates. On Virtex-6 FPGA platform using four parallel multipliers, a 256-bit EC scalar multiplication operation is completed in 1.46 ms and consume 11.65K slices. The results show that the proposed EC scalar multiplier designs offer significant improvements in the computation time with significant reduction in the required number of clock cycles as compared to the other reported designs. Therefore, the presented EC scalar multipliers are useful for many ECC based schemes.

## 1.4 Thesis Organization

The rest of this thesis is organized as follows:

- 1. **Chapter 2** gives a brief introduction to the mathematical background of finite field and elliptic curve cryptography. It also lists different algorithms and some of the common optimization techniques to compute EC scalar multiplication operations using layered hierarchical implementations. Finally, the chapter also gives a basic introduction to FPGA architecture.

- Chapter 3 first presents hardware architectures for modular addition, subtraction and inversion/division operations. Then, the radix-4 and radix-8 Booth encoded interleaved modular multipliers are presented with their hardware architectures.

- 3. **Chapter 4** details further optimization of the modular multiplier architectures presented in Chapter 3. Then, it presents a detailed performance evaluation of the proposed interleaved modular multipliers compared to related contemporary designs on the basis of area, speed, throughput and flexibility.

- 4. **Chapter 5** presents high performance elliptic curve scalar multiplier architectures by utilizing the hardware architectures of finite field arithmetic primitives proposed in Chapters 3 and 4. The performance of the proposed elliptic curve scalar multipliers are also compared with contemporary designs in the literature.

- 5. **Chapter 6** is devoted to possible future research directions and it also presents an overall conclusion of the thesis work.

# Chapter 2

# Background

This chapter briefly introduces the background and mathematical tools that are of prime importance in elliptic curve scalar multiplication. First, some basic concepts of different cryptographic schemes with their recommended key sizes are introduced. Then, an introduction to finite field and elliptic curve arithmetic over prime field is presented. Subsequently, implementation strategies of elliptic curve crypto schemes at different levels of implementation hierarchy are discussed. Finally, an introduction to FPGA is given in the last section of this chapter.

All cryptographic encryption/decryption methods, irrespective of their applications can be categorized into symmetric or asymmetric key algorithms. Symmetric key algorithms are sometimes called Private-Key cryptography, whereas asymmetric key algorithms are widely referred to Public-Key cryptography (PKC).

# 2.1 Symmetric-Key Cryptography

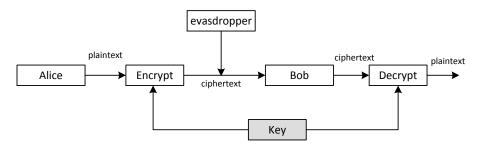

Symmetric or Private-Key algorithms are a class of algorithms which use a single key for encryption and decryption purposes, therefore the key used for these tasks should be kept secret and must be communicated securely among the participants prior to any communication. Encryption/Decryption tasks using symmetric key algorithms are fairly simple as shown in Figure 2.1, where Alice sends her message (plaintext)

after doing encryption with a *key*, which must be available to Bob as well. Bob after receiving "ciphertext" (encrypted message from Alice) decrypts it with the same *key* and recovers the original plain text message. Security of these systems depends on

Figure 2.1: Symmetric-Key encryption/decryption

how securely the key is managed and transmitted among users in a communication network. The private key algorithms are efficient and easy to implement but there are certain drawbacks as well. The first problem is that each party must have this secret key before any secure communication between them, in other words the secret key must be securely shared among all parties involved in the communication. The second problem refers to the key management issues, because a communication in a group of n parties would require n(n-1)/2 keys, so these keys should be kept secure and must be changed regularly to avoid any security breaches.

Symmetric-Key cryptographic algorithms are further classified into block and stream ciphers. Block cipher algorithms operate on blocks of input data and produce the corresponding output blocks, where as in stream cipher very small chunks (can be a single bit) of input data are fed into the algorithm to obtain the corresponding small chunks of output data. Digital Encryption Standard (DES) [4] and Advanced Encryption Standard (AES) [5], [6] are the well known block ciphers schemes, whereas RC4 [7] is an example of stream ciphers.

## 2.2 Public-Key Cryptography

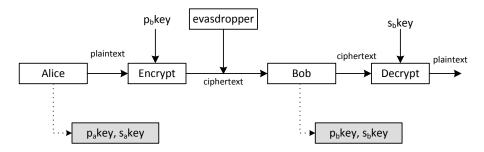

Whitfield Diffie and Martin Hellman introduced Public-Key cryptography (PKC) in 1970 [8]. After its inception PKC has solved many problems and enabled the creation of many new interesting protocols considered to be impossible with Symmetric-Key cryptography [9]. PKC algorithms use a pair of keys (public key, private key) for encryption and decryption tasks. A user, Bob, generates his key pair ( $p_b$ key,  $s_b$ key),  $p_b$ key

Figure 2.2: Public-Key encryption/decryption

is his public key while  $s_b$ key is his private key. He publishes the  $p_b$ key and securely stores his  $s_b$ key. If Alice wants to send a message to Bob, she needs to encrypt the message with Bob's public key, i.e,  $p_b$ key. Bob on receiving the ciphertext decrypts it with his private key ( $s_b$ key) to recover the message as shown in Figure 2.2.

The pair of keys are related in such a way that from the knowledge of one to infer the other is a mathematically intractable problem. Ideally to generate a public key from a private key is based on a one way function. The one way function, as its name suggests, is easy to compute in one direction and is completely infeasible to reverse the operation. Different PKC schemes can be constructed based on different one way functions.

Ronald Rivest, Adi Shamir, and Len Adleman in 1978, proposed a very popular crypto-system which is widely known as RSA [3]. Since its appearance, RSA has been adopted and used widely in many applications and communication networks. Theoretically, the security of RSA crypto-system is based on the mathematical problem (one way function) of integer factorization. RSA has been a dominant Public key system for many years, but with the rapid increasing of the number of resource constrained devices connected to the Internet, a more compact public-key system is required. In 1985 Victor Miller [1] and Neal Koblitz [2] proposed elliptic curve cryptography (ECC) which requires much smaller key sizes as compared to RSA and is discussed in the next section.

Cryptography is the fundamental tool to secure sensitive data. However, efficient implementations of cryptographic algorithms are required to meet speed requirements in high-speed networks. The high processing rate enables cryptographic algorithms to fully utilize the available network bandwidth. The implementation must also be flexible and upgradeable in the field to the rapid changes in algorithms and standards. Therefore, FPGA as an underlying implementation platform provides software-like

| Date     | Minimum  | Symmetric  | RSA   | ECC | ECC : AES | RSA: ECC |

|----------|----------|------------|-------|-----|-----------|----------|

|          | Strength | Algorithms |       |     |           |          |

|          |          | (AES)      |       |     |           |          |

| 2010     | 80       | 2-key      | 1024  | 160 | 2:1       | 6.4:1    |

|          |          | triple-DES |       |     |           |          |

| 2011-230 | 112      | 3-key      | 2048  | 224 | 2:1       | 9.14:1   |

|          |          | triple-DES |       |     |           |          |

| >2030    | 128      | AES-128    | 3072  | 256 | 2:1       | 12:1     |

| >>2030   | 192      | AES-192    | 7680  | 384 | 2:1       | 20:1     |

| >>>2030  | 256      | AES-256    | 15360 | 512 | 2:1       | 30:1     |

**Table 2.1:** NIST Gudielines for Key Sizes 2012 [10, 11]

flexibility and hardware-like performance. FPGA based security protocols can be deployed in many critical embedded systems such as wireless networks, electronic banking, electronic commerce, government online service and Virtual Private Networks (VPNs).

Mostly PK algorithms such as RSA and ECC are deployed in hybrid schemes, where they are used to design different protocols e.g. key exchange, digital signature, etc., while normal encryption/decryption tasks are achieved using symmetric key algorithms such as AES and DES due to their simplicity. However, PK algorithms can be used for encryption/decryption. This work sees ECC based cryptographic schemes being deployed in a hybrid scenario.

## 2.3 Cryptographic Key Sizes

To ensure cryptographic schemes are secure against different attacks, different recommendations have been made and updated with time to overcome known weaknesses of the cryptographic systems [12]. In symmetric key cryptography the key sizes directly determines the level of security. Nowadays AES is considered to be a benchmark among symmetric schemes, while RSA is considered as a benchmark in asymmetric schemes.

Table 2.1 and Table 2.2 demonstrate two recommendations by the US National Institute of Standards and Technology (NIST) and ECRYPT II, respectively [13]. The NIST [10] recommendations in Table 2.1 suggest that 112-bit symmetric key sizes are enough for up-to 2030 after that 128-bit symmetric key sizes are recommended. As in symmetric key algorithms key sizes directly determine the level of security, therefore

**Table 2.2:** ECRYPT II Recommended key sizes 2012 [14]

| Date                                    | Symmetric<br>Algorithms | RSA   | ECC | Hash | ECC : AES | RSA: ECC |

|-----------------------------------------|-------------------------|-------|-----|------|-----------|----------|

| Protection upto 2015                    | 80                      | 1024  | 160 | 160  | 2:1       | 6.4:1    |

| Short-term<br>Protection<br>(2015-2020) | 96                      | 1176  | 192 | 192  | 2:1       | 6.13:1   |

| Medium-term protection (2015-2030)      | 112                     | 2432  | 224 | 124  | 2:1       | 10.9:1   |

| Long-term protection (2015-2040)        | 128                     | 3248  | 256 | 256  | 2:1       | 12.69:1  |

| Foreseeable<br>future                   | 256                     | 15424 | 512 | 512  | 2:1       | 30.1:1   |

AES-128 would be required to provide a minimum security after 2030. Similar conclusions can be drawn from ECRYPT II recommendations given in Table 2.2, where short-term, medium-term, and long-term key sizes recommendations are listed.

As mentioned before for asymmetric schemes RSA is considered as a benchmark. In both Tables 2.1 and 2.2, it is recommended that to achieve 128-bit AES security level, RSA needs to have more than three thousand bits, more precisely 3072 [10] (NIST recommendation) and 3248 [14] (ECRYPT II recommendation). It is also recommended that to achieve the same 128-bit AES security level, the required key sizes in ECC is only 256-bit which is 12 times smaller than RSA key sizes. This difference in required key sizes is even bigger at higher security level, 20 times smaller ECC key sizes than the corresponding RSA at 192-bit AES security level. For 256-bit AES security level, ECC key sizes are 30 times smaller than RSA.

It is worth noticing that the ECC key sizes are only twice the symmetric key sizes while these are much smaller than the traditional asymmetric schemes such as RSA. Smaller key sizes translate into lower implementation cost, higher performance, lower power consumption, lower bandwidth requirements, and many other benefits. Therefore, ECC will play a very important role in secure communications in resource constrained devices in the near feature.

#### 2.4 Finite Field

Finite field is the fundamental of cryptography, coding theory, and many other areas of mathematics and computer science. This section describes some basic definitions and then arithmetic operations in a finite field are discussed [15].

### **2.4.1** Groups

A Group concept is extensively used in modern cryptography. A Group G consists of set of elements and an operator \*. When the operator is applied on the elements of G, it satisfies the following properties:

- The group is closed with respect to operator \*, i.e.,  $\forall a, b \in G, a * b = c \in G$ .

- Associative law:  $a*(b*c) = (a*b)*c, \forall (a,b,c) \in G$ .

- Identity law :  $a * 1 = 1 * a = a, \forall a \in G$ .

- Inverse law:  $a * a^{-1} = a^{-1} * a = 1, \forall a \in G$ .

- Commutative law :  $a * b = b * a, \forall a \in G$

## **2.4.2** Rings

A ring R is an algebraic structure, in which elements can be added and multiplied while satisfying the following properties:

- Commutativity:  $\forall a, b \in R, a + b = b + a \in R$

- Associativity:  $\forall a, b, c \in R, (a+b)+c = a+(b+c) \in R; (a \times b) \times c = a \times (b \times c) \in R$

- **Distributivity**:  $\forall a, b, c \in R, a \times (b+c) = (a \times b) + (a \times c)$

- Additive identity: An element 0 in *R* such that  $a + 0 = a \ \forall a \in R$ .

- **Multiplicative identity**: An element 1 in *R* such that  $a \times 1 = a \ \forall a \in R$ .

- Additive inverse : An element  $a_1$  in R such that  $a + a_1 = 0 \ \forall a \in R$ .

Examples of rings are integer numbers, the rational numbers, the complex numbers and the real numbers. A number in a ring is said to have a multiplicative inverse if there is a unique element  $b \in R$  such that  $a \times b = b \times a = 1$ . Then the element b is a multiplicative inverse of a.

#### 2.4.3 Finite Fields

A field is a commutative ring that has multiplicative inverse for all non-zero elements. A field is a set equipped with arithmetic operations such as addition, subtraction, multiplication and division, while satisfying commutative, associative and distributive properties.

A finite field also called a Galois field is a field which has a finite number of elements. The number of elements in the field is called the order of the field. The order of a finite field is always the power of a prime p i.e.  $q = p^m$ , where m is any positive integer and q is the order of field. The prime p is called the characteristic of a field. If the order q of the field is equal to prime p then the field is called a prime field. A more formal definition of finite field and its properties are given below.

A finite field consists of a set F together with two operations i.e, addition (denoted by +) and multiplication (denoted by  $\times$ ), such that it satisfies the following arithmetic properties:

- 1.  $\forall a, b \in F, a + b \in F \text{ and } a \times b \in F$

- 2.  $\forall a, b \in F, a + b = b + a \text{ and } a \times b = b \times a$

- 3.  $\forall a, b, c \in F$ ,  $a \times (b+c) = (a \times b) + (a \times c)$

- 4.  $\forall a, b, c \in F$ , (a+b)+c=a+(b+c) and  $(a \times b) \times c=a \times (b \times c)$

- 5.  $\exists 0, 1 \in F$ , (a + 0) = (0 + a) = a,  $(a \times 1) = (1 \times a) = a$ . Then, 0, 1 are additive and multiplicative identities of the group respectively.

- 6.  $\forall a \in F, \exists (-a) \in F \text{ such that } (a + -a) = (-a + a) = 0$

- 7.  $\forall a \in F, \exists a^{-1} \in F \text{ such that } a \times a^{-1} = a^{-1} \times a = 1.$  Then,  $a^{-1}$  is called a multiplicative inverse of a.

As an algebraic structure every field is a commutative ring with an additional property of a multiplicative inverse for non zero elements, however, every ring may not be a field. The smallest set of finite fields are defined on characteristics 2 and 3 and are denoted as  $\mathbb{F}_2$  (GF(2)) and  $\mathbb{F}_3$  (GF(3)). In this work, finite fields defined over a large prime characteristic p are used and described as GF(p) or  $\mathbb{F}_p$ . The number of elements in a finite field is called its order.

This research work is focused on elliptic curve cryptography over prime fields. In this case  $\mathbb{F}_p$  or GF(p) consists of all integers  $\{0, 1, 2, ...., p-1\}$ , where arithmetic operations are performed on integers modulo p.

#### 2.4.4 Prime Field Arithmetic

This section describes the arithmetic operations over prime field  $\mathbb{F}_p$ . There are different strategies to compute these operations efficiently [16], [15]. Efficient techniques to compute finite field arithmetic operations are described in Chapter 3. However, a general description of these operations is described here as follows:

- $\mathbb{F}_p$  Addition: Given  $a, b \in \mathbb{F}_p$ , compute (a + b) and (a + b p). Output = (a + b p) if  $(a + b) \ge p$ , else output= (a + b).

- $\mathbb{F}_p$  **Subtraction:** Given  $a, b \in \mathbb{F}_p$ , compute (a b) and a b + p. Output = (a b + p) if (a b) < 0, else output= (a b).

- $\mathbb{F}_p$  **Multiplication:** Given  $a, b \in \mathbb{F}_p$ , compute  $z = (a \times b) \mod p$ , where z is the remainder of dividing  $(a \times b)$  by p.

- $\mathbb{F}_p$  **Inversion:** For a given non zero element  $a \in \mathbb{F}_p$ , a multiplicative inverse exists, if and only if a and p are relatively prime i.e, gcd(a,p) = 1, then compute  $z = a^{-1} \mod p$ , where z is a unique integer in  $\mathbb{F}_p$  such that  $(a \times z) \mod p = 1$

- $\mathbb{F}_p$  **Squaring:** For a given  $a \in \mathbb{F}_p$ , compute  $z = (a^2 \mod p)$ , which is  $\mathbb{F}_p$  multiplication of an operand to itself.

## 2.5 Introduction to Elliptic Curves

This work considers an elliptic curve  $\mathbb{E}$ , defined over prime field GF(p), where p is a large prime characteristic number, then  $\mathbb{E}$  is defined as a set of points (x, y), with elements in GF(p) and the curve equation in short Weierstrass form [15,16] is represented as

$$\mathbb{E}: y^2 = x^3 + ax + b \tag{2.1}$$

Where, a, b, x, and  $y \in GF(p)$  and  $4a^3 + 27b^2 \neq 0$  (modulo p). The set of all points (x, y) that satisfy (2.1), plus the point at  $\infty$  (infinity) make an abelian group. The number of points on the curve is called the *order* of the curve. EC point addition and EC point doubling operations over such groups are used to construct many elliptic curve crypto-systems.

### 2.5.1 Elliptic Curve Scalar Multiplication

The main operation in all EC cryptographic schemes is the multiplication of a point on an elliptic curve with a scalar (an integer). It is also known as point multiplication and is given as

$$Q = dP (2.2)$$

Where d is a scalar value, P, Q are points on a same elliptic curve. The operation

$$dP = \underbrace{P + P + P + \dots + P}_{d \text{ times}}$$

can be achieved by d-1 repeated point additions. All ECC based protocols need to compute this dP, hence it is the central operation in all ECC schemes. It is a one way function where a forward computation i.e, dP is easy, but to calculate d from the given Q and P is computationally hard. It is called the elliptic curve discrete logarithm problem (ECDLP). Thus, mathematically, the security of elliptic curve cryptosystems depends on the hardness of ECDLP which is defined as

For a given elliptic curve E defined over  $\mathbb{F}_p$ , a point  $P \in E(\mathbb{F}_p)$  of order r, and a second point  $Q \in E(\mathbb{F}_p)$ , ECDLP is to determine the integer  $d \in [0, r-1]$  such that Q = dP

ECDLP is the heart of elliptic curve cryptography. The security of any cryptosystem defined over elliptic curves depends on the hardness of the ECDLP problem. It is

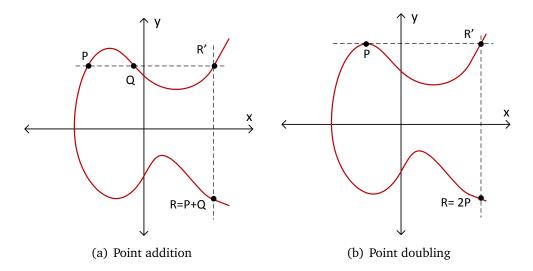

Figure 2.3: EC group operations

believed to be stronger and harder than the other problems such as the integer factorization problem, which is the foundation of RSA cryptosystems. As a consequence, it is expected that the key sizes of a cryptosystem defined over ECC, using a suitable chosen elliptic curve and underlying field for a given security level are significantly smaller than those cryptosystem defined over RSA as demonstrated in Tables 2.1 and 2.2.

Given a large d, it is not feasible to compute dP through repeated EC point addition (PA) operation. Therefore, another special group operation of adding a point to itself is defined and called EC point doubling (PD). There are many EC scalar multiplication algorithms discussed in [16] [15], EC PA and PD are the two main basic operations in all of these algorithms.

## 2.5.2 Elliptic Curve Group Operations

EC scalar multiplication is computed by a series of EC PD and PA operations. The EC PA operation is an addition of two distinct EC points P with coordinates  $(x_1, y_1)$  and Q with coordinates  $(x_2, y_2)$ .

The geometrical interpretation of the EC PA operation on EC is shown in Figure 2.3(a), where a line is drawn passing through the two given points P and Q. The line intersects the curve at a third point R'. The point R' when reflected along the x-axis results in a point R, which is the resultant point of the EC PA operation. Let  $(x_3, y_3)$  be

the coordinates of R, then the mathematical interpretation of Figure 2.3(a) is given as

$$x_3 = \lambda_{PA}^2 - x_1 - x_2 \tag{2.3}$$

$$y_3 = \lambda_{PA}(x_1 - x_3) - y_1 \tag{2.4}$$

$$\lambda_{PA} = \frac{(y_2 - y_1)}{(x_2 - x_1)} \tag{2.5}$$

Similarly, in the EC PD operation, a tangent line to the curve is drawn at the given point P. The tangent line intersects the curve at point R'. The reflection of point R' along the x-axis is the resultant point of the EC PD operation, i.e., R = 2P, as shown in Figure 2.3(b). A mathematical translation of this procedure is given as follows:

$$x_3 = \lambda_{PD}^2 - 2x_1 \tag{2.6}$$

$$y_3 = \lambda_{PD}(x_1 - x_3) - y_1 \tag{2.7}$$

$$\lambda_{PD} = \frac{(3x_1^2 + a)}{2y_1} \tag{2.8}$$

Note that, the only difference in the computation of EC PD and PA operations are their respective  $\lambda$  values as given in equations (2.5) and (2.8). It is also worth mentioning that EC points with two coordinates (x, y) is called affine coordinates representation.

# 2.5.3 Order of an Elliptic Curve

All the points in  $F_p$  that satisfy the equation (2.1) plus the point at infinity  $\infty$  forms the elliptic curve group and is denoted as  $E(F_p)$ . Each group is comprised of a finite number of elements. The total number of points on the curve, including the point  $\infty$ , is called the order of the curve. The order of the curve is usually denoted as  $\#E(F_p)$ . The upper and lower bounds of the order of the curve can be approximated by Hasse's theorem described as follows:

Let  $\#E(F_p)$  be the number of points in  $E(F_p)$ , then, it is

$$p + 1 - 2\sqrt{p} \le \#E(F_p) \le p + 1 + 2\sqrt{p}$$

Table 2.3: Implementation Hierarchy of ECC Based Crypto Schemes

| Leyers | Operations                                                      |  |  |  |  |

|--------|-----------------------------------------------------------------|--|--|--|--|

| 4      | EC curve crypto schemes (key exchange, digital signature, etc)  |  |  |  |  |

| 3      | EC scalar multiplication                                        |  |  |  |  |

| 2      | EC group operations (PA, PD)                                    |  |  |  |  |

| 1      | Finite Field arithmetic primitives                              |  |  |  |  |

|        | GF(p) addition, subtraction, multiplication, inversion/division |  |  |  |  |

The interval  $[p+1-2\sqrt{p} \le \#E(F_p) \le p+1+2\sqrt{p}]$  is known as the Hasse interval [17,18]. Since  $2\sqrt{p}$  is very small relative to p, therefore  $\#E(F_p) \approx p$ . However, the Schoof algorithm [19] is an efficient way to find the exact number of points on an elliptic curve. Similarly, the order of a point is described as follows.

For any point P on elliptic curve E over  $F_p$ , there is a small positive integer r such that  $rP = \infty$ , then r is called the order of point P. The order of any point always exists and divides the order of the curve  $\#E(F_p)$ .

# 2.5.4 EC Crypto Schemes Implementation Hierarchy

Typical implementation hierarchy of EC based cryptographic schemes is shown in Table 2.3. It is divided into four layers. Top layer consists of ECC based cryptographic protocols such as key exchange [20], EC digital signature algorithm (ECDSA) [21], secure shell (SSH) [22], transport layer security (TLS) [23], Bitcoin [24], etc. An interested reader is referred to [25]. The next layer is the EC scalar multiplication operation which is comprised of two EC group operations: EC PD and PA operations. Further down, these EC group operations consist of finite field arithmetic operations including modular addition, subtraction, multiplication and division. These finite field primitives are the fundamental arithmetic operations, therefore they have a strong impact on the overall crypto-system performance. The next section describes a simple key exchange protocol based on ECC to illustrate the operations in elliptic curve cryptography.

# 2.5.5 Diffie-Hellman Key Exchange

Diffie-Hellman key exchange method provides an ability to transfer keys securely over an insecure channel without compromising security of the encryption process. In a

Figure 2.4: Diffie-Hellman key exchange scheme

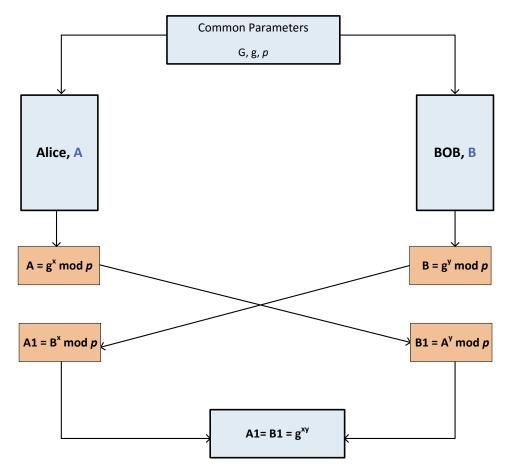

finite field, the Diffie-Hellman key exchange methods involves several steps show in Figure 2.4 and described as follows.

- First Alice and Bob has to agree on common parameters (G, g, p), where G is group with generator g and a prime p.

- Alice computes  $A = g^x \mod p$ , for a random chosen  $x \in [1, p-1]$  and sends A to Bob.

- Bob computes  $B = g^y \mod p$ , for a random chosen  $y \in [1, p-1]$  and sends B to Alice.

- Alice computes  $A1 = B^x \mod p$ .

- Bob computes  $B1 = A^y \mod p$ .

Since A1 and B1 are equal i.e.,  $g^{xy} \mod p$ , Alice and Bob successfully shared a secret which they can use as an encryption key in the further subsequent communication. An eavesdropper only have A, B, g, p, to find x while knowing g and  $g^x$  mod p he has to

Figure 2.5: EC based Diffie-Hellman key exchange scheme

solve the discrete logarithm problem (DLP), which is not feasible to solve for enough large values of p in a polynomial time.

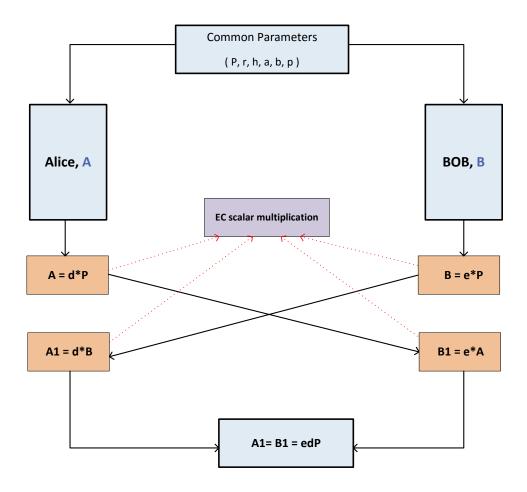

An elliptic curve version of the Diffie-Hellman key exchange method is known as Elliptic Curve Diffie-Hellman (ECDH) key exchange. It is shown in Figure 2.5 and the steps involved in the ECDH is given as follows.

- First Alice and Bob has to agree on common parameters (P, r, h, a, b, p), where point P is a group generator of order r, h is a cofactor, a and b are elliptic curve constants and p is a large prime.

- Alice computes A = dP, for a randomly chosen  $d \in [1, r-1]$  and sends A to Bob.

- Bob computes B = eP, for a randomly chosen  $e \in [1, r-1]$  and sends B to Alice.

- Alice computes A1 = dB.

- Bob computes B1 = eA.

Since A1 and B1 are the same i.e., dB = d(eP) = dA = e(dP), both parties agreed on the common secret using the ECDH method. Note that the operations dP, eP, dB, eA are commonly known as an EC scalar multiplication or EC point multiplication. Therefore, it is the fundamental operation in all the protocols based on ECC.

EC version of the DH key exchange protocol is further extended and standardized in [26, 27]. An interested reader is referred to [25] for ECC protocols, deployment, and security.

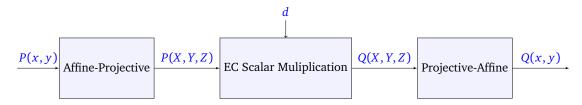

# 2.5.6 Standard Projective Coordinates

EC points represented in affine coordinates (x, y) require a modular inversion operation to compute both EC PD and EC PA operations, see equations 2.5 and 2.8. It is the most expensive operation in terms of computation time and resource requirements. In order to speed up the EC group operations, one common optimization is to represent points on an EC in such a way so that inversion free EC PD and PA operations can be computed. Different projective coordinate systems have been explored. These projective coordinate systems have the advantage of eliminating modular inversion from the group operations at the cost of increased number of modular multiplication operations. Typically at the end, one or two inversions are required to re-map from projective to affine coordinates. An overall implementation flow of the EC scalar multiplication operation in projective coordinates is shown in Figure 2.6.

One such coordinate system is called standard projective coordinates. In the standard projective space setting, a point is represented using three coordinates (X, Y, Z). An affine point P(x, y) corresponds to the point  $P(XZ^{-1}, YZ^{-1}, Z)$ , where  $Z \neq 0$  in the standard projective coordinates.

Conversions from affine-to-projective and projective-to-affine spaces are required, however these occur only once during the scalar multiplication operation. An input

Figure 2.6: EC scalar multiplication in projective coordinates

point for EC scalar multiplication operation is in affine coordinates (x, y) and its projective representation is  $(XZ^{-1}, YZ^{-1}, Z)$ , therefore affine-to-projective conversion is required which is achieved by setting Z=1 to avoid the conversion cost. Hence, affine-to-projective transformation becomes a trivial process given as

$$(x, y) \longmapsto (X, Y, 1)$$

(2.9)

More precisely, given point in affine space (x, y), its standard projective space representation is derived by setting the Z coordinate equal to one, then the other X, Y coordinates are given as

$$(x, y) \longmapsto (X, Y, 1), \quad X = x, \quad Y = y, \quad Z = 1$$

At the end of the EC scalar multiplication operation, the projective-to-affine conversion is required which is achieved as follows:

$$x = XZ^{-1}, y = YZ^{-1}$$

(2.10)

This conversion costs two multiplications and a single inversion.

# 2.5.7 Jacobian Projective Coordinates

The other commonly used coordinates system is Jacobian projective coordinates, where an affine point P(x, y) is represented as  $P(XZ^{-2}, XZ^{-3}, Z)$ . Similarly, affine-to-Jacobian transformation is trivial by setting the Z coordinate equal to one.

$$(x, y) \longmapsto (X, Y, 1)$$

(2.11)

At the end of scalar multiplication, conversion back to affine space is done as

$$x = XZ^{-2}, y = YZ^{-3}$$

(2.12)

The cost of this conversion is four multiplications and one inversion. A more detailed analysis of EC point operations in standard projective coordinates is presented in Chapter 5 with complete EC scalar multiplier architectures. Further details of the Jacobian

projective coordinates can be found in [28], [29], [16].

# 2.6 Side Channel Attacks

Algebraic attacks are not the only solution to deduce sensitive information of the cryptosystem. There are many methods to retrieve sensitive information from the physical implementation of a cryptographic device by monitoring some side channel information which are called side channel attacks (SCA) [30].

Theoretically, the security of elliptic curve cryptographic systems relies on the hardness of the ECDLP problem. However, ECDLP can be bypassed by exploiting several algorithmic and implementation weaknesses. For example, if somehow an adversary gets access to a cryptographic device, then the adversary may be able to reveal the secret by observing timing and power consumption information. Timing and simple power analysis (SPA) are the most common and simple side-channel attacks [31]. There are even more sophisticated attacks based on fault injection or differential power analysis [32]. Fan et al. in [33,34] surveyed most of the side-channel attacks and their countermeasures.

Power analysis side channel attacks are grouped into simple power analysis (SPA) and differential power analysis (DPA) [32]. SPA monitors a single instance of power consumption of a device and tries to deduce the secret information. On the other hand DPA gathers power data of several instances of the device and then statistically analyses the data to reveal the secret information.

To employ any side channel attack, an attacker needs a physical access to a cryptographic device; therefore countermeasures against these attacks are very important in cryptosystems implemented on smart cards. However, this work targets the FPGA as an implementation platform therefore it only considers algorithmic level countermeasures against timing and simple power analysis attacks.

# 2.7 Related Work

This section reviews the literature of available hardware accelerators for point multiplication on elliptic curves. It outlines some of the proposed designs to establish a

basic understanding of the state-of-the art research in this domain.

# 2.7.1 Hardware Architectures for EC Scalar Multiplication

As implementation of point multiplication on elliptic curves can be decomposed into several layers, therefore, the overall performance and efficiency could be significantly improved by optimization at different layers, independently. The fundamental or base layer of an EC cryptosystem implementation is the finite field arithmetic operations. There are different design approaches to optimize these field operations which is discussed in chapter 3. Optimized field operations can boost the overall performance of EC point multiplication which is based on EC PA and PD operations which are in turn based on these field operations.

Crypto-systems based on ECC are designed using either elliptic curves defined over the binary extension field  $GF(2^m)$  or curves defined over a prime field GF(p). The nature of operations in these fields are quite different from each other. In a binary extension field, elements are described using polynomials and reduction is done using an irreducible polynomial. On the other hand, elements in a prime field are integers and arithmetic operations are done using integer operations modulo a prime p. Therefore, binary field arithmetic imposes completely different design challenges as compared to that in prime field [35]. Typically, field operations over  $GF(2^m)$  are very much hardware friendly due to carry free arithmetic. Therefore, design challenges, implementation cost, and performance of ECC processors over binary and prime fields are not comparable, their comparison is misleading and even not possible because of their different underlying field representations. However, due to recent advancements in methods for attacking discrete logarithms, there are some concerns regarding binary curves security. Modern cryptographers tend to avoid binary curves and would like to use prime curves for long-term security. Performance comparison of ECC hardware implementation using binary and prime fields is presented in [36].

This work focuses on point multiplication on elliptic curves over prime field, therefore, the main point of discussion throughout this work is hardware implementations and analysis of ECC over prime field. For references, some of the ECC processor designs over  $GF(2^m)$  are reported in [37, 38, 39, 40, 41, 42, 43]. Review of high speed ECC processors over  $GF(2^m)$  is reported in [44], [45].

Table 2.4: NIST Recomended Primes

| p  size          | Numerical value                            | AES equivalent security level |

|------------------|--------------------------------------------|-------------------------------|

| $p_{192}$        | $2^{192} - 2^{64} - 1$                     | 96                            |

| $p_{224}$        | $2^{224} - 2^{96} + 1$                     | 112                           |

| $p_{256}$        | $2^{256} - 2^{224} + 2^{192} + 2^{96} - 1$ | 128                           |

| p <sub>384</sub> | $2^{384} - 2^{128} + 2^{96} + 2^{32} - 1$  | 192                           |

| $p_{521}$        | $2^{521}-1$                                | 256                           |

Several prime field hardware accelerators for elliptic curve scalar multiplication have been proposed during the last fifteen years. These designs can be classified into two categories: designs over standard and designs over general prime fields.

# 2.7.1.1 EC Scalar Multipliers over Standard Prime Fields

Modular multiplication is the most time critical component in the construction of elliptic curve point multiplication in projective coordinates. One of the optimization techniques is by choosing a prime modulus p of special structure (very close to a power of 2) called pseudo-Mersenne primes, which can reduce the computational complexity of the reduction stage in a modular multiplication operation. In this regard NIST recommends five prime fields [16] for different levels of security given in Table 2.4.