# DESIGN AND EVALUATION OF AN ENERGY EFFICIENT FREQUENCY ADAPTIVE ROUTER

Feng Guo

#### This Dissertation is submitted to Dublin City University in Candidacy for the Degree of Doctor of Philosophy

BY THE SCHOOL OF ELECTRONIC ENGINEERING SUPERVISOR: DR XIAOJUN WANG

JUNE 2016

#### Declaration

I hereby certify that this material, which I now submit for assessment on the programme of study leading to the award of Ph.D is entirely my own work, that I have exercised reasonable care to ensure that the work is original, and does not to the best of my knowledge breach any law of copyright, and has not been taken from the work of others save and to the extent that such work has been cited and acknowledged within the text of my work.

Signed:

Candidate ID No.:

Date:

#### Abstract

Energy efficiency is becoming a prominent issue in ICT networks. Many approaches have been proposed to reduce the power consumption of ICT network devices. Among those green approaches, dynamic frequency scaling (DFS) offers an elegant solution for improving the energy efficiency of processors. To evaluate the impact of different DFS techniques on energy efficiency of real network devices, this work designs a prototype of a novel energy-aware Frequency Adaptive Router (FAR) that dynamically scales the operating frequency of core logic FPGA processor among five different processing capacities in response to traffic load, rather than leaving the network devices running on its maximum processing capacity all the time.

Three dynamic frequency adaptation control policies are introduced into the FAR to balance the trade-off between performance and power consumption. Based on statistics monitoring and preset thresholds, the proposed dynamic frequency adaptation control policies can manage the FAR to always operate at the lowest processing capacity required to handle instantaneous traffic load without affecting the quality of service (QoS). The implementation of these frequency adaptation control policies involves assessing an associated traffic throughput threshold beyond which the router will begin to lose packets for each of the five operating frequencies, and then adaptively scaling the operating frequency in response to the instantaneous traffic load to save energy without compromising end-to-end QoS.

The energy efficiency and performance of the FAR is evaluated at the five different operating frequencies with different number of active ports, traffic bit rates and packet sizes. The evaluation results show that when in idle state, the FAR can significantly save power of up to 52%. Experiments with synthetic traces indicate that 46% of power can be saved while maintaining required QoS. Similar results can be expected when these general power-saving principles are applied in future commercial routers.

#### Acknowledgements

This work is co-funded by the China Scholarship Council (No. 2010647020) and the European FP7 ECONET project (No. 258454). I would especially like to acknowledge my supervisor Dr Xiaojun Wang who have spent much time reading drafts of this thesis and offering insightful suggestions, which led me to improve this work. I sincerely acknowledge Dr Martin Collier and Dr Olga Ormond for their guidance, encouragement and constructive criticism throughout the ECONET project.

I would like to thank my colleagues and friends Xiaowei Ma, Xiangjun Shi and Wenliang Fu from Beijing Institute of Technology (BIT), and Jie Jin, Xing Zheng and Lianghua Li from Hangzhou Dianzi University (HDU) for having detailed NetFPGA hardware Verilog code discussions with me. I would also like to thank research interns Yashank Sakhardande from National Institute of Technology Karnataka (NITK), Tejas Patel from Vellore Institute of Technology (VIT), Kevin Pierrot, Clément Aillet and Simon Fétigny from Ecole Nationale Supérieure Electronique Electrotechnique Informatique Hydraulique Télécommunications (ENSEEIHT) for their assistance on experimental setup and power consumption measurements.

Finally, I would like to honor the memory of my grandfather Zhiqi Zhang who passed away last year.

## Contents

|   | Abs  | tract   |                          | iii |

|---|------|---------|--------------------------|-----|

|   | Ack  | nowled  | lgements                 | v   |

|   | List | of Tabl | es                       | ix  |

|   | List | of Figu | ures                     | xi  |

|   | List | of Abb  | reviations               | xv  |

| 1 | Intr | oductio | on                       | 1   |

|   | 1.1  | Resea   | rch Motivation           | 1   |

|   | 1.2  | Energ   | y Efficient Networking   | 5   |

|   | 1.3  | Scope   | and Objectives           | 8   |

|   | 1.4  | Contr   | ibution                  | 10  |

|   | 1.5  | Thesis  | Structure                | 12  |

| 2 | Rela | nted Wo | ork                      | 13  |

|   | 2.1  | Devic   | e Level                  | 14  |

|   |      | 2.1.1   | Sleep Mode               | 16  |

|   |      | 2.1.2   | Power Scaling            | 19  |

|   | 2.2  | Netwo   | ork Level                | 23  |

|   |      | 2.2.1   | Network Design           | 24  |

|   |      | 2.2.2   | Green Routing Algorithms | 29  |

|   | 2.3  | Summ    | nary                     | 32  |

| 3 | Arc  | hitectu | re of Reference Router and Frequency Adaptive Router     | 33 |

|---|------|---------|----------------------------------------------------------|----|

|   | 3.1  | The N   | letFPGA platform                                         | 34 |

|   | 3.2  | The N   | letFPGA Reference Router                                 | 36 |

|   |      | 3.2.1   | Receive Queues                                           | 37 |

|   |      | 3.2.2   | User Data Path                                           | 38 |

|   |      | 3.2.3   | Transmit Queues                                          | 41 |

|   | 3.3  | Frequ   | ency Adaptive Router                                     | 42 |

|   |      | 3.3.1   | The Frequency Division Module                            | 42 |

|   |      | 3.3.2   | The AFIFO Module                                         | 50 |

|   | 3.4  | Summ    | nary                                                     | 52 |

| 4 | Frec | quency  | Control Policies and System Models                       | 53 |

|   | 4.1  | Local   | Frequency Control Policies                               | 55 |

|   |      | 4.1.1   | Single Threshold Policy (STP)                            | 58 |

|   |      | 4.1.2   | Double Threshold Policy (DTP)                            | 60 |

|   |      | 4.1.3   | Packet Loss Aware Policy (PLAP)                          | 63 |

|   | 4.2  | Globa   | l Frequency Control Policies                             | 63 |

|   |      | 4.2.1   | Performance First Policy (PFP)                           | 65 |

|   |      | 4.2.2   | Power Saving First Policy (PSFP)                         | 65 |

|   |      | 4.2.3   | User Defined Policy (UDP)                                | 66 |

|   | 4.3  | Syster  | n Models                                                 | 67 |

|   |      | 4.3.1   | System Model of Reference Router                         | 67 |

|   |      | 4.3.2   | System Model of Frequency Adaptive Router                | 71 |

|   | 4.4  | Summ    | nary                                                     | 73 |

| 5 | Ene  | rgy Eff | iciency and Performance Evaluation of Frequency Adaptive |    |

|   | Rou  | ter     |                                                          | 74 |

|   | 5.1  | Evalu   | ation Metrics                                            | 75 |

|    |        | 5.1.1   | Energy Efficiency Metrics             | . 75  |

|----|--------|---------|---------------------------------------|-------|

|    |        | 5.1.2   | Performance Metrics                   | . 78  |

|    | 5.2    | Exper   | imental Setup                         | . 79  |

|    |        | 5.2.1   | Power Consumption Measurements        | . 80  |

|    |        | 5.2.2   | Performance Measurements              | . 83  |

|    | 5.3    | Fixed   | traffic experiments                   | . 86  |

|    |        | 5.3.1   | Quiescent power consumption           | . 86  |

|    |        | 5.3.2   | Power consumption under fixed traffic | . 89  |

|    |        | 5.3.3   | Peak measured throughput              | . 92  |

|    |        | 5.3.4   | Round trip time                       | . 93  |

|    |        | 5.3.5   | Packet loss rate                      | . 94  |

|    |        | 5.3.6   | Frequency adaptation transition time  | . 95  |

|    | 5.4    | Exper   | iments with synthetic traces          | . 100 |

|    | 5.5    | Netwo   | ork wide global green techniques      | . 103 |

|    | 5.6    | Summ    | nary                                  | . 106 |

| 6  | Con    | clusior | ns and Future Works                   | 108   |

|    | 6.1    | Concl   | usions                                | . 108 |

|    | 6.2    | Future  | e Works                               | . 110 |

| Α  | List   | of Pub  | lications                             | 111   |

| Re | eferer | nces    |                                       | 114   |

## **List of Tables**

| 1.1 | Annual energy consumption of major telecommunications              |    |

|-----|--------------------------------------------------------------------|----|

|     | companies worldwide                                                | 2  |

| 1.2 | Average energy price (Million per TWh in US dollar)                | 4  |

| 3.1 | DCM frequency divisors, corresponding DCM output frequencies       |    |

|     | and theoretical throughputs of RR                                  | 47 |

| 3.2 | Mapping between control inputs and selected clock output           | 50 |

| 3.3 | Frequency control register values and corresponding operating      |    |

|     | frequencies of core logic FPGA                                     | 50 |

| 4.1 | Packet loss rate of FAR under different sampling period at traffic |    |

|     | rate 6400 Mb/s                                                     | 58 |

| 4.2 | Frequencies, capacities and thresholds mapping table for STP       | 59 |

| 4.3 | Frequencies, capacities and thresholds mapping table for DTP       | 61 |

| 4.4 | Advantages and disadvantages for each frequency control policy     | 67 |

| 4.5 | Notations used for M/M/1/N queuing model                           | 69 |

| 4.6 | Performance characteristics in system model of Reference Router    | 71 |

| 4.7 | Performance characteristics in system model of Frequency Adaptive  |    |

|     | Router                                                             | 72 |

| 5.1 | Impact of operating frequency and number of active ports on power  |    |

|     | consumption of RR                                                  | 87 |

| 5.2 | Impact of operating frequency and number of active ports on power     |

|-----|-----------------------------------------------------------------------|

|     | consumption of FAR 87                                                 |

| 5.3 | Frequency adaptation transition time of FAR (from column to row) . 98 |

| 5.4 | Aggregate duration in each frequency mode                             |

| 5.5 | Average total power consumption for the day                           |

| 5.6 | Control policy for DFS, GTE and EPS implementation on FAR 106         |

| 5.7 | Summary of power consumption and performance comparisons              |

|     | between the Reference Router and Frequency Adaptive Router 107        |

# **List of Figures**

| 2.1  | Power management control flow [54]                                   | 17 |

|------|----------------------------------------------------------------------|----|

| 2.2  | Point-to-Point architecture in optical access networks               | 25 |

| 2.3  | Active optical network architecture in optical access networks       | 26 |

| 2.4  | Passive optical network architecture in optical access networks      | 27 |

| 2.5  | Difference between P2P and WDM                                       | 28 |

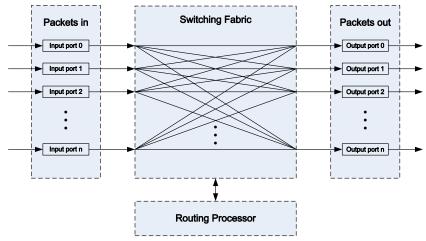

| 3.1  | Generic router architecture                                          | 34 |

| 3.2  | Major hardware components of the NetFPGA 1G board [110]              | 35 |

| 3.3  | NetFPGA hardware and host software interaction in the Reference      |    |

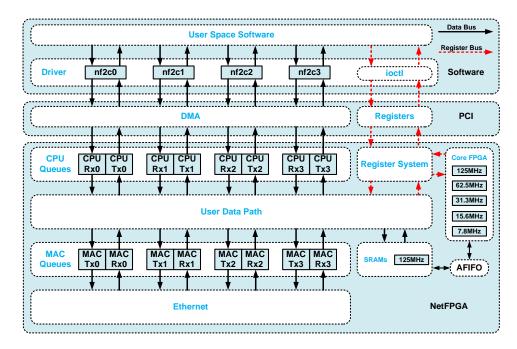

|      | Router                                                               | 36 |

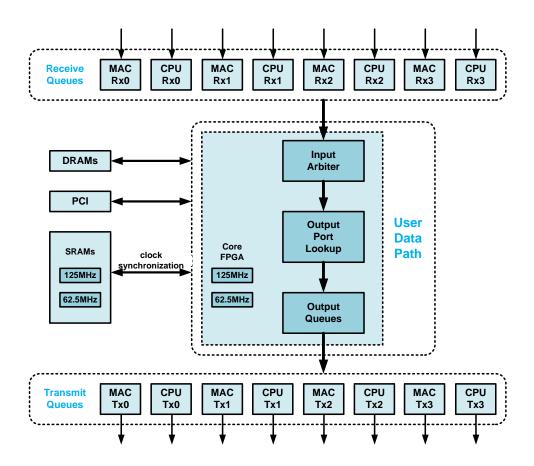

| 3.4  | The architecture of the Reference Router                             | 37 |

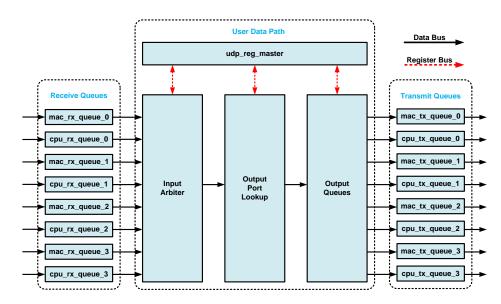

| 3.5  | Block diagram of data bus and register bus in the Reference Router . | 38 |

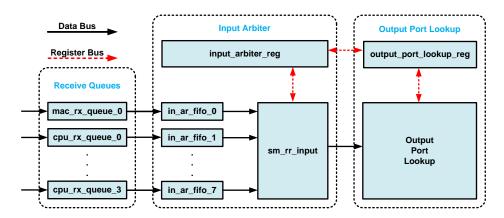

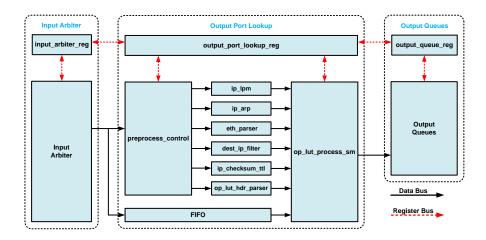

| 3.6  | Block diagram of the Input Arbiter module                            | 39 |

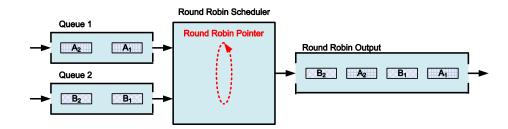

| 3.7  | The round robin scheduler                                            | 40 |

| 3.8  | Block diagram of the Output Port Lookup module                       | 41 |

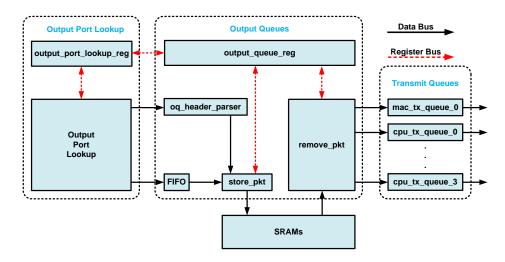

| 3.9  | Block diagram of the Output Queues module                            | 42 |

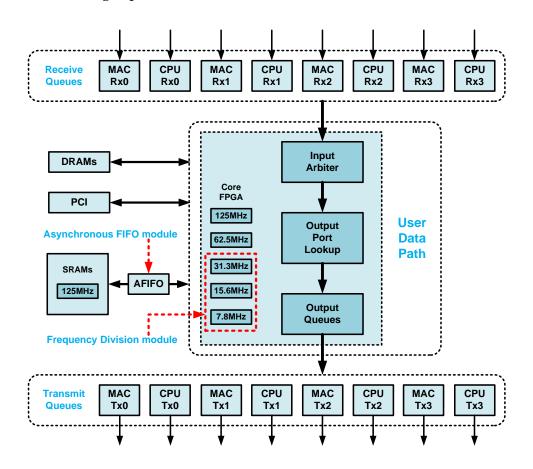

| 3.10 | The architecture of the Frequency Adaptive Router                    | 43 |

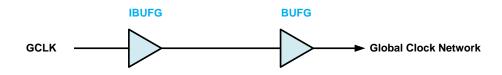

| 3.11 | A GCLK fed into a low-skew global clock network through an           |    |

|      | IBUFG and a BUFG [113]                                               | 43 |

| 3.12 | A GCLK fed into a low-skew global clock network through an           |    |

|      | IBUFG, a DCM and a BUFG [113]                                        | 44 |

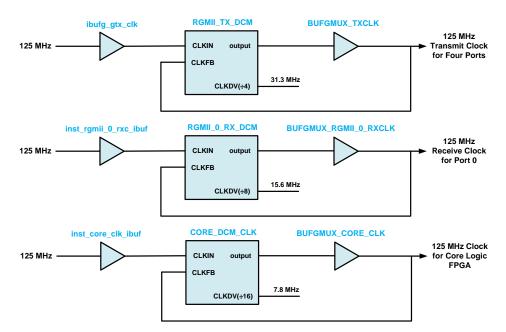

| 3.13 | Global clock design of the Reference Router                         | 45 |

|------|---------------------------------------------------------------------|----|

| 3.14 | Dividing source clock using the DCM                                 | 46 |

| 3.15 | The linear relationship between the operating frequency and the     |    |

|      | theoretical throughput                                              | 46 |

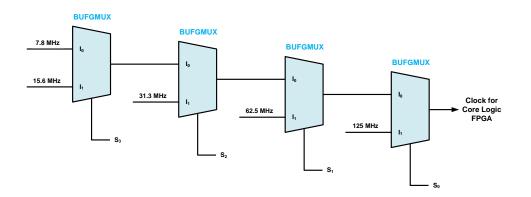

| 3.16 | Design details for generating three new frequencies in the          |    |

|      | Frequency Adaptive Router                                           | 48 |

| 3.17 | 5-to-1 cascaded clock multiplexer                                   | 49 |

| 3.18 | NetFPGA hardware and host software interaction in the Frequency     |    |

|      | Adaptive Router                                                     | 52 |

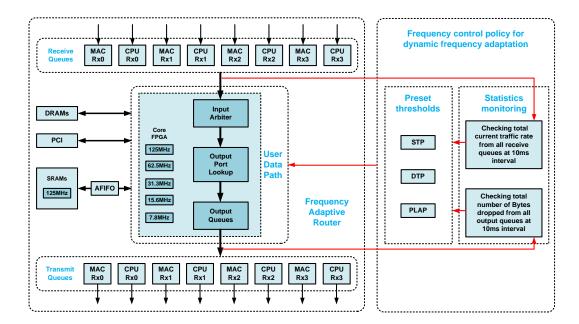

| 4.1  | Implementation of dynamic frequency adaptation on FAR               | 55 |

| 4.2  | Analysis of frequency adaptation transition time in local frequency |    |

|      | control policies                                                    | 56 |

| 4.3  | Thresholds of single threshold policy                               |    |

| 4.4  | Thresholds of double threshold policy                               |    |

| 4.5  | System model of the Reference Router                                | 67 |

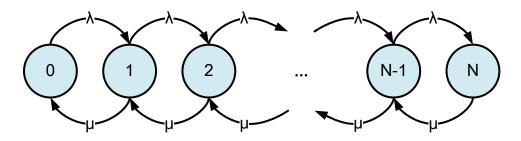

| 4.6  | M/M/1/N queuing model                                               | 68 |

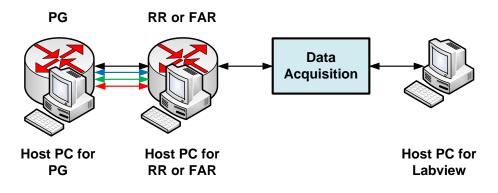

| 4.7  | Difference between the queuing system and the FIFO queue            | 70 |

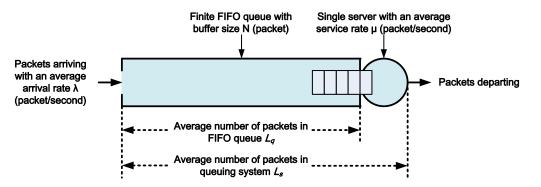

| 4.8  | System model of the Frequency Adaptive Router                       | 72 |

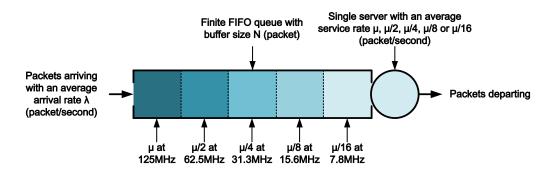

| 5.1  | Experimental setup                                                  | 80 |

| 5.2  | Coarse-grained and fine-grained power consumption measurement       | 00 |

| 0.2  | methods                                                             | 81 |

| 5.3  | Fine-grained power consumption measurement tools                    |    |

| 5.4  |                                                                     | 05 |

| 5.4  | Experimental setup for peak measured throughput and packet loss     | 8E |

|      | rate evaluation                                                     |    |

| 5.5  | Experimental setup for round trip time evaluation                   | 86 |

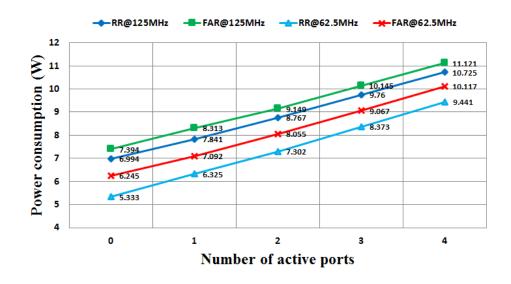

| 5.6  | Quiescent power consumption comparison between RR and FAR          |     |

|------|--------------------------------------------------------------------|-----|

|      | under different operating frequencies (125 MHz and 62.5 MHz) and   |     |

|      | different number of active ports (from 0 to 4)                     | 88  |

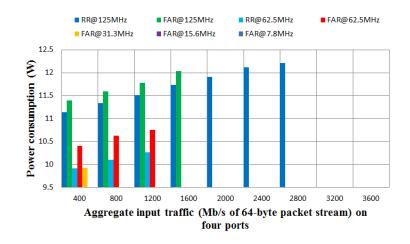

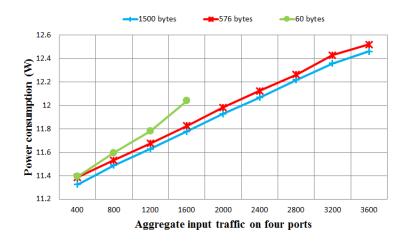

| 5.7  | Power consumption of RR and FAR under different frequencies and    |     |

|      | traffic bit rates with 64-byte packet stream                       | 90  |

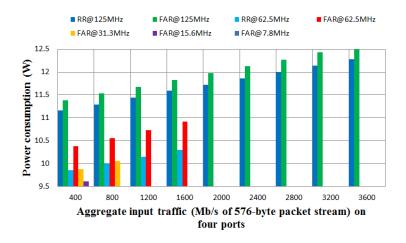

| 5.8  | Power consumption of RR and FAR under different frequencies and    |     |

|      | traffic bit rates with 576-byte packet stream                      | 90  |

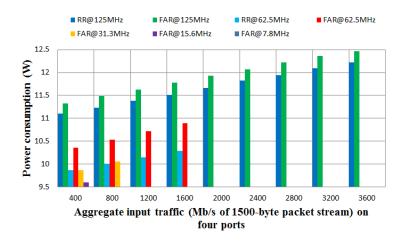

| 5.9  | Power consumption of RR and FAR under different frequencies and    |     |

|      | traffic bit rates with 1500-byte packet stream                     | 91  |

| 5.10 | Power consumption of FAR under different packet sizes and          |     |

|      | different traffic bit rates at 125 MHz                             | 91  |

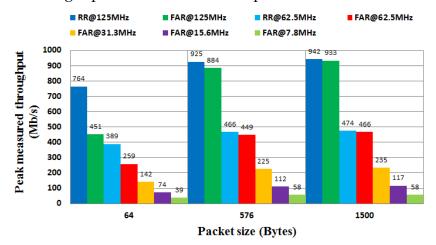

| 5.11 | Link capacity of RR and FAR under different frequencies and packet |     |

|      | sizes                                                              | 92  |

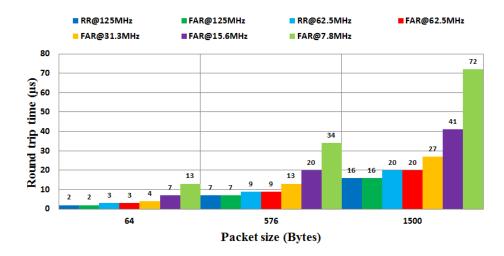

| 5.12 | Round trip time of RR and FAR under different frequencies and      |     |

|      | packet sizes                                                       | 93  |

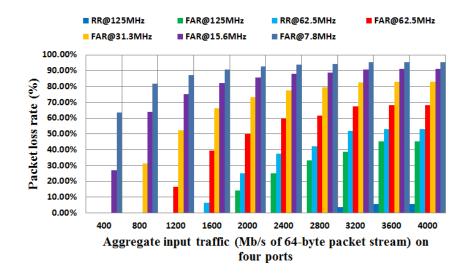

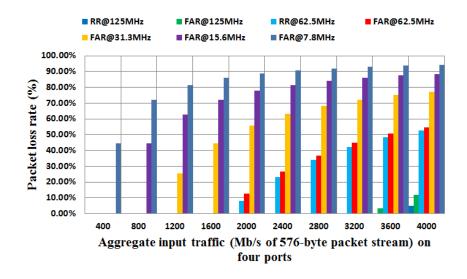

| 5.13 | Packet loss rate of RR and FAR under different frequencies and     |     |

|      | different traffic bit rates with 64-byte packet stream             | 94  |

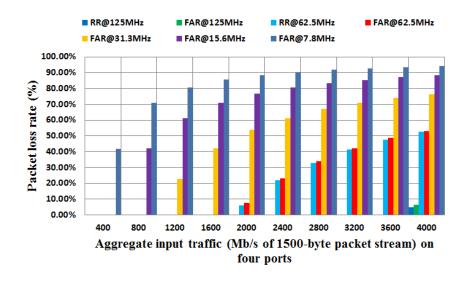

| 5.14 | Packet loss rate of RR and FAR under different frequencies and     |     |

|      | different traffic bit rates with 576-byte packet stream            | 95  |

| 5.15 | Packet loss rate of RR and FAR under different frequencies and     |     |

|      | different traffic bit rates with 1500-byte packet stream           | 95  |

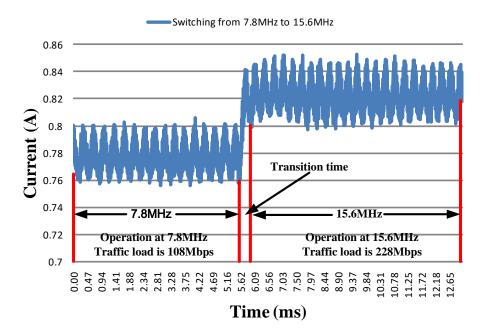

| 5.16 | An example of frequency adaptation transition time calculation     | 97  |

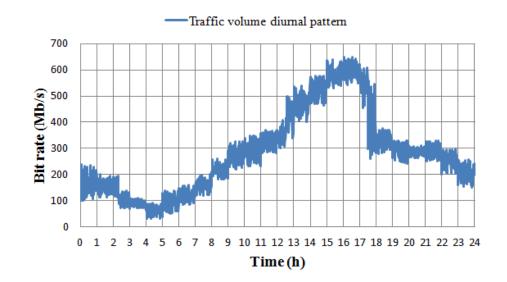

| 5.17 | Link traffic bit rate diurnal pattern                              | 100 |

| 5.18 | Operating frequency of RR and FAR corresponding to traffic trace   |     |

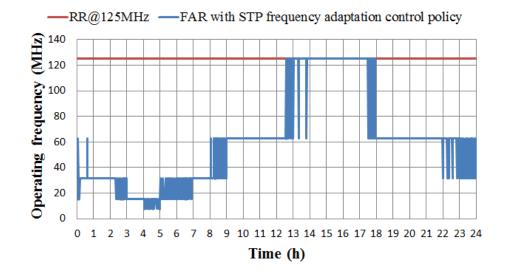

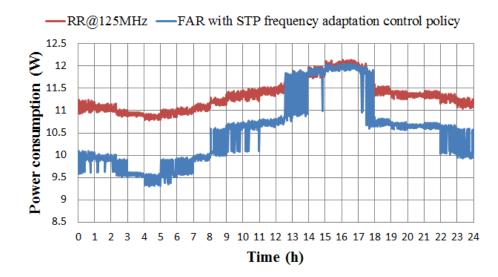

|      | in Figure 5.17                                                     | 101 |

| 5.19 | Power consumption of RR and FAR corresponding to traffic trace in  |     |

|      | Figure 5.17                                                        | 102 |

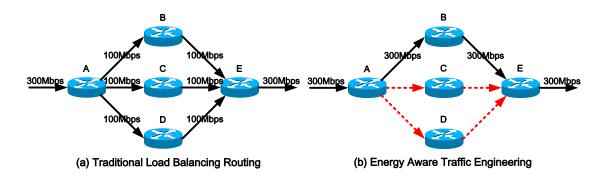

| 5.20 | Difference between traditional load balancing routing and energy |     |

|------|------------------------------------------------------------------|-----|

|      | aware traffic engineering                                        | 105 |

### List of Abbreviations

- AFIFO Asynchronous First In First Out

- ALR Adaptive Link Rate

- ARP Address Resolution Protocol

- BUFG Global clock BUFfer

- BUFGMUX Global clock BUFfer MUltipleXer

- CMOS Complementary Metal Oxide Semiconductor

- **CO**<sub>2</sub> **C**arbon **d**iOxide

- CPU Central Processing Unit

- DAQ Data AcQuisition

- DCM Digital CLock Manager

- DFS Dynamic Frequency Scaling

- DMA Direct Memory Access

- DNS Domain Name System

- **DTP** Double Threshold Policy

- **DVD** Digital Versatile Disk

- **DVFS** Dynamic Voltage and Frequency Scaling

- EC European Commission

- EMAC Ethernet Media Access Controller

- EPS Ethernet Port Shutdown

- ETSI European Telecommunications Standards Institute

- EU European Union

- FAR Frequency Adaptive Router

- FCFS First Come First Served

- FIFO First In First Out

- FPGA Field Programmable Gate Array

- FTP File Transfer Protocol

- GAL Green Abstract Layer

- GCLK Global CLocK input pad

- GND GrouND

- **GTE** Green Traffic Engineering

- HTTP HyperText Transfer Protocol

- **IBUFG** Global Input clock **BUF**fer

- ICMP Internet Control Message Protocol

- ICT Information and Communications Technology

- **IP** Internet **P**rotocol

- LPI Low Power Idle

- MAC Media Access Control

- NGN Next Generation Networks

- **NI** National Instruments

- **OSPF** Open Shortest Path First

- PC Personal Computer

- PCI Peripheral Component Interconnect

- PG Packet Generator

- **PLAP** Packet Loss Aware Policy

- **PON** Passive Optical Network

- **QoS Quality of Service**

- **RAM** Random Access Memory

- **RR** Reference Router

- **RTT** Round Trip Time

- **SNMP** Simple Network Management Protocol

- **STP** Single Threshold Policy

- TCP Transmission Control Protocol

- TWh Tara Watt hour

- UDP User Datagram Protocol

- USB Universal Serial Bus

- WDM Wavelength-Division Multiplexing

## Chapter 1

## Introduction

#### 1.1 Research Motivation

Traditionally, network performance is measured using metrics including bandwidth, throughput, latency, jitter and error rate. These parameters are the primary concern for network designers and manufacturers, and optimized at every step of the design and manufacture process to enhance user experience. While energy consumption, energy cost, greenhouse gas emissions and other metrics were previously brushed aside.

Recently, reducing energy consumption is universally recognized as equally important as performance improvement [1]. This was motivated by economics to reduce power cost mainly for operators but also for users facing increasing energy price and network traffic, while still maintaining end-to-end quality of service (QoS). This was also motivated by environment protection to decrease resource wastage and greenhouse gas emissions by 20% by 2020 from European Union (EU) '20-20-20' targets launched by European Commission (EC) [2].

The 21st century is in an era of information explosion. As the sharp increase in Internet traffic, broadband accesses, complex services and end users, energy consumption in ICT industry is increasing exponentially at an alarming rate. A detailed report [3] estimated that a huge increase in overall network power consumption is predicted for European Internet Service Providers (ISPs) from 21.4 terawatt hours (TWh) in 2010 to 35.8 TWh in 2020 if no green technologies are adopted. Such increase in power consumption could result in millions of energy costs. Table 1.1 summarizes the annual energy consumption of major telecommunications companies worldwide.

| Company                  | En                                                                                                                                                                  | ergy Co                                                                                                                                                                                                                                                                                                                                         | nsump                                                                                                                                                                                                   | tion (TV                                                                                                                                                                                                                              | Vh)                                                                                                                                                                                                                                                                   |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                     | 2011                                                                                                                                                                | 2012                                                                                                                                                                                                                                                                                                                                            | 2013                                                                                                                                                                                                    | 2014                                                                                                                                                                                                                                  | 2015                                                                                                                                                                                                                                                                  |

| British Telecom [4]      | 2.75                                                                                                                                                                | 2.67                                                                                                                                                                                                                                                                                                                                            | 2.61                                                                                                                                                                                                    | 2.52                                                                                                                                                                                                                                  | 2.41 <sup>1</sup>                                                                                                                                                                                                                                                     |

| Telecom Italia [5] [6]   | 1.93                                                                                                                                                                | 1.91                                                                                                                                                                                                                                                                                                                                            | 2.40                                                                                                                                                                                                    | 2.51                                                                                                                                                                                                                                  | 2.63                                                                                                                                                                                                                                                                  |

| Deutsche Telecom [7] [8] | 8.30                                                                                                                                                                | 8.40                                                                                                                                                                                                                                                                                                                                            | 8.60                                                                                                                                                                                                    | 9.10                                                                                                                                                                                                                                  | 8.90 <sup>2</sup>                                                                                                                                                                                                                                                     |

| Telefonica [9]           | -                                                                                                                                                                   | -                                                                                                                                                                                                                                                                                                                                               | -                                                                                                                                                                                                       | 6.35                                                                                                                                                                                                                                  | 6.43                                                                                                                                                                                                                                                                  |

| France Telecom [10]      | 3.98                                                                                                                                                                | 4.16                                                                                                                                                                                                                                                                                                                                            | 4.31                                                                                                                                                                                                    | 4.22                                                                                                                                                                                                                                  | 4.45                                                                                                                                                                                                                                                                  |

| Verizon [11]             | 10.00                                                                                                                                                               | 10.47                                                                                                                                                                                                                                                                                                                                           | -                                                                                                                                                                                                       | -                                                                                                                                                                                                                                     | -                                                                                                                                                                                                                                                                     |

| AT&T [12]                | 14.10                                                                                                                                                               | 14.60                                                                                                                                                                                                                                                                                                                                           | 14.80                                                                                                                                                                                                   | 14.90                                                                                                                                                                                                                                 | 14.80                                                                                                                                                                                                                                                                 |

| NTT [13]                 | 5.66                                                                                                                                                                | 5.22                                                                                                                                                                                                                                                                                                                                            | 4.88                                                                                                                                                                                                    | 4.83                                                                                                                                                                                                                                  | 4.91 <sup>3</sup>                                                                                                                                                                                                                                                     |

| China Mobile [14] [15]   | 12.93                                                                                                                                                               | 14.30                                                                                                                                                                                                                                                                                                                                           | 15.06                                                                                                                                                                                                   | 17.18                                                                                                                                                                                                                                 | 20.09                                                                                                                                                                                                                                                                 |

|                          | Name<br>British Telecom [4]<br>Telecom Italia [5] [6]<br>Deutsche Telecom [7] [8]<br>Telefonica [9]<br>France Telecom [10]<br>Verizon [11]<br>AT&T [12]<br>NTT [13] | Name         2011           British Telecom [4]         2.75           Telecom Italia [5] [6]         1.93           Deutsche Telecom [7] [8]         8.30           Telefonica [9]         -           France Telecom [10]         3.98           Verizon [11]         10.00           AT&T [12]         14.10           NTT [13]         5.66 | Name20112012British Telecom [4]2.752.67Telecom Italia [5] [6]1.931.91Deutsche Telecom [7] [8]8.308.40Telefonica [9]France Telecom [10]3.984.16Verizon [11]10.0010.47AT&T [12]14.1014.60NTT [13]5.665.22 | Name201120122013British Telecom [4]2.752.672.61Telecom Italia [5] [6]1.931.912.40Deutsche Telecom [7] [8]8.308.408.60Telefonica [9]France Telecom [10]3.984.164.31Verizon [11]10.0010.47-AT&T [12]14.1014.6014.80NTT [13]5.665.224.88 | Name2011201220132014British Telecom [4]2.752.672.612.52Telecom Italia [5] [6]1.931.912.402.51Deutsche Telecom [7] [8]8.308.408.609.10Telefonica [9]6.35France Telecom [10]3.984.164.314.22Verizon [11]10.0010.47AT&T [12]14.1014.6014.8014.90NTT [13]5.665.224.884.83 |

Table 1.1: Annual energy consumption of major telecommunications companies

worldwide\_\_\_\_\_\_

In United Kingdom (UK), the energy consumption for British Telecom's network and estate in 2010 was 3.12 TWh in total [4], including 2,281 GWh energy consumption for maintaining networks, data centers and offices in UK, 417 GWh energy consumption by gas, heating oil and generator fuel in UK, and 425 GWh

<sup>&</sup>lt;sup>1</sup>British Telecom has monitored and regulated energy consumption using its network of around 79,000 smart meters to optimise energy efficiency across 3,850 of its sites by responding to operational needs, weather forecast information and the number of people in the building. The annual energy consumption kept decreasing from 2011 to 2015.

<sup>&</sup>lt;sup>2</sup>Due to the fact that Deutsche Telecom has made progress in energy efficiency including network migration to IP technology, improved network utilization, and consolidation of data centers, annual energy consumption slightly decreased by approximately 3% in 2015.

<sup>&</sup>lt;sup>3</sup>With the adoption of energy saving measures, NTT reduced its annual energy consumption in 2012, 2013 and 2014.

energy consumption in countries outside UK. To operate networks, data centers and offices, British Telecom was one of UK's largest energy consumers, with around 0.7% of the entire UK's energy consumption [16]. As indicated in [17], approximately 10% of the UK's entire energy consumption was related to ICT equipments.

In Italy, the energy consumption of Telecom Italia was 2.64 TWh in 2015, which was approximately 0.89% of Italy's entire energy consumption [6]. Compared to 2.51 TWh in 2014 and 1.93 TWh in 2011, it increased by 4.56% and 26.89% respectively [5]. In this energy consumption increase from 2011 to 2015, the energy consumption of network infrastructures is the major source of the energy consumption increase. The energy consumption of network infrastructures contributed 70%. While, data centers contributed 10% and other sources (e.g., offices, shops, etc.) contributed the remaining 20%.

In Germany, the energy consumption of Deutsche Telecom also followed an increasing trend from 2011 to 2014, except for a slight decrease in 2015. The energy consumption of Deutsche Telecom was 8.90 TWh in 2015 [8]. Compared to 8.30 TWh in 2011 [7], it increased by 6.74%. The Deutsche Telecom attributed this energy consumption increase to increasing transmission volumes and network expansions. In Spain, the energy consumption of Telefonica was 6.43 TWh in 2015, which was about 2.70% of Spain's entire energy consumption [9]. Compared to 6.35 TWh in 2014, it increased by 1.33%. In France, the energy consumption of France Telecom also increased from 3.98 TWh in 2011 to 4.45 TWh in 2015 [10].

Similar trends are observed in the rest of the world. In United States (US), an early work [18] investigated and examined annual energy usage for office and network equipments. This work also estimated that the total energy used by office and network equipments was 74 TWh, which was 2% of entire US's energy usage in 1999. In 2011, the energy consumption of Verizon (an American telecommunications company) was 10.00 TWh, which was about 0.24% of entire US's energy consumption [11]. The energy consumption of Verizon increased to 10.47 TWh in 2012. While, the energy consumption of AT&T (another American telecommunications company) was 14.60 TWh in 2012 [12], which was of the same magnitude as Verizon.

In Japan, the energy consumption for telecommunications was 42 TWh in 2004 [19], which was about 1% of the Japan's entire energy consumption and was about 4% of the Japan's electricity generation [20]. The energy consumption of NTT (a Japanese telecommunications company) was 4.91 TWh in 2015 [13], which was about 0.53% of Japan's entire energy consumption. In China, the energy consumption of China Mobile (a Chinese telecommunications company) has been consistent growth from 2011 to 2015. The energy consumption of China Mobile was 20.09 TWh in 2015 [15]. Compared to 12.93 TWh in 2011 [14], it increased by 35.63%.

Apart from total energy consumption increases, average energy price is also increasing in the meantime. Referred to the United States Energy Information Administration (EIA) agency, average energy price has increased with a high pace except for two slight decreases in 2012 and 2015. The average energy price increased from 99.0 million per TWh (in US dollar) in 2011 to 104.1 million per TWh in 2015. Table 1.2 summarizes average energy price from 2011 to 2015 [21]. The increasing of energy consumption and price are driving Internet Service Providers (ISPs) and telecommunications companies worldwide towards energy efficient networking.

Table 1.2: Average energy price (Million per TWh in US dollar)

| <u> </u>              | 1    |      | 1     |       |       |

|-----------------------|------|------|-------|-------|-------|

| Year                  | 2011 | 2012 | 2013  | 2014  | 2015  |

| Million per TWh in \$ | 99.0 | 98.4 | 101.0 | 104.4 | 104.1 |

On the other hand, carbon dioxide (CO<sub>2</sub>) emissions from the ICT industry should never be ignored [22]. In 2002, the Global e-Sustainability Initiative (GeSI) reported that global Telecommunications infrastructure and devices contributed 152 million tons CO<sub>2</sub> emissions, including 66 million tons from mobile networks, 64 million tons from fixed narrowband networks, 18 million tons from Telecommunications devices and 4 million tons from fixed broadband networks [3]. From 2002, Telecommunications CO<sub>2</sub> emissions have grown from 152 million tons in 2002 to 300 million tons in 2007. The GeSI also estimated that the CO<sub>2</sub> emissions of global Telecommunications infrastructure and devices will be approximately 349 million tons in 2020, including 179 million tons from mobile networks, 70 million tons from fixed narrowband networks, 51 million tons from Telecommunications devices and 49 million tons from fixed broadband networks [3].

In 2007, Gartner estimated that the ICT industry contributed about 2% of global  $CO_2$  emissions [23]. This work also indicated that the approximately 2% of global  $CO_2$  emissions that the ICT industry contributed is equivalent to the entire airline industry. Such an unsustainable trend of the power consumption and the  $CO_2$  emissions in the ICT industry should be addressed seriously in order to reduce power consumption and  $CO_2$  emissions from growing ICT industry.

#### **1.2 Energy Efficient Networking**

In the late 20th and early 21st centuries, Internet traffic is witnessing an exponential growth in the face of technological and social change [24]. To keep pace with the traffic growth, network devices are designed to translate improvements in digital circuits and operating frequency into higher

performance, such as maximizing the routing capacity of network devices at the cost of the highest and constant power consumption.

Network traffic is very dynamic and the busy-hour traffic rate has always been much higher than the average traffic rate. The gap between peak and average traffic is growing further due to increased share of video streaming of the Internet traffic. The routing capacity of network devices is designed to accommodate peak rates rather than average rates. In backbone networks, the routing capacity is usually twice larger than rush-hour traffic volume to achieve minimum network delay and packet loss [25]. However, the peak rates only occur for a very small fraction of the time, so significant amount of power are wasted to keep the network always at full capacity. The work in [26] monitors Internet backbone networks has actually grown faster than Internet traffic in 2008. The average and peak link utilization on major backbone networks are approximately 29% and 43% respectively.

In ICT networks, traditional design of network devices tends to primarily emphasize network performance. Power consumption, while given some attention, failed to be recognized as an important part of a family of design metrics, along with performance, reliability, security, etc. As the performance has been always a predominant consideration, most network devices never vary their capacity when they are running, even if very little or no traffic data is involved. Such phenomenon without enough attention on power consumption has caused huge energy waste in ICT network infrastructures. Power consumption measurements in the work [27] show that a 1 Gb/s Ethernet link consumes approximately 4 W more power than a 100 Mbp/s Ethernet link, and a 10 Gb/s Ethernet link consumes even more power ranging from 10 W to 20 W. Power consumption of most Ethernet links is independent of their link utilization [27]. A fully utilized Ethernet link consumes almost the same amount of power as an idle Ethernet link [28]. Power consumption measurements in the work [29] show that the average Ethernet link utilization is ranging from 1% to 5%.

Performance should never be the sole focus. As energy and power issue comes to the forefront recently, future network devices should integrate more features and deliver higher performance within the same or even less energy budget. Otherwise, without green techniques adopted into ICT network infrastructures, energy inefficiency in roughly three billion Ethernet connections worldwide [30] could potentially lead to massive energy waste and millions of unnecessary energy costs.

With the development of Next Generation Networks (NGN), it is widely believed that energy efficiency should be taken into account as a prominent design metric in ICT network infrastructures. To reduce the energy consumption of ICT and the environmental impact of ICT, many approaches have been proposed towards ICT energy efficient networking. All shared the same common aim to achieve the lowest possible power consumption while not compromising the performance.

Efforts in these approaches can be divided into two categories: device level and network level. In networks, device level techniques aim to improve the energy efficiency of individual network devices (e.g., switches, routers, etc.). This is mostly achieved by adopting energy-saving modes when the network device is underutilized or improving the energy efficiency of hardware components. On the other hand, network level techniques aim to improving the energy efficiency of whole network systems. This is achieved by manipulating the energy profile of network components and consolidating network traffic.

#### **1.3** Scope and Objectives

The energy consumption of ICT network device has been growing at a fast pace over the past two decades. The typical router capacity is increased from 100 Gb/s in 2000 to 10 Tb/s in 2008 with energy consumption increasing from 1.7 KW to 50 KW [31]. ICT network devices consume significant energy even in the idle state. Given that typical router utilization are ranging from 20% to 50% in Internet Service Providers (ISPs) backbone, from 8% to 25% in enterprise networks and less than 1% in Local Area Networks (LANs) [32], the energy wastage is significant. Observation in the work [3] reported that, in the life time of the ICT network device, operating the device contributed 80% of the lifetime energy consumption, while manufacturing the device contributed the remaining 20%. Therefore, reducing the operating energy consumption of the ICT network device is worth the effort. Furthermore, it is also reported in the work [3] that processing bits in network devices and data centers contributed 63% of energy consumption in ICT, while transporting bits in telecommunications contributed the remaining 37%. Therefore, reducing processing per bit energy consumption in ICT network device is even more crucial.

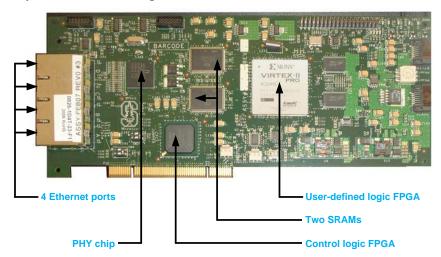

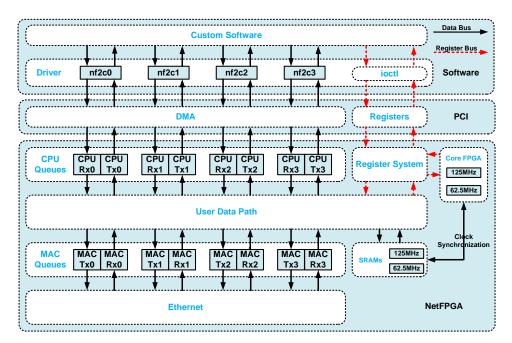

To reduce processing per bit energy consumption, the scope of this work is to design and develop an energy efficient network hardware router named the Frequency Adaptive Router (FAR), achieving energy proportionality between the router's energy consumption and the router's utilization. This work is validated on the NetFPGA 1G board [33] because it supports a community of open source hardware and software, and makes use of modular structure in the reference pipeline. Therefore, it is capable of providing a fast way to develop and experiment custom green mechanisms with low cost reconfigurable feature. This work develops and implements a fine-grained energy proportional technique on the NetFPGA, and examines the impact of various factors, including the operating frequency, the number of active Ethernet ports, the traffic bit rate and the packet size, on both the power consumption and the performance. The main objectives of this work are to address the following three challenges.

Many approaches have been proposed to improve the energy efficiency of ICT networks at various components levels. However, most of these approaches have contributed to the energy-saving solutions in simulated environments [34] [35]. Due to the fact that different energy states adaptation is not supported by most of current hardware coupled with compatibility issues, practical application of the proposed energy saving approaches in existing networks is still challenging.

Energy aware network device may suffer from long response time and more energy consumption during transitions of different energy states. Transitions of different energy states may lead to performance degradation (e.g., increasing packet loss, increasing network delay, etc.). Therefore, minimizing the overall energy consumption of network device and minimizing the overhead of transitions of different energy states are crucial in a parallel manner. Building hardware components to efficiently deal with the overhead of energy states transitions is another challenge.

The last challenge is achieving proportionality between energy consumption and device utilization. Achieving energy proportionality not only can reduce the energy consumption of network devices, but also can eliminate the demand for other complicated energy saving approaches [36].

#### 1.4 Contribution

The main contribution of this research is the design of a Frequency Adaptive Router, the exploration of frequency adaptation control policies, and the energy efficiency and performance evaluation of the Frequency Adaptive Router. This work mainly contributes in four aspects:

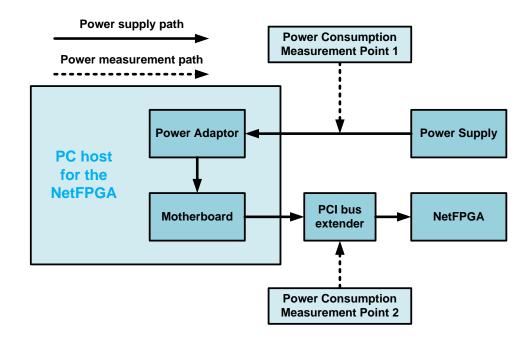

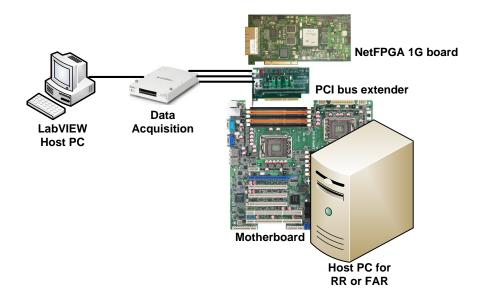

**Energy savings benchmarking.** Currently, switches and routers do not include comprehensive power consumption values. Most device specification sheets only report the maximum rated power [37] [38]. This information is insufficient to well understand the actual power consumption of a network device. As shown in the rest of this thesis, the actual power consumed by wired routers depends on various factors, such as: 1) operating frequency, 2) number of active Ethernet ports, 3) traffic bit rate and 4) packet size. Therefore, counting only the maximum rated power of the network device could grossly overestimate the actual energy consumption of the network device. This work introduces an accurate and fine-grained power consumption measurement method to measure the power consumption of peripheral component interconnect (PCI) based NetFPGA 1G router, which can be used to better quantify energy savings from the energy proportional technique on real network devices. Compared to the maximum rated power reported in the work [37] [38], this work measures real time power consumption of the NetFPGA router under different operating frequencies, number of active Ethernet ports, traffic bit rates and packet sizes.

**Frequency Adaptive Router.** Starting from the NetFPGA 1G Reference Router (RR), this work builds a dynamic frequency adaptive router (FAR) to develop and implement power scaling techniques on real network devices. When toggling the operating frequency of the NetFPGA core logic processor between 125MHz and

62.5MHz on the original RR, the frequency switching causes a board reset and all buffered packets are lost. Three additional operating frequency options, 31.3MHz, 15.6MHz and 7.8MHz, are added in the FAR for more finely tuned frequency switching without significant packet processing delay. The board reset problem is also eliminated. The FAR dynamically scales and tunes the operating frequency of the router in response to the traffic load it is currently handling, so that when the traffic load is low, the router can adaptively switch to an appropriate low routing capacity state to save power consumption. In ICT networks, peak traffic rate is much higher than average traffic rate. The Frequency Adaptive Router can operate at lower frequencies at off peak times to save power consumption. As shown in the rest of this thesis, compared to the RR in the work [33], the FAR consumes less quiescent power consumption by up to 52% and less total power consumption by up to 46%.

**Frequency Adaptation Control Policy.** To achieve energy efficiency and avoid compromising performance, a frequency adaptation control policy aims to offer the required performance with the lowest possible power consumption. Based on statistics monitoring and preset thresholds, three different dynamic frequency adaptation control policies are designed to determine when to initiate a frequency transition. The three dynamic frequency adaptation control policies are: Single Threshold Policy (STP), Double Threshold Policy (DTP) and Packet Loss Aware Policy (PLAP). Previous works [34] [35] have contributed to the energy-saving solutions in simulated environments. Compared to the simulation of the control policy in the work [34], this work implements the proposed frequency adaptation control policies directly in the FAR, providing more accurate and valid power consumption and performance evaluation results.

Hardware Acceleration. The dynamic frequency control policies of the FAR are directly implemented in hardware because software is slow compared to dedicated hardware. The dedicated hardware makes an enormous difference in the speed of time-sensitive operations, providing a significant statistics monitoring advantage over software. For example, frequency transition time on software implementation of a control policy consists of the delay in software reading buffer usage, operating frequency selection according to the control policy and setting the appropriate frequency control register, which involves communications between hardware and software through reading and writing registers. While, frequency transition time on hardware implementation of a control policy eliminates the delay in communications between hardware and software. Compared to the software implementation in the work [34] [39], this work reduces the frequency transition time by up to 85%.

#### **1.5** Thesis Structure

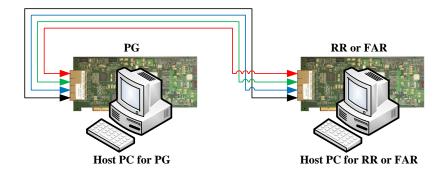

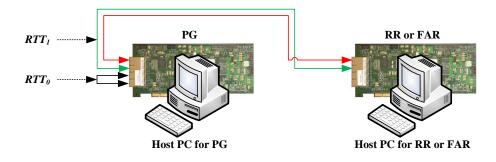

The rest of this thesis is organized as follows. Chapter 2 reviews the existing techniques related to energy efficient networking. Chapter 3 describes the design architecture of the NetFPGA Reference Router and the Frequency Adaptive Router. Chapter 4 explains the frequency adaptation control policies for the Frequency Adaptive Router, and the system models for the Reference Router and the Frequency Adaptive Router. Chapter 5 addresses the implementation details, describing the lab setup, the tools for power consumption measurements and performance measurements. The energy efficiency and the performance of the Frequency Adaptive Router are evaluated and analyzed in comparison with the Reference Router. Chapter 6 concludes the thesis.

## Chapter 2

## **Related Work**

Internet traffic has been witnessing a sky-rocketing growth over the past decade. To keep pace with such growth, it is even more compelling to reduce power consumption while managing massive increases in Internet traffic and networking hardware [40]. Economic reasons and environmental concerns on sustainable growth have created a demand for green communication networks. Many approaches have been proposed to manage energy and power issues to improve the energy efficiency of the ICT infrastructures in a variety of areas (e.g. wired networks, wireless networks, optical networks, smart grids, etc) [41] [42].

To improve the energy efficiency of network devices, Guapta et al. [43] proposed the sleep mode in green networking to place network interfaces and components of network devices to sleep when they are idle. This work also discussed main implementation challenges and expected benefits from the sleep mode. Since this work [43], many green approaches have been proposed and several literature surveys in various areas and domains of energy efficiency have been published [44] [45].

These green approaches can be mainly divided into green approaches in device level and green approaches in network level. The green approaches in device level make efforts to design low power consumption network equipment and improve the energy efficiency of the hardware using sleep mode functionality or power scaling capabilities. Device level techniques reduce power consumption of individual network devices (e.g., switches, routers, etc.) by adapting the power saving mode of various components of the devices (e.g., processors, memories, network interfaces, etc.). This is achieved in a localized manner by locally collected information.

On the other hand, the green approaches in network level focus on routing policies to reduce the network energy consumption, such as maximizing the number of network interfaces and components that can be put into sleep while maintaining the required quality of service. Network level techniques minimize power consumption of a network using global information, including the topology, the status of links, the traffic demands, the performance requirements and the power saving modes of all the devices within the network. This is achieved either in a centralized manner by collecting all the information at a single governor or in a distributed manner through network nodes cooperation.

#### 2.1 Device Level

Many approaches have been proposed to improve the energy efficiency of the network by re-engineering conventional network equipments and network protocols. Based on locally collected information, device level techniques for reducing the energy consumption can be divided into two categories: sleep mode and power scaling [46].

Sleep mode refers to a low power mode for electronic devices [47]. This mode can significantly reduce power consumption compared to leaving a device fully on all the time when the network presence of this device is not required [48]. In sleep mode, power is cut for unneeded subsystems and the RAMs are placed into a minimum power state, just sufficient to retain their data. Sleep mode is a promising technique in ICT green computing to save energy. In ICT green networking, only when there is no traffic to handle for an extended period of time can a router go to sleep.

Another energy saving technique is power scaling. It provides the ICT network devices the capability to dynamically scale into different processing states in response to instantaneous operational needs and traffic load. In power scaling category, Dynamic Voltage and Frequency Scaling (DVFS) has always been the king solution [49]. This fine-grained energy proportional technique allows the voltage supply and/or the clock speed of a processor to meet the instantaneous operational need of the operation being performed, while minimizing power draw and heat dissipation.

Once the power scaling capabilities are provided in a router, appropriate power scaling control policy must be introduced to balance the trade-off between performance and power consumption. An effective power scaling control policy should manage the router to always operate at the lowest appropriate routing capacity to handle the instantaneous traffic without affecting the performance as perceived by the user. The control policy must be effective and simple to be directly implemented inside a network router. Significant increases to packet loss and delay should be avoided when implementing a power scaling control policy, as this could degrade user experience.

#### 2.1.1 Sleep Mode

Energy Star standard [50] [51] was launched in 1992 and was designed to improve energy efficiency in computers, servers, appliance, heating and cooling systems, etc. This promoted the widespread adoption of sleep mode in electronic devices [52]. Sleep mode refers to a low power mode for the electronic devices and this mode can save significant power consumption compared to leaving a device fully on [53]. When placed in sleep mode, power was cut for unneeded subsystems entering into a very low power state.

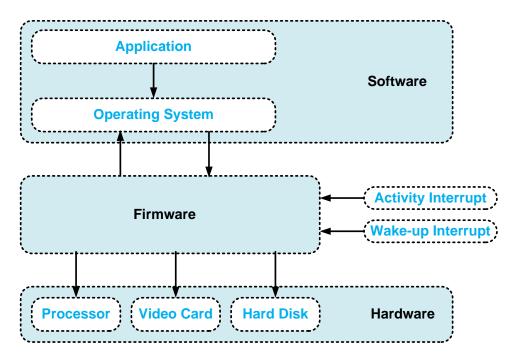

In green computing, power management first appeared in laptop computers to extend battery life for mobile users [54]. Figure 2.1 demonstrates the power management control flow. The firmware periodically sends request signals to the operating system to start power management. If the power management is enabled on the operating system and no activity is detected from the application, the operating system sends a responding signal back to the firmware to start a power management inactivity timer. After a specified time with no activity detected, the firmware initiates power management by sending signals to the hardware (e.g., the processor, the video card, the hard disk, etc). The corresponding hardware is then placed into a low power operating mode. An activity interrupt or a wake-up interrupt could lead the firmware to send signals to corresponding hardware to get back to an active and powered mode of operation. There are two modes of operation for the power management of the hardware, a slow clock mode and a stopped clock mode. The slow clock mode reduces speed of operation for the hardware with reduced power consumption. While, the stopped clock mode turns the hardware almost completely off and only an interrupt can cause a restart of the hardware.

Figure 2.1: Power management control flow [54]

In green networking, sleep mode is based on similar power management primitives in green computing, which allows network devices or part of them turning themselves almost completely off, while all their functionalities are frozen. Compared to idle state, sleep mode refers to a deeper idle state characterized by more power savings but longer wake-up time. There are challenges to applying sleep mode in network devices because it takes more time and power to transition between the *on* and *off* state. Predicting the *off* period and adapting to the appropriate state is still difficult. For instance, when a network device or a part of it is placed into sleep mode, its applications and services stop working and its network connectivity is lost. As a result, the network device loses its network presence so that it can not maintain network connectivity and respond to its applications or services. In addition, when the network device wakes up, it takes longer time to re-initialize its applications and services by sending its signalling traffic.

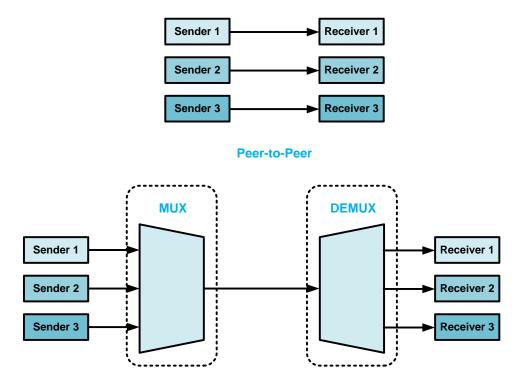

To introduce sleep mode into green networking with less overheads, Christensen et al. [54] proposed to use a sleep proxy for a network host and to integrate power management functions into TCP/IP and network applications. TCP/IP connections follow a client-server (CS) architecture. For peer-to-peer (P2P) connections, one peer acts as the client, the other peer acts as the server. A server can listen to requests from multiple connected clients. When a client request is detected at the server, a three-way handshake is initiated to establish a connection. When the connection is established, data can be transferred from a client to a server or a server to a client. The sleep proxy is designed to handle TCP/IP connections on behalf of the sleeping hosts allowing a safe sleep of the network hosts maintaining network presence through the proxy while at sleep.

In their follow-on work, Christensen et al. [28] investigated network traffic on several heavy-loaded computers in a university campus and results show that even the heavy-loaded computers still have many hours of idle time per day during which they can be placed into sleep mode. This work developed a proxying Ethernet adapter which can handle routine protocol messages without waking-up a desktop computer. The proxying Ethernet adapter can also wake-up the sleeping computer if needed.

An energy-efficient network device should be energy proportional to its actual needs. An idle or lightly utilized PC, Ethernet link or switch should not consume the same power as heavily utilized ones. Gunaratne et al. [27] developed several methods to reduce energy consumption of PCs, Ethernet links, and switches. These methods are achieved by supporting centralized proxying and control for discovery protocols, and disabling unused network devices in the routing path.

Most Ethernet connected network devices are fully powered on all the time to maintaining their network connectivity. Nordman et al. [55] developed a power management proxy to enable PC power management in network host PCs. The power management proxy is a low-powered entity that maintains full network presence for a sleeping high-powered network device. Their proposed proxy is able to bring powered down network host PCs back into a fully powered on state with reliable wake-up operations.

Gupta et al. [56] proposed dynamic Ethernet link shutdown to reduce power consumption on Ethernet links. This work uses buffer occupancy, the behavior of previous packet arrival times and a configurable maximum bounded delay to make decisions for dynamic Ethernet link shutdown. Simulation results using a synthetic traffic generator show that power savings can be achieved with little noticeable impact on network delay and packet loss.

#### 2.1.2 Power Scaling

In addition to sleep mode, power scaling [57] [58] can also be used to improve the energy efficiency of network hardware. Power scaling capabilities allow dynamically reducing the working speed of processing engines or link interfaces. The power scaling is usually accomplished by adopting two basic techniques: Low Power Idle (LPI) and adaptive performance scaling. The former forces links or processing engines to enter low-power states when not sending or processing packets and quickly switch to a high-power state when sending one or more packets. The latter allows dynamically modulating the capacity of a link or a processing engine in order to meet traffic load and service requirements. These techniques are not exclusive and can be jointly adopted in order to adapt system performance to current workload requirements. Scaling the working speed of processing engines or link interfaces as a function of user demand can save less power compared to sleep mode, but it has less wake-up time and less performance impact to a user.

Nedevschi [59] firstly proposed to support such energy-aware capabilities with a special reference to the Low Power Idle (LPI) with I/O traffic handling mechanisms, able to shape traffic profiles in order to optimally exploit LPI and adaptive performance scaling. For example, an I/O traffic handling mechanism based on a simple polling policy well suits an optimal use of LPI. An optimization policy is generally needed to configure and control the usage of energy-aware capabilities and states with respect to the estimated workload and service requirements. Regarding the optimization policy, several methods have been proposed in order to estimate the current workload and to optimally control the trade-off between performance and energy consumption in the computing system field [60] [61]. These methods range among predictive techniques [62] and dynamic schemes [63] [64], which were studied for disk drives [65], processors [66] [67], and other components [68].

Christensen et al. [27] has specifically addressed how to reduce the direct energy use of Ethernet links, and has contributed to the development of the IEEE 802.3az energy-efficient Ethernet (EEE) standard. The work [27] first explored the adaptive link rate (ALR) for Ethernet so that an Ethernet link can be operated at a lower data rate during periods of low utilization and at high data rate only for high utilization periods. Most Ethernet links are highly over-provisioned, with ALR most Ethernet links could operate at a lower bit rate and thus reduce energy consumption compared to operation at a higher bit rate all the time [69]. The auto-negotiation scheme in the 802.3 standard [70] takes about 100 ms to change data rates at a 1 Gb/s link data rate. Gunaratne et al. [69] proposed the ALR that allows the speed of network links to be changed by adaptively switching to different processing states in response to the amount of data that is being transmitted. The transition time of changing data rates in the ALR can be significantly reduced to 1 ms through a newly-defined handshake mechanism. Later on, by combining the schemes of LPI and ALR, the IEEE 802.3az EEE standard [30] is proposed. The LPI specified in the IEEE 802.3az EEE standard currently allows a 10 Gb/s link to wake up in less than 3 us.

The IEEE 802.3az EEE standard [30] can be also used in smart grid. As described in the IEEE 802.3az EEE standard, the EEE uses Low Power Idle to reduce the power consumption of a link when the link is idle. During the low-power mode, refresh signals are sent periodically to maintain alignment between the transmitter and the receiver [71]. For a low link utilization of 25%, results in the work [42] indicated that the EEE can reduce power consumption by 25%.

Bolla et al. [72] analyzed and empirically modeled the energy modulation capabilities of processing engines in Linux-based software routers equipped with general-purpose and multi-core processors that already include LPI and ALR primitives. The results obtained by evaluating several hardware architectures indicated that both technologies permit the trade-off between power consumption and network performance to scale almost linearly.

Bolla et al. [73] extended their approach by introducing a control framework for optimally tuning LPI mechanisms and adaptive performance scaling to statistically meet current traffic loads and service requirements. The results obtained on real traffic traces show that up to 60% power savings can be achieved. Previous work [59] especially focused on LPI primitives and performed a comprehensive study of the impact of transition times on LPI as a function of load. The results indicated that as the transition times shrink from the value of 10 ms to 1 ms and then further to 100 us, the time spent sleeping at 30 percent load goes from 0 at transition time of 10 ms to 40 percent when transition time is 1 ms, and to 70 percent when the transition happens in 100 us.

In the power scaling category, dynamic voltage scaling and dynamic frequency scaling are often used together as DVFS to conserve power [74] [75]. Dynamic voltage scaling [76] [77] is a power management technique in green ICT, where the voltage used in a unit is increased or decreased depending upon circumstances [78]. Decreasing voltage is to conserve power, particularly in laptops and other mobile devices, where energy comes from a limited battery. On the contrary, increasing voltage is to increase performance, or in rare cases, to increase reliability.

Dynamic frequency scaling [79] [80] is another power conservation technique that works on the same principles as dynamic voltage scaling. Dynamic frequency scaling technologies allow the clock speed of the processor to be dynamically changed to different processing states depending upon the traffic load. This allows the processor to meet the instantaneous performance needs of the operation being performed, while minimizing power draw and heat dissipation.

Meng et al. [34] proposed a multi-frequency scaling (MFS) scheme that examines buffer usage inside a network device so that the components of the device could dynamically scale its capacity according to its buffer occupancy. In the MFS scheme, a clock adapter is the hardware module for frequency scaling, and a multi-dual-threshold policy is adopted as the MFS control policy.

Pham et al. [39] [81] proposed a power scaling mechanism on the NetFPGA OpenFlow switch that can adapt the operating clock frequencies of the FPGA processor and the link rates of the four Ethernet ports based on the actual traffic load. The power can be saved by changing the clock frequency from 125 MHz to 3.9 MHz in combination with four possible operation modes on each Ethernet port (idle, 10 Mb/s, 100 Mb/s and 1 Gb/s).

### 2.2 Network Level

In previous section, device level techniques are reviewed. However, device level techniques can not guarantee the minimization of Internet power consumption. The device level techniques are used based on locally collected information without any node coordination. Currently, real networks are over-provisioned to accommodate the maximum expected traffic demands and over-redundant to deal with link and node failures. As a result, many network links are under-utilized and many network devices are constantly in operation with maximum capacity. Therefore, consolidating network traffic to place specific network nodes and links to a power saving mode is promising to improve the energy efficiency of networks. Network level techniques requires cooperations between network nodes to collect information on global network state, including the topology, the status of links, the traffic demands, the performance requirements and the power saving modes of all the devices within the networks. The network level techniques can be implemented both at the design stage (network design) and the operating stage (network routing). In this section,

network level techniques in these two different categories network design and network routing are reviewed.

#### 2.2.1 Network Design

Network design traditionally focuses on the minimization of network capital expenditure, including the device and installation costs of the network infrastructure [82]. However, as Internet traffic and energy costs are exponentially increasing, energy consumption is becoming a major issue for network operators for three main reasons, including significant increase in operational expenditure due to increasing traffic levels and energy costs, significant increase in CO<sub>2</sub> emissions and escalated heat dissipation problems [83]. As a result, improving the energy efficiency in network design has been paid much greater attention than before.

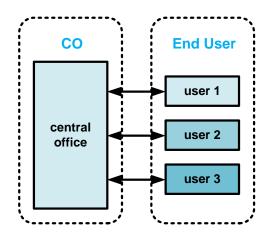

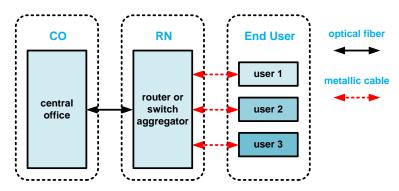

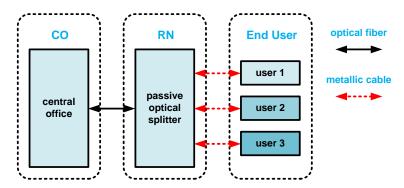

In digital communication networks, a core network is the backbone infrastructure of a network that usually interconnects metropolitan areas and may extend across different continents or nations. On the contrary, an access network is the last mile infrastructure of a network that connects the end users to their immediate core network. Internet can be divided into a core network and several access networks connected to the core network. Network devices in different network categories have different power consumption and performance. Understanding power consumption of different networking devices is the first step to identify where the most power savings can be achieved in ICT industry.

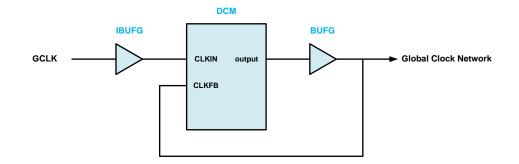

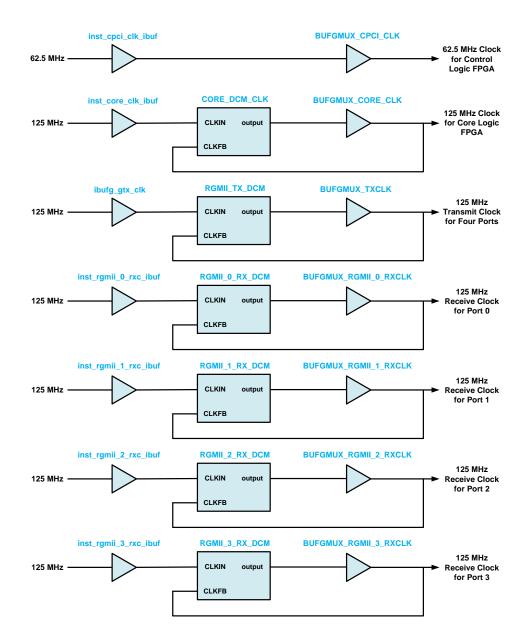

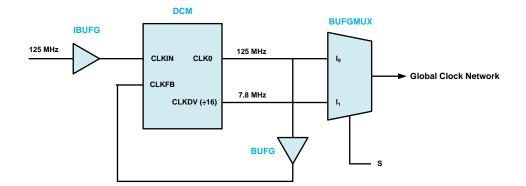

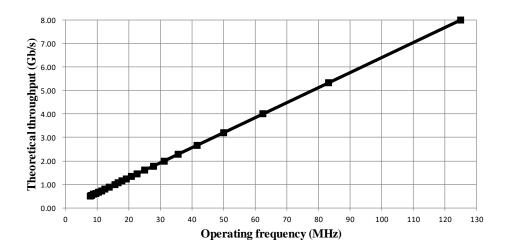

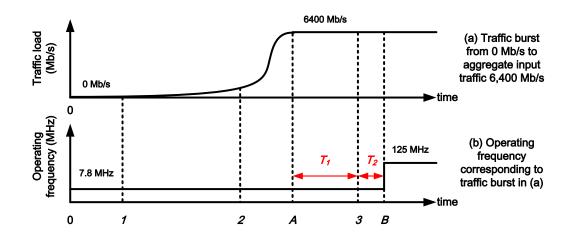

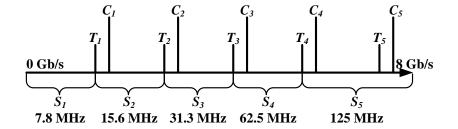

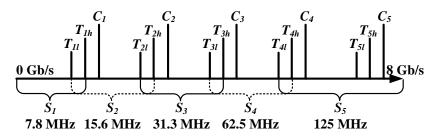

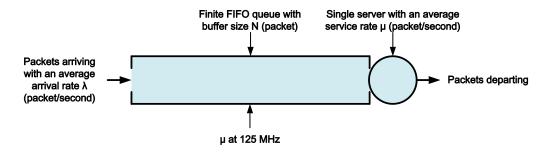

The majority of the energy used by the Internet today is consumed in the access networks, and this will continue to increase [84]. As access networks expand to deliver increasing amount of data traffic to increasing number of customers, efforts have been made to improve the energy efficiency of access networks. The access networks can be classified according to the type of the transmission medium (e.g., copper cables, optical fiber or wireless). Optical networks use optical signals over optical fibers for data transmission. Since the optical transmission provides high bandwidth, low signal attenuation, immunity to electromagnetic interference, low energy consumption, etc, it has been widely spread over decades.