# ENERGY EFFICIENT ENABLING TECHNOLOGIES FOR SEMANTIC VIDEO PROCESSING ON MOBILE DEVICES

by

Daniel Larkin, B.Eng.

Submitted in partial fulfilment of the requirements for the Degree of Doctor of Philosophy

Dublin City University

School of Electronic Engineering

Supervisor: Prof. Noel E. O'Connor

September, 2008

I hereby certify that this material, which I now submit for assessment on the programme of study leading to the award of Doctor of Philosophy is entirely my own work, that I have exercised reasonable care to ensure that the work is original, and does not to the best of my knowledge breach any law of copyright, and has not been taken from the work of others save and to the extent that such work has been cited and acknowledged within the text of my work.

| Signed: |                           |

|---------|---------------------------|

|         | Daniel Larkin (Candidate) |

|         |                           |

| ID      |                           |

| ID:     |                           |

|         |                           |

|         |                           |

| Date:   |                           |

# **Table of Contents**

| Li | st of 1 | rigures       |                                                              | VII  |

|----|---------|---------------|--------------------------------------------------------------|------|

| Li | st of T | <b>Fables</b> |                                                              | xi   |

| Al | ostrac  | et            |                                                              | xii  |

| Li | st of A | Acronyı       | ms                                                           | xiv  |

| Li | st of l | Peer-Re       | eviewed Publications                                         | xvii |

| A  | cknow   | vledgem       | nents                                                        | xix  |

| 1  | Intr    | oductio       | n                                                            | 1    |

|    | 1.1     | The E         | mergence of Mobile Multimedia                                | 2    |

|    | 1.2     | Grand         | Challenges Facing Next Generation Mobile Multimedia          | 3    |

|    |         | 1.2.1         | Semantic Multimedia Processing                               | 3    |

|    |         | 1.2.2         | Multimedia Content Delivery to Mobile Devices                | 5    |

|    |         | 1.2.3         | Multimedia Processing on Resource Constrained Mobile Devices | 6    |

|    | 1.3     | Resear        | rch Motivation and Work Programme                            | 7    |

|    |         | 1.3.1         | Novel Face Detection and associated hardware acceleration    | 7    |

|    |         | 1.3.2         | Hardware Acceleration of Motion Estimation                   | 8    |

|    | 1.4     | Resear        | rch Objectives                                               | 9    |

|    | 1.5     | Thesis        | Structure                                                    | 9    |

|                        | 1.6  | Summ     | ary                                                     | 10  |

|------------------------|------|----------|---------------------------------------------------------|-----|

| 2 Technical Background |      |          | ackground                                               | 11  |

|                        | 2.1  | Digital  | l Video Compression                                     | 12  |

|                        |      | 2.1.1    | A Generic Video Compression System                      | 15  |

|                        |      | 2.1.2    | Semantic Video Object based Compression                 | 28  |

|                        |      | 2.1.3    | Image & Video Compression Standards                     | 32  |

|                        | 2.2  | Seman    | tic Video Object Segmentation                           | 37  |

|                        | 2.3  | Thesis   | Contributions in the Context of Video Object Processing | 38  |

|                        | 2.4  | Impler   | mentation Options                                       | 41  |

|                        |      | 2.4.1    | Summary of Implementation Options                       | 43  |

|                        | 2.5  | Energy   | Efficient Design Principles                             | 44  |

|                        |      | 2.5.1    | Low Power design techniques                             | 47  |

|                        |      | 2.5.2    | Summary of Low Power Design                             | 51  |

|                        | 2.6  | Conclu   | asions                                                  | 52  |

| 3                      | Face | e Detect | ion: A Review of Popular Approaches                     | 53  |

|                        | 3.1  | Face D   | Detection State of the Art Review                       | 55  |

|                        |      | 3.1.1    | Feature Extraction based face detection approaches      | 55  |

|                        |      | 3.1.2    | Appearance based face detection approaches              | 59  |

|                        |      | 3.1.3    | Prior art in hardware acceleration of face detection    | 69  |

|                        | 3.2  | Discus   | ssion: Suitable Algorithms for a Mobile Device          | 73  |

|                        | 3.3  | Funda    | mentals of Evolutionary Artificial Neural Networks      | 77  |

|                        |      | 3.3.1    | Artificial Neural Networks                              | 78  |

|                        |      | 3.3.2    | Genetic Algorithms                                      | 82  |

|                        |      | 3.3.3    | Evolutionary Artificial Neural Networks                 | 83  |

|                        |      | 3.3.4    | Neuro Evolution of Augmenting Topologies                | 88  |

|                        | 3.4  | Conclu   | asions                                                  | 90  |

| 4                      | A N  | ovel Fac | ce Detection Training Algorithm                         | 92  |

|                        | 4.1  | Trainir  | ng data preparation                                     | 92  |

|                        | 4.2  |          | based face detection training                           | 95  |

|                        | 4.3  | Trainir  | ng Runs and Parameter Selection                         | 102 |

|   |      | 4.3.1    | Non-Seeded Topology Training                                     | 106 |

|---|------|----------|------------------------------------------------------------------|-----|

|   |      | 4.3.2    | Seeded Topology Training                                         | 110 |

|   | 4.4  | Conclu   | asions on Training                                               | 120 |

|   | 4.5  | Future   | Work                                                             | 121 |

|   |      | 4.5.1    | Automatic Input/Feature Selection                                | 128 |

|   |      | 4.5.2    | Using Alternative Low-Level Features                             | 128 |

|   |      | 4.5.3    | Detection of Side Profile and Rotated Faces                      | 130 |

|   | 4.6  | Summa    | ary of Contributions                                             | 130 |

| 5 | Soft | ware In  | pplementation of Trained Face Detection EANN                     | 134 |

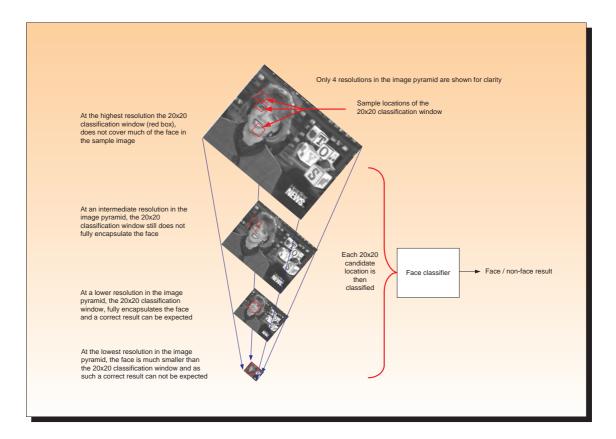

|   | 5.1  |          | Il Mode Face Detection Operation                                 | 134 |

|   |      | 5.1.1    | Merging detection results                                        | 136 |

|   | 5.2  | Profilii | ng of Normal Mode Face Detection Operation                       | 138 |

|   |      | 5.2.1    | Software Power & Energy Consumption                              | 140 |

|   | 5.3  | Softwa   | are Implementation & Algorithmic Optimisations                   | 141 |

|   | 5.4  | Results  | S                                                                | 145 |

|   |      | 5.4.1    | Evaluation on the BioID face database                            | 147 |

|   |      | 5.4.2    | Failure Analysis on the CMU/MIT face database                    | 150 |

|   | 5.5  | Future   | Work                                                             | 150 |

|   | 5.6  | Summa    | ary of Contributions                                             | 154 |

| 6 | EAN  | NN Haro  | dware Accelerator                                                | 155 |

|   | 6.1  |          | of the Art Hardware EANN Review                                  | 158 |

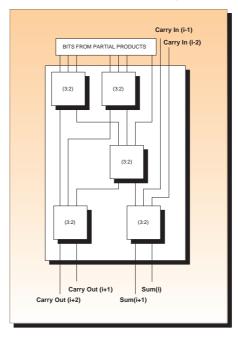

|   |      | 6.1.1    | Efficient Multiply Accumulation                                  | 159 |

|   |      | 6.1.2    | Activation Function Generator                                    | 159 |

|   |      | 6.1.3    | Number System and Precision Requirement Considerations           | 160 |

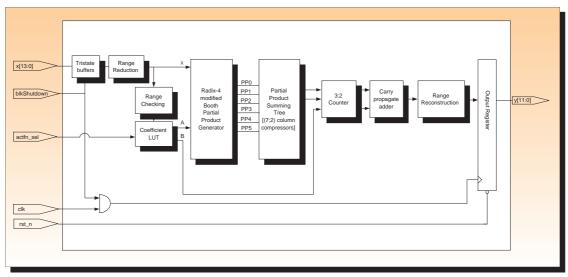

|   | 6.2  | Propos   | sed Hardware Architecture                                        | 162 |

|   | 6.3  | Implen   | nentation of Proposed Architecture                               | 165 |

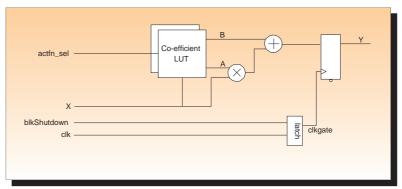

|   |      | 6.3.1    | Activation Function Generator                                    | 166 |

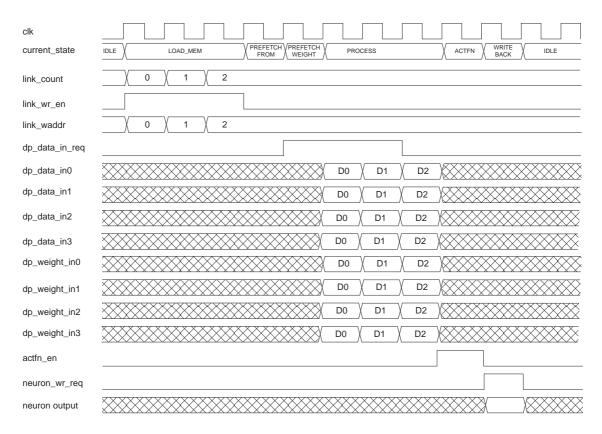

|   | 6.4  | Results  | s                                                                | 172 |

|   |      | 6.4.1    | Activation Function Results                                      | 173 |

|   |      | 6.4.2    | Hardware Implementation Results                                  | 174 |

|   |      | 6.4.3    | Benchmarking of Proposed Hardware Architecture against Prior Art | 178 |

|    | 6.5    | Future Work                                    | 181 |

|----|--------|------------------------------------------------|-----|

|    | 6.6    | Summary of Contributions                       | 182 |

| 7  | Bina   | ary Motion Estimation Hardware Accelerator     | 184 |

|    | 7.1    | State of the Art Review                        | 185 |

|    |        | 7.1.1 Binary Motion Estimation                 | 190 |

|    | 7.2    | Proposed Binary Motion Estimation Architecture | 193 |

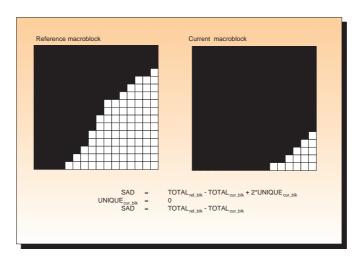

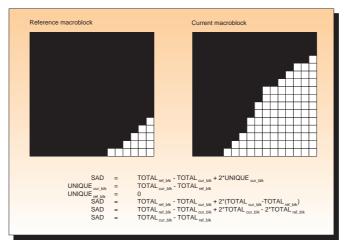

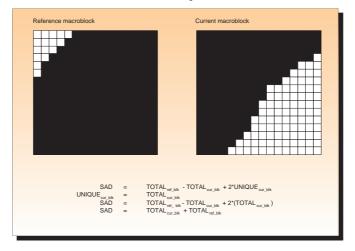

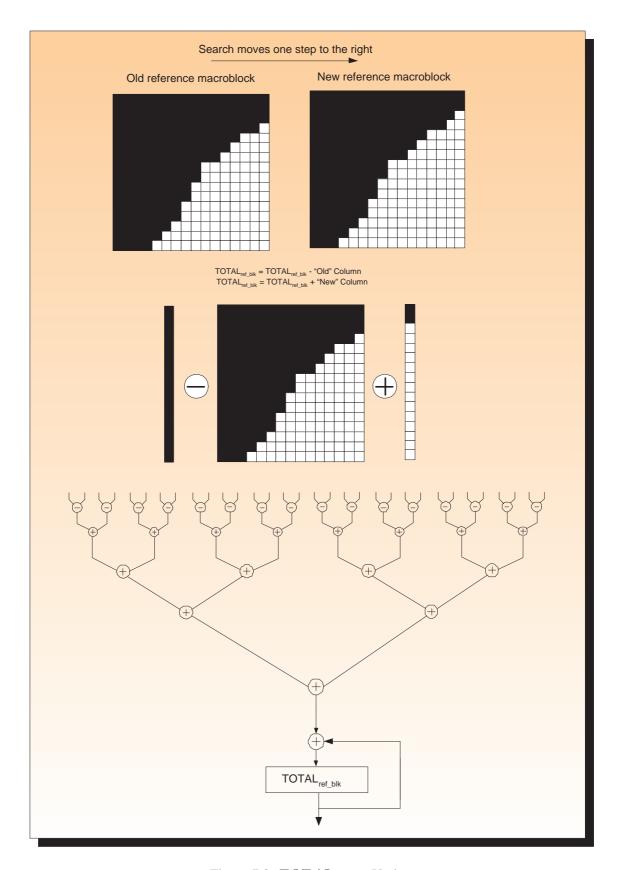

|    |        | 7.2.1 Reformulation of the Binary SAD Metric   | 194 |

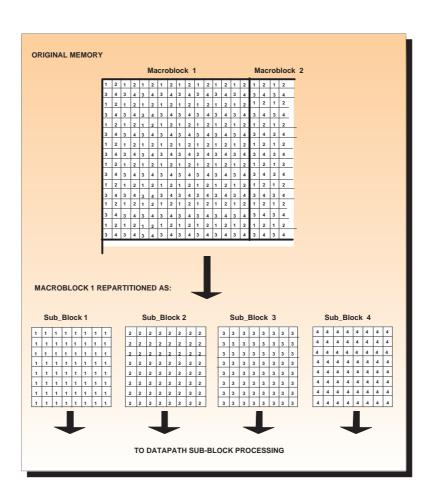

|    |        | 7.2.2 4xPE Block Matching Architecture         | 200 |

|    | 7.3    | Results                                        | 208 |

|    | 7.4    | Future Work                                    | 209 |

|    |        | 7.4.1 16XPE Block-Matching Architecture        | 210 |

|    |        | 7.4.2 Possible PE improvements                 | 210 |

|    | 7.5    | Summary of Contributions                       | 212 |

| 8  | Con    | clusions & Future Work                         | 214 |

|    | 8.1    | Motivation for Research – A Summary            | 214 |

|    | 8.2    | Summary of Thesis contributions                | 216 |

|    | 8.3    | A Vision for the Future                        | 218 |

| Bi | bliogr | raphy                                          | 220 |

# List of Figures

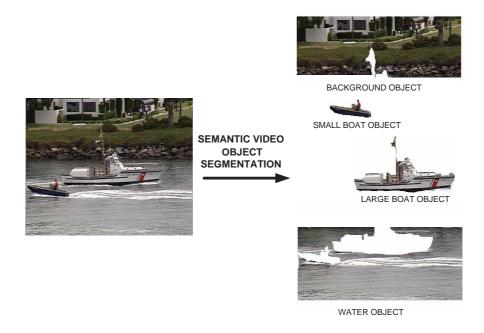

| 1.1  | Video scene decomposed into constituent semantic objects                     | 3  |

|------|------------------------------------------------------------------------------|----|

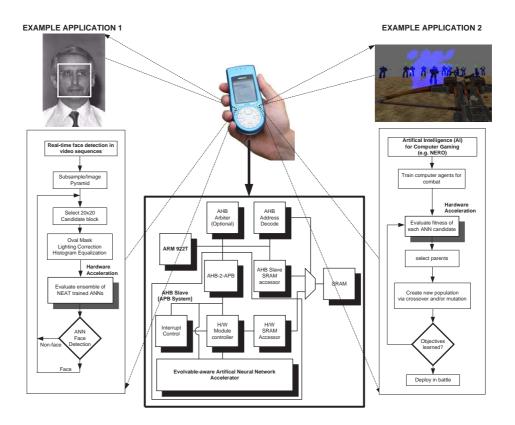

| 1.2  | Example of multiple applications leveraging a hardware ANN accelerator       | 8  |

| 2.1  | An example of a digital still image and video sequence                       | 13 |

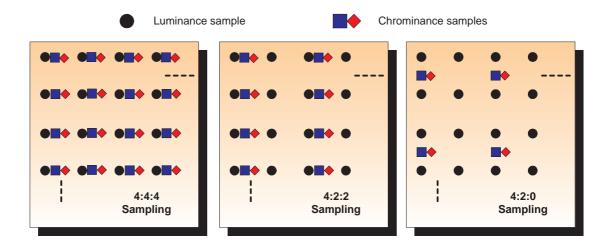

| 2.2  | Examples of $YC_bC_r$ sampling modes                                         | 13 |

| 2.3  | A Generic Video Encoder and Decoder                                          | 17 |

| 2.4  | Temporal Redundancy in Video Sequences                                       | 19 |

| 2.5  | Motion estimation taxonomy                                                   | 20 |

| 2.6  | Block sizes used in H.264 motion estimation)                                 | 21 |

| 2.7  | Probability of DCT coefficients being nonzero                                | 25 |

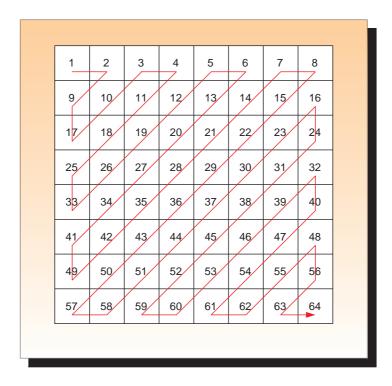

| 2.8  | Zig-zag scanning of quantised DCT coefficients                               | 27 |

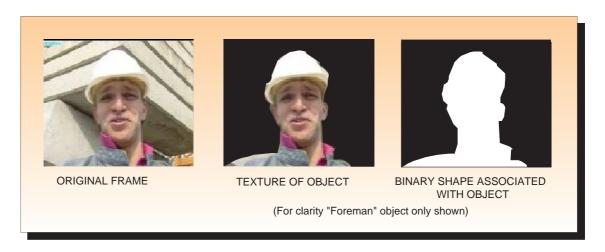

| 2.9  | MPEG-4 Video Objects                                                         | 29 |

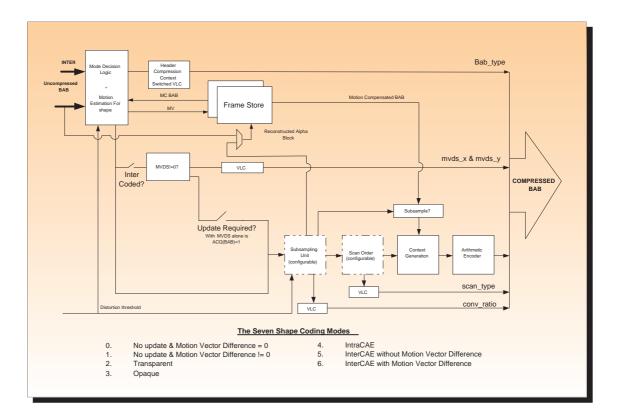

| 2.10 | MPEG-4 Binary Shape Encoder                                                  | 31 |

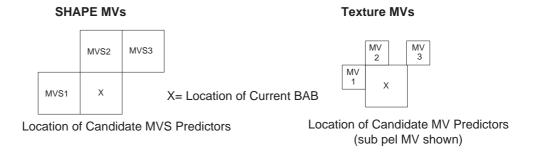

| 2.11 | Motion Vector difference for Shape                                           | 33 |

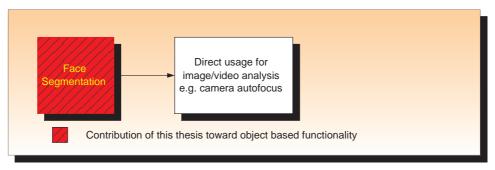

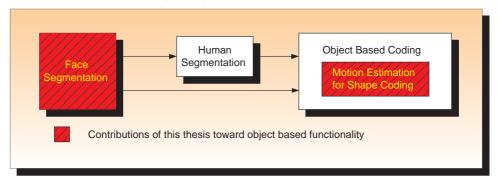

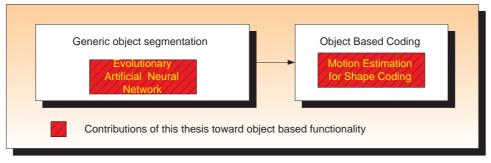

| 2.12 | Contributions of this Thesis in context of Video object-based functionality  | 39 |

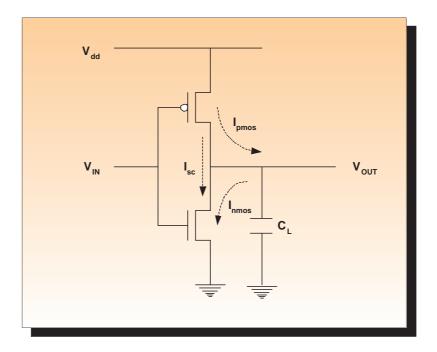

| 2.13 | Dynamic power loss in a CMOS Inverter                                        | 45 |

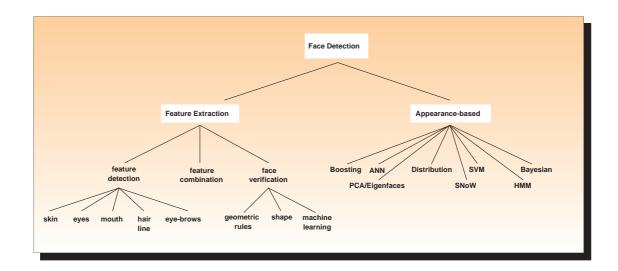

| 3.1  | Basic taxonomy of face detection algorithms                                  | 56 |

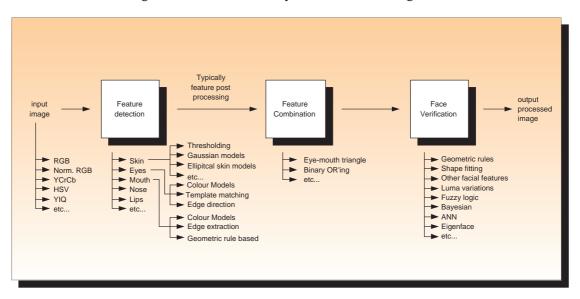

| 3.2  | Block diagram of a generic feature extraction based face detection algorithm | 56 |

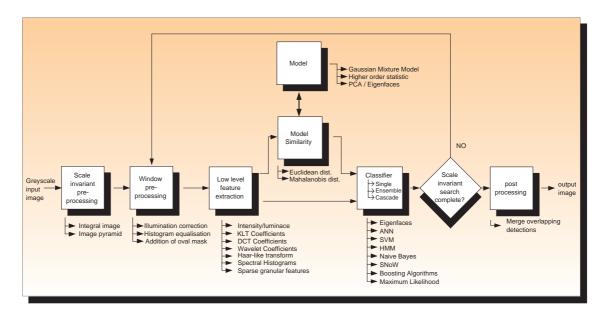

| 3.3  | Algorithmic options for appearance based face detection approaches           | 59 |

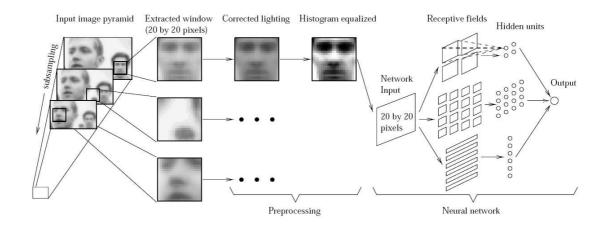

| 3.4  | Rowley's ANN based face detection algorithm                                  | 61 |

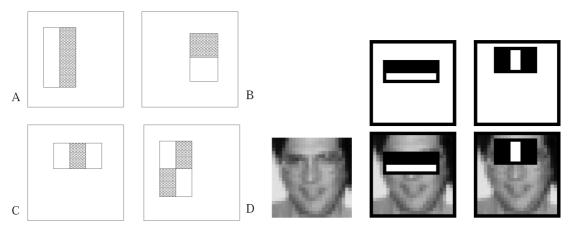

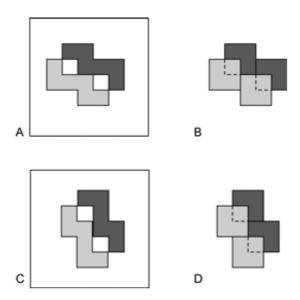

| 3.5  | Haar-like Features used in Viola & Jones Cascaded Adaboost algorithm             | 66  |

|------|----------------------------------------------------------------------------------|-----|

| 3.6  | Additional Haar features for rotation-invariant face detection                   | 67  |

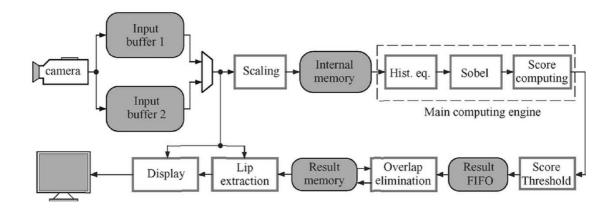

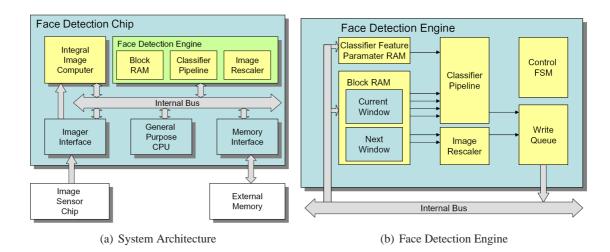

| 3.7  | System Architecture of Face Detection Algorithm proposed by Nguyen et al         | 71  |

| 3.8  | Face Detection Hardware Architecture Proposed by Yang et al                      | 73  |

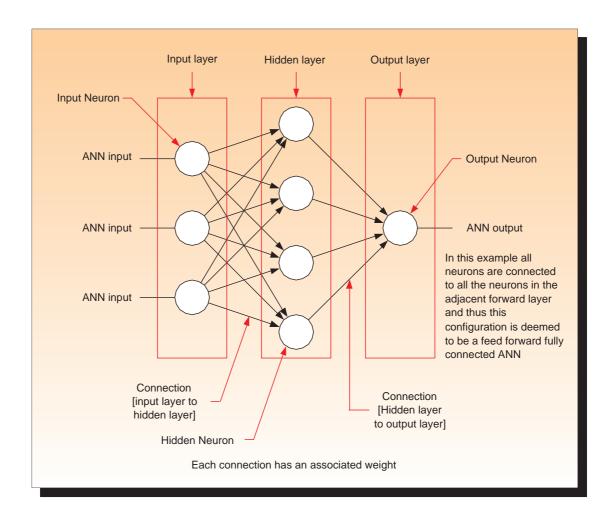

| 3.9  | Basic Terminology associated with Artificial Neural Networks                     | 79  |

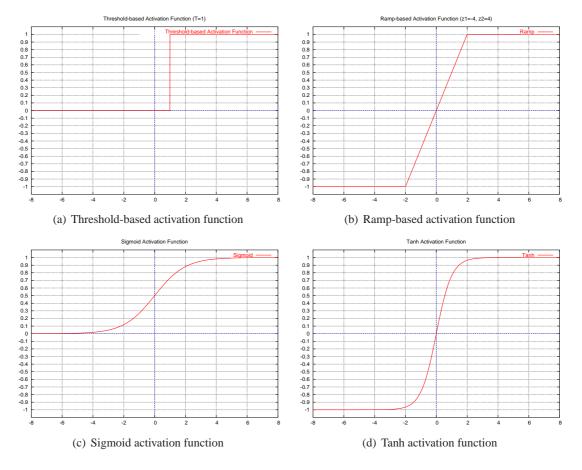

| 3.10 | Selection of popular activation functions                                        | 81  |

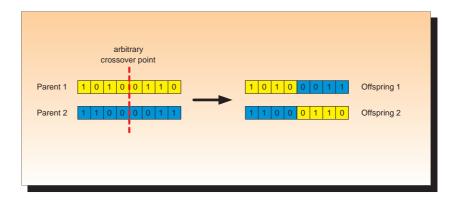

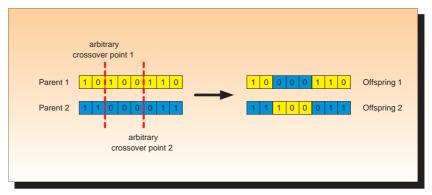

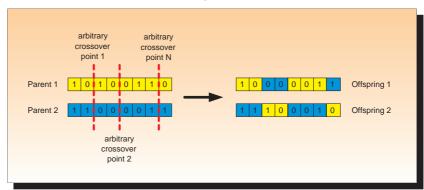

| 3.11 | Examples of genetic algorithm binary crossover techniques                        | 84  |

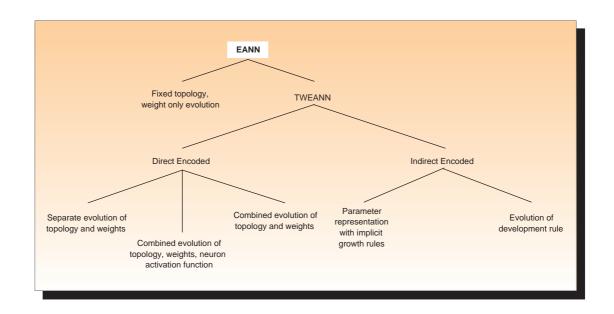

| 3.12 | Taxonomy of EANN algorithms                                                      | 85  |

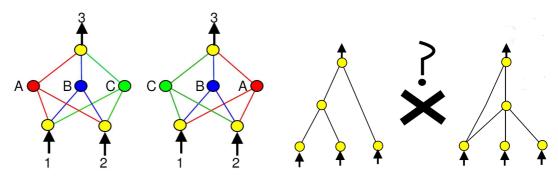

| 3.13 | Issues associated with topology genome representation & the crossover operator . | 87  |

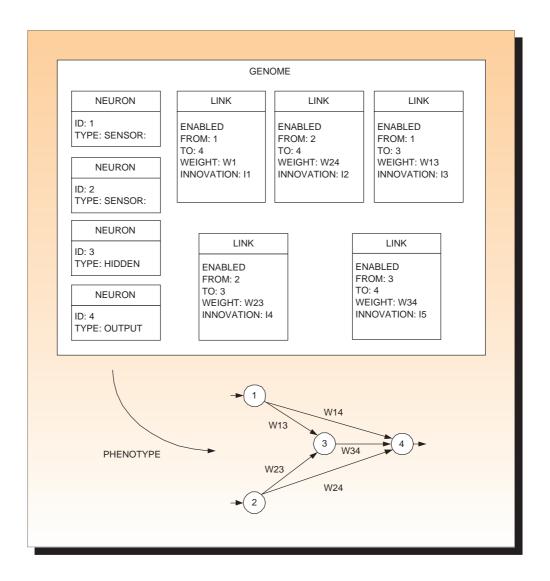

| 3.14 | Example of a NEAT genome and resultant phenotype                                 | 87  |

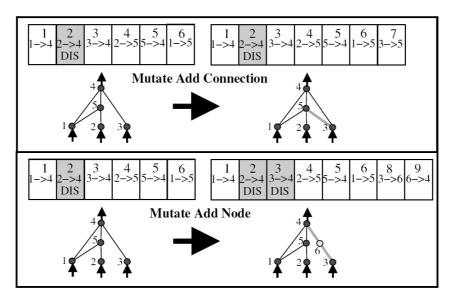

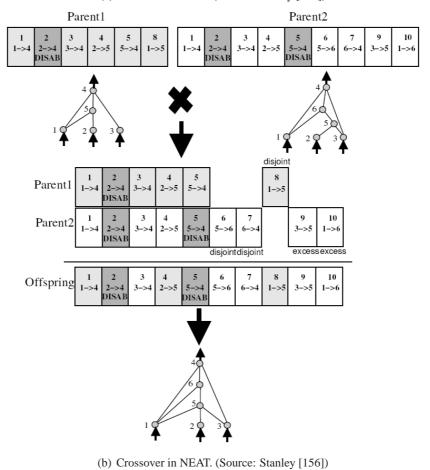

| 3.15 | Use of innovation numbers in the mutation and crossover operators in NEAT        | 89  |

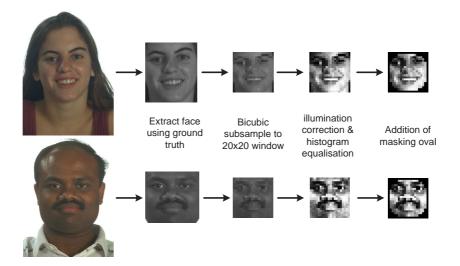

| 4.1  | Preprocessing of FERET face training dataset                                     | 93  |

| 4.2  | Example scenery image devoid of faces which was used during the training image   | 94  |

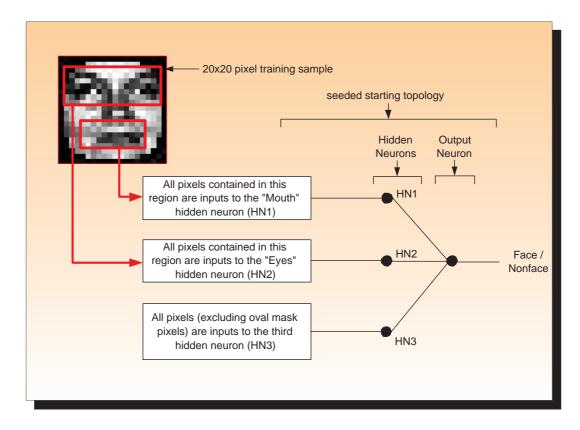

| 4.3  | Starting topology seeded with localised features                                 | 95  |

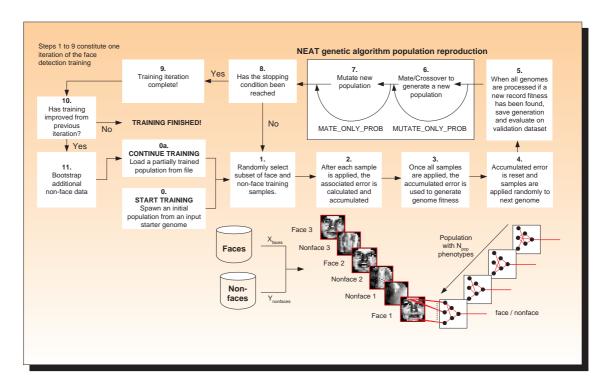

| 4.4  | Proposed NEAT-based face detection training                                      | 99  |

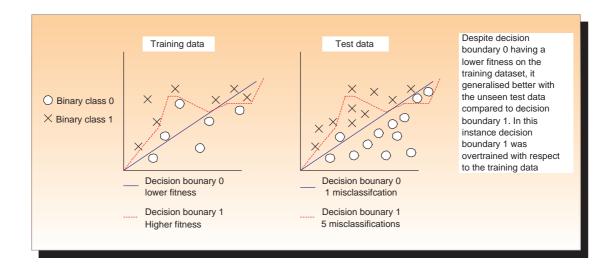

| 4.5  | Simple example of over-training                                                  | 100 |

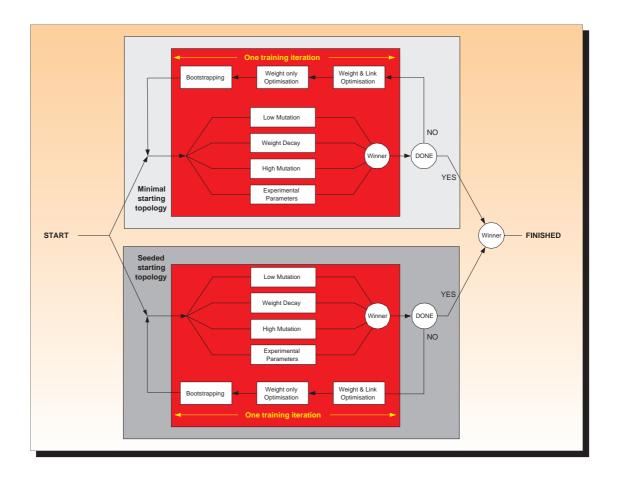

| 4.6  | Proposed Evolutionary Training Strategy                                          | 105 |

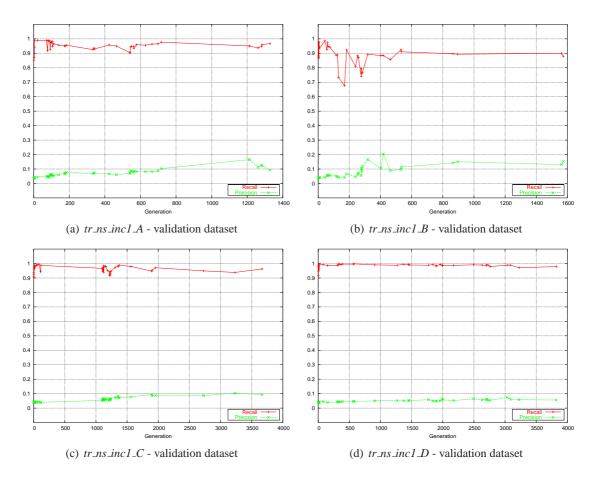

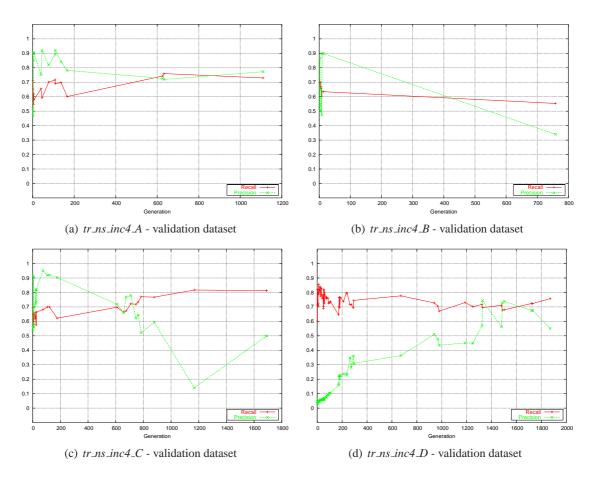

| 4.7  | Non-seeded topology training run – iteration 1                                   | 111 |

| 4.8  | Non-seeded topology training run – iteration 2                                   | 112 |

| 4.9  | Non-seeded topology training run – iteration 3                                   | 113 |

| 4.10 | Non-seeded topology training run – iteration 4                                   | 114 |

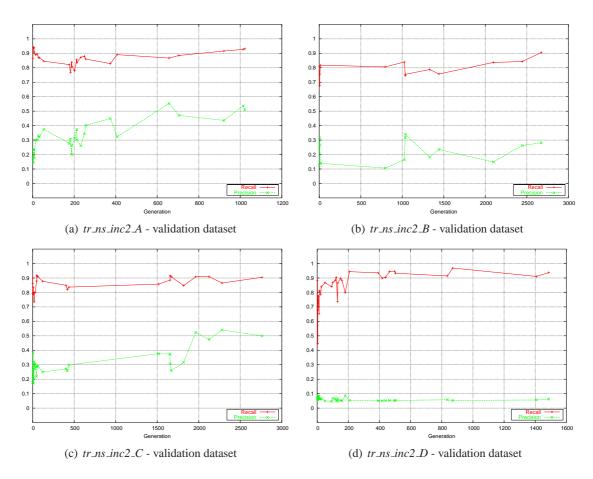

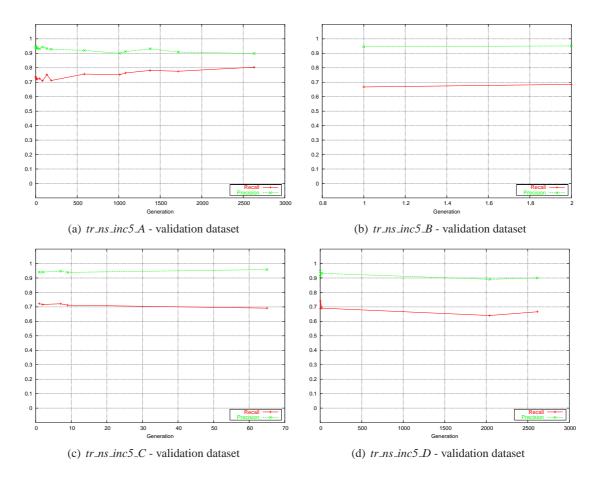

| 4.11 | Non-seeded topology training run – iteration 5                                   | 115 |

| 4.12 | Non-seeded topology training run – iteration 6                                   | 116 |

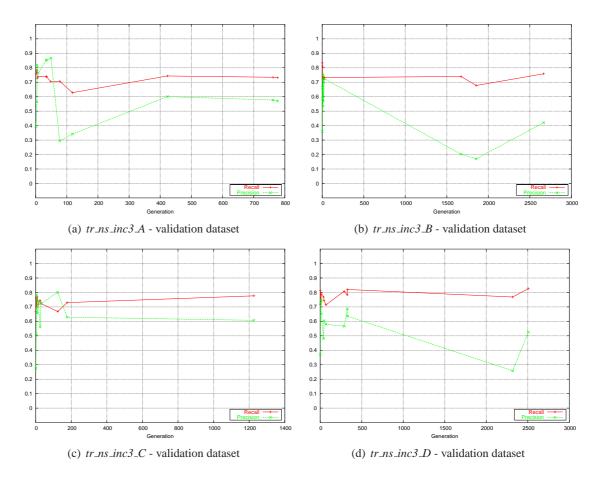

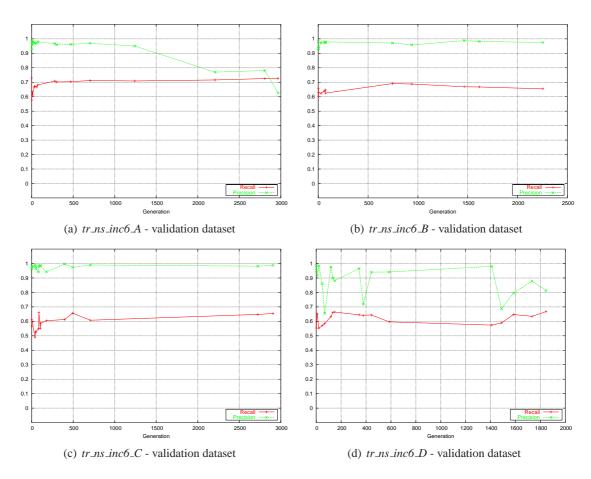

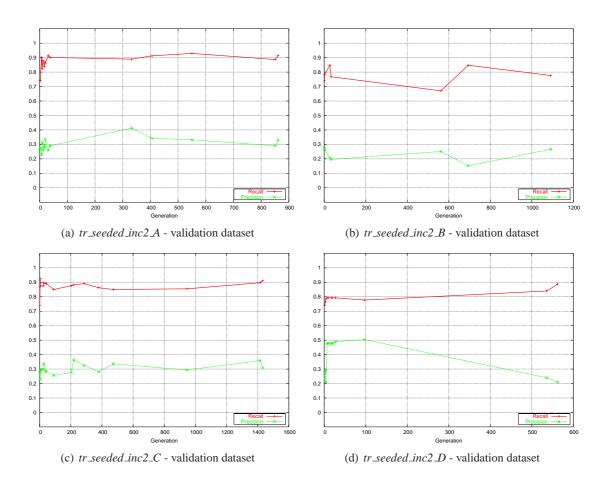

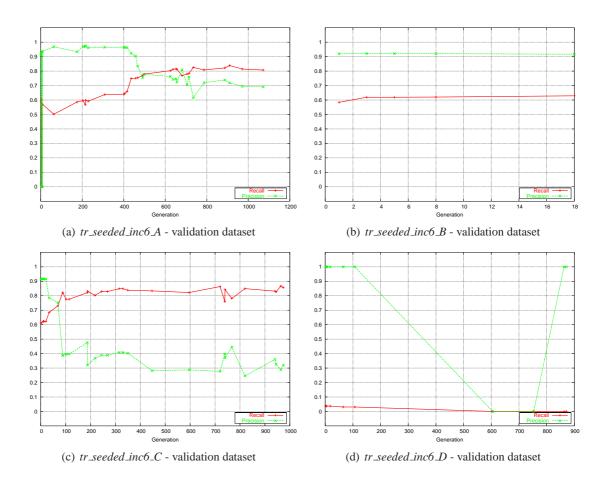

| 4.13 | Seeded topology training run – iteration 1                                       | 122 |

| 4.14 | Seeded topology training run – iteration 2                                       | 123 |

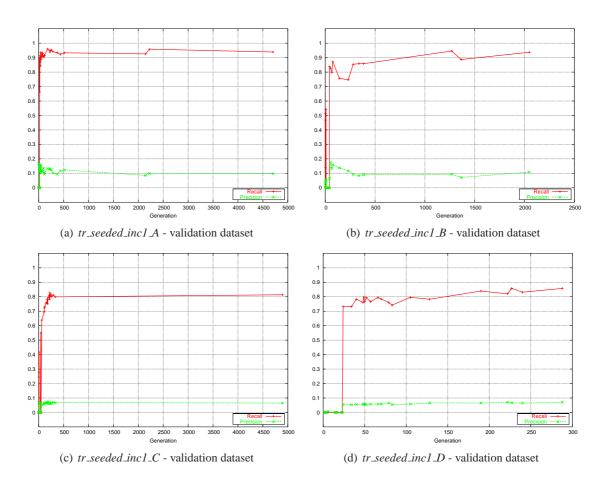

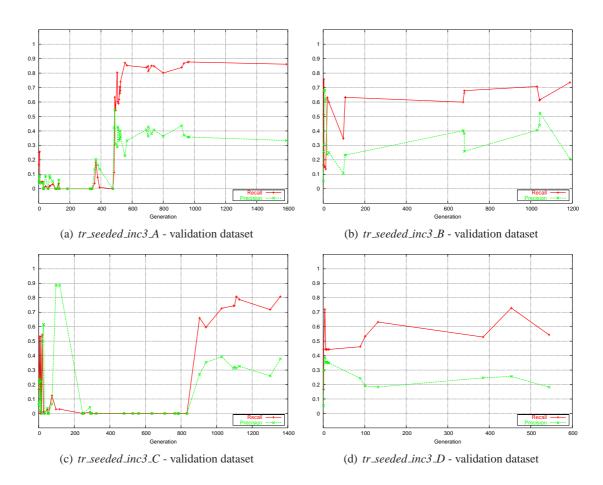

| 4.15 | Seeded topology training run – iteration 3                                       | 124 |

| 4.16 | Seeded topology training run – iteration 4                                       | 125 |

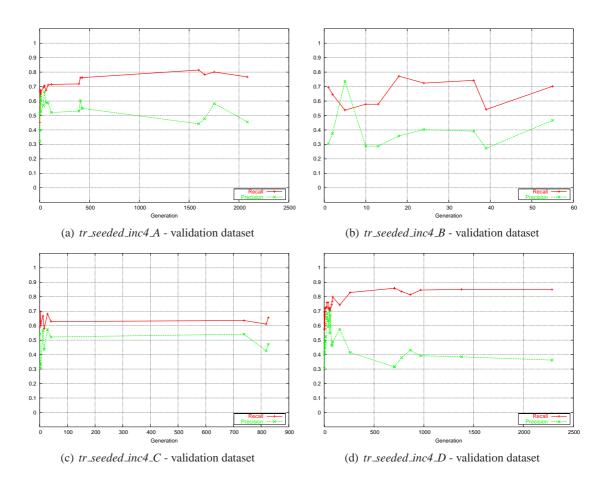

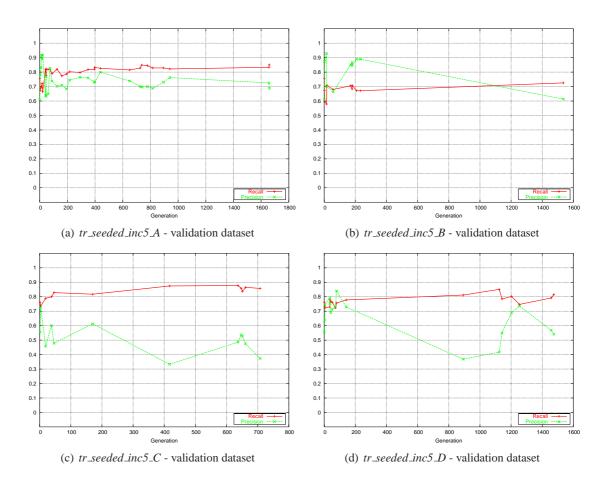

| 4.17 | Seeded topology training run – iteration 5                                       | 126 |

| 4.18 | Seeded topology training run – iteration 6                                       | 127 |

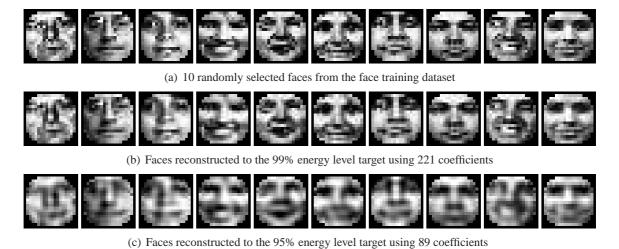

| 4.19 | DCT Energy exploration                                                           | 131 |

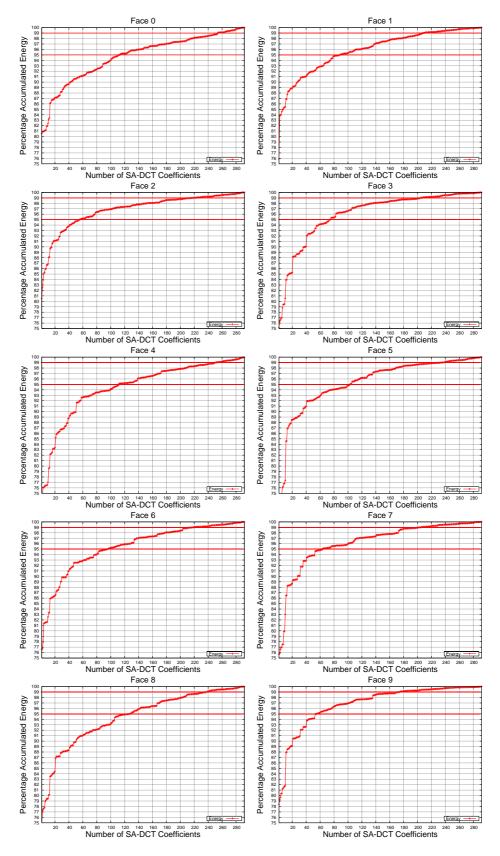

| 4.20 | Energy versus the number of SA-DCT coefficients of each of the face samples      | 132 |

| 5.1  | Example image pyramid                                                            | 135 |

|------|----------------------------------------------------------------------------------|-----|

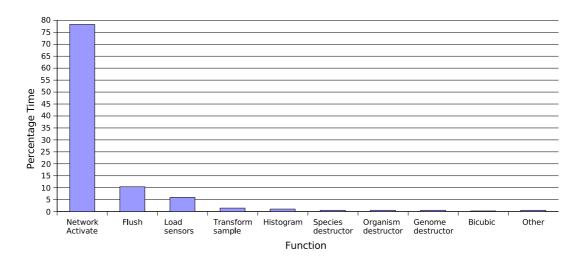

| 5.2  | Software Profiling of Proposed Face Detection Algorithm                          | 139 |

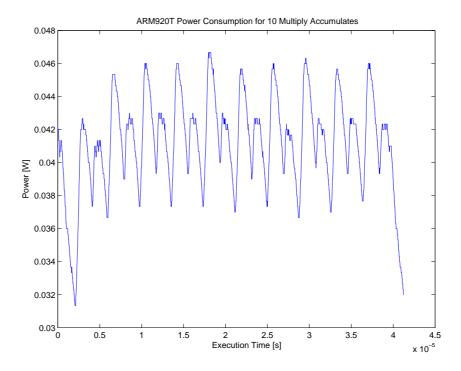

| 5.3  | Power Profiling of Multiply Accumulate Operations on an ARM-920T processor       | 141 |

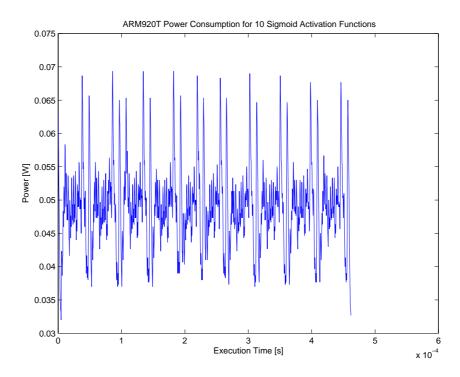

| 5.4  | Power Profiling of a Sigmoid Activation Function on an ARM-920T processor        | 142 |

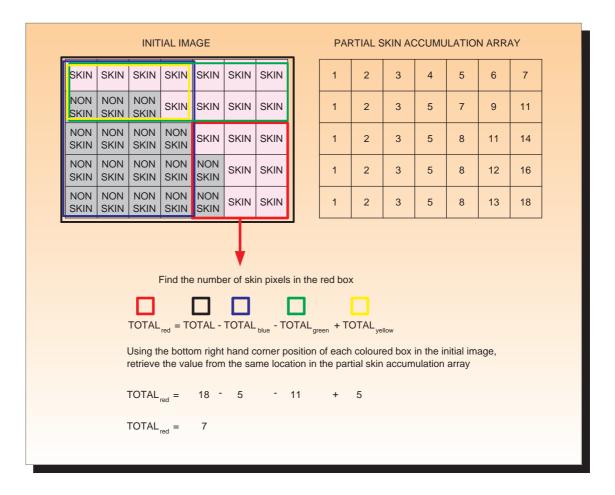

| 5.5  | Efficient calculation of block skin totals                                       | 143 |

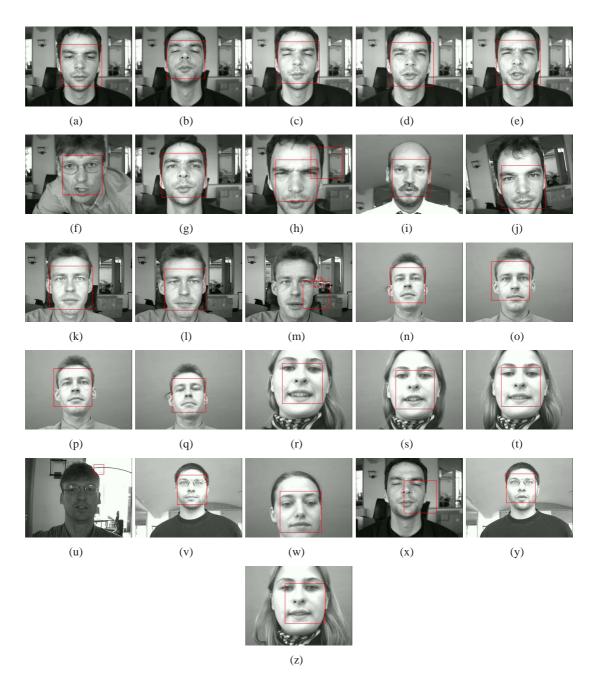

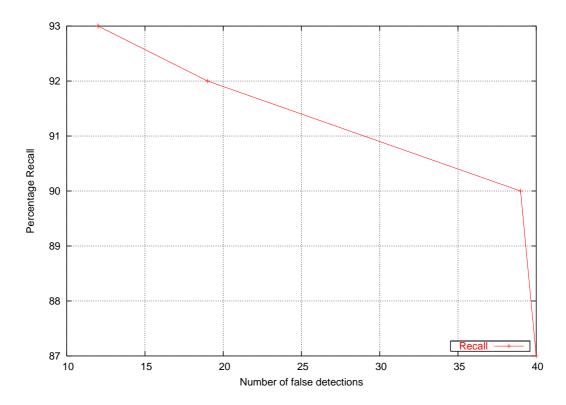

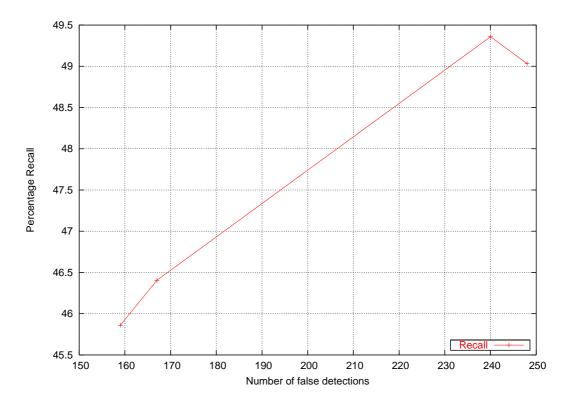

| 5.6  | Effect of changing the face detection threshold                                  | 146 |

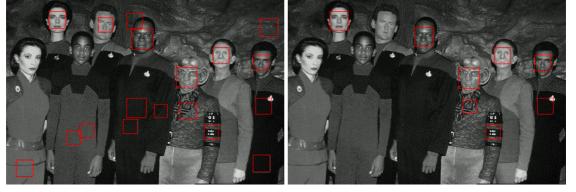

| 5.7  | Representative results from the BioID face evaluation dataset                    | 148 |

| 5.8  | ROC graph generated from proposed algorithm when using the BioID dataset         | 149 |

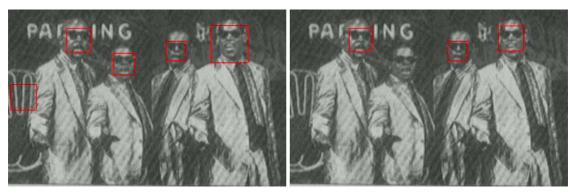

| 5.9  | Representative results from the CMU face evaluation dataset                      | 151 |

| 5.10 | ROC graph generated from proposed algorithm when using the CMU dataset           | 153 |

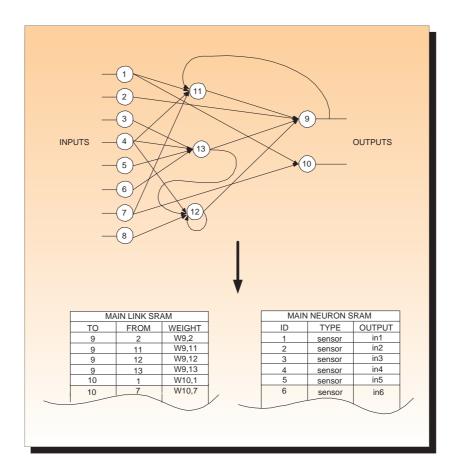

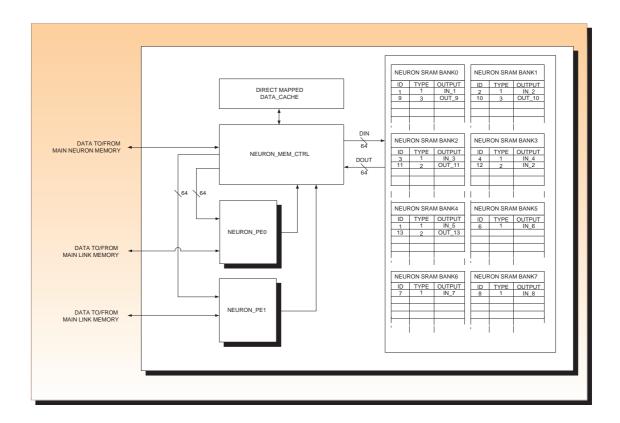

| 6.1  | NEAT multimedia hardware accelerator                                             | 157 |

| 6.2  | Neuron connection types                                                          | 162 |

| 6.3  | NEAT phenotype to hardware memory mapping                                        | 163 |

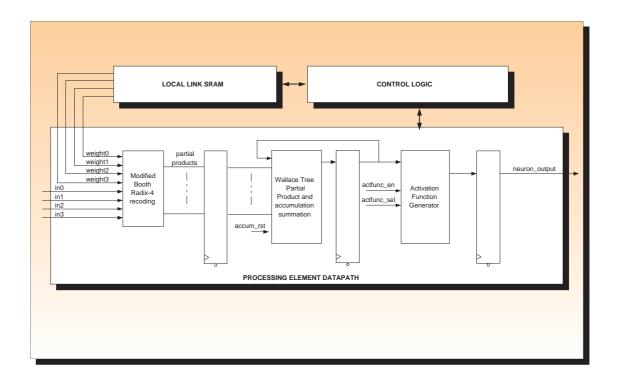

| 6.4  | Simplified block diagram of the proposed EANN hardware accelerator datapath $$ . | 164 |

| 6.5  | Simplified block diagram of the Neuron PE                                        | 166 |

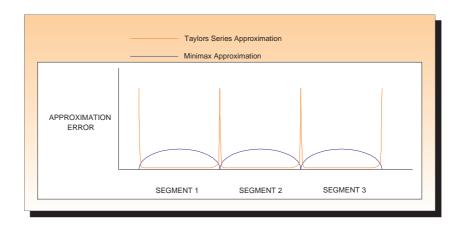

| 6.6  | Error of Minimax Spline versus a Taylor Series Spline                            | 167 |

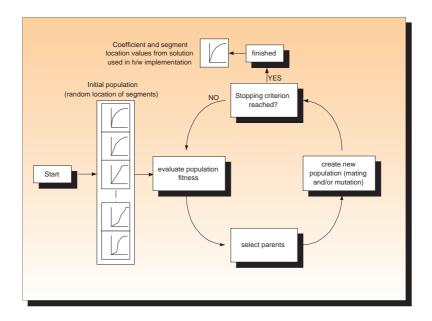

| 6.7  | Genetic algorithm used in optimising location of spline knot points              | 168 |

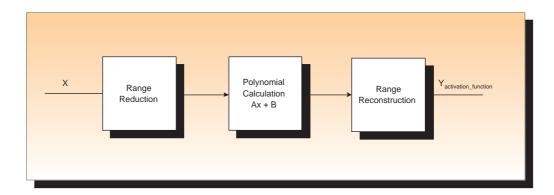

| 6.8  | Implementation of Activation function generator                                  | 170 |

| 6.9  | Elements of the Efficient Multiply Accumulate Hardware                           | 171 |

| 6.10 | Neuron PE timing diagram                                                         | 173 |

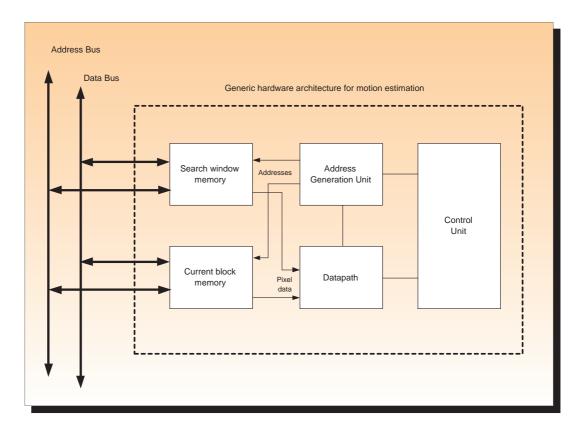

| 7.1  | Generic hardware architecture for motion estimation                              | 186 |

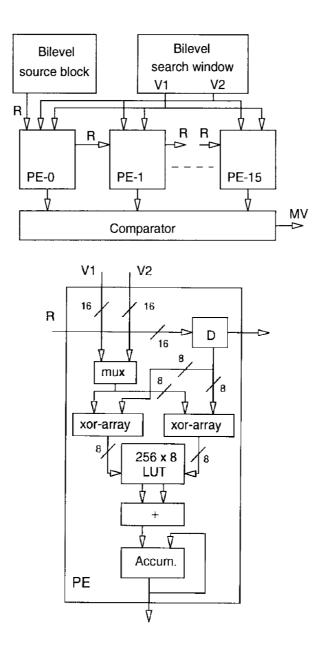

| 7.2  | Systolic array architecture and PE proposed by Natajaran et al                   | 191 |

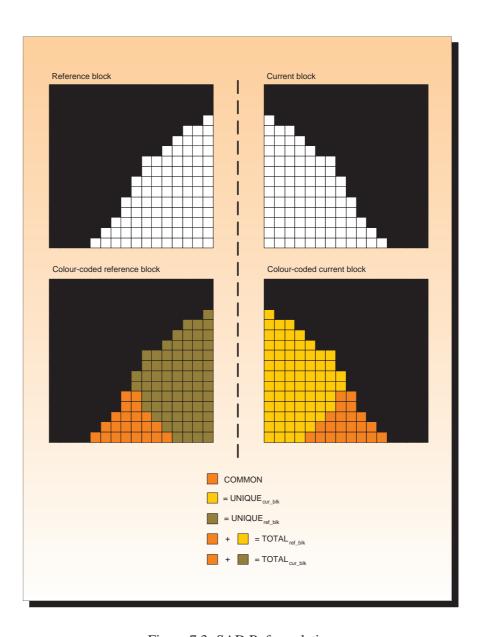

| 7.3  | SAD Reformulation                                                                | 195 |

| 7.4  | Reformulated binary SAD Examples                                                 | 197 |

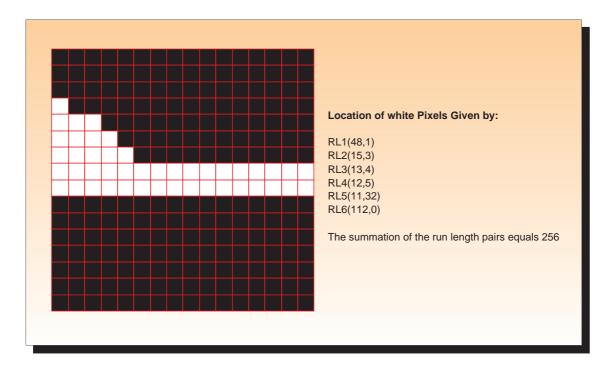

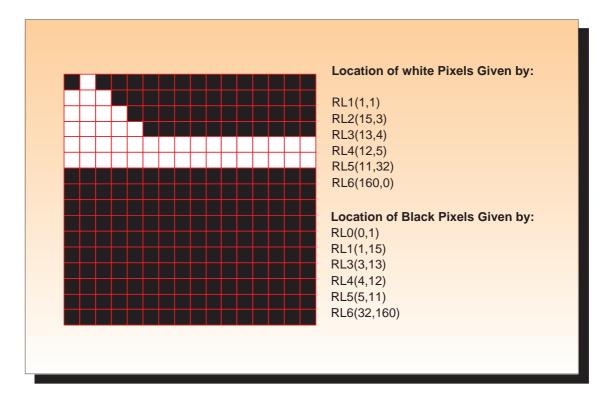

| 7.5  | Example of Run Length Coding                                                     | 198 |

| 7.6  | Regular and Inverse RLC pixel addressing                                         | 199 |

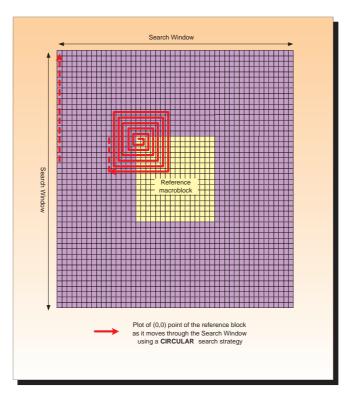

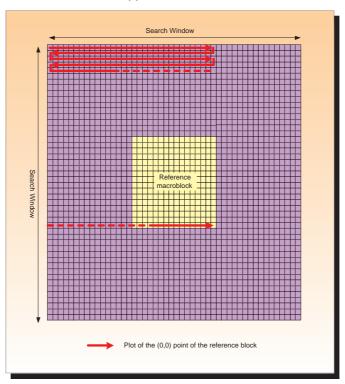

| 7.7  | Search strategies                                                                | 201 |

| 7.8  | $TOTAL_{ref\_blk}$ Update                                                        | 202 |

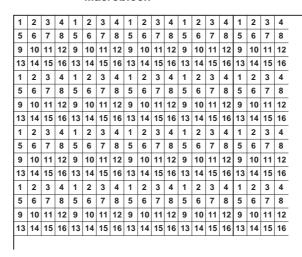

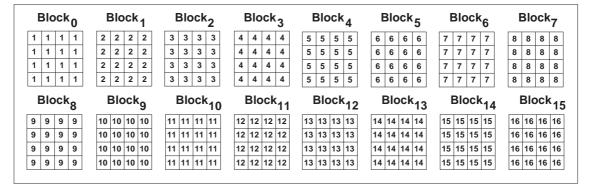

| 7.9  | Macroblock repartitioning for 4xPE Architecture                                  | 204 |

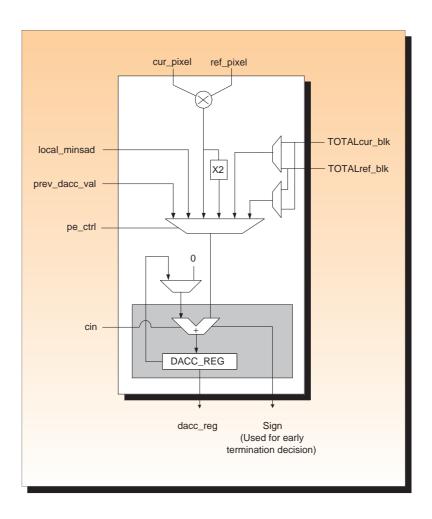

| 7.10 | RLC SAD Processing Element                                                       | 205 |

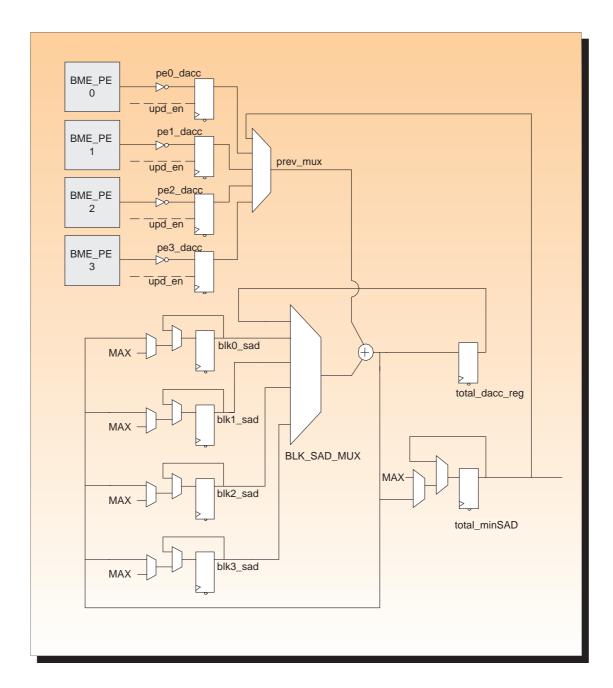

| 7.11 | 4xPE Update logic                                                                | 207 |

| 7.12 Memory Subsampling for 16xPE Architecture |

|------------------------------------------------|

|------------------------------------------------|

# List of Tables

| 1.1  | Novel semantic visual object based applications                             | 4   |

|------|-----------------------------------------------------------------------------|-----|

| 4.1  | Tunable parameters in proposed face detection training scheme               | 103 |

| 4.2  | Parameters for iteration 1 of non-seeded starting topology training run     | 111 |

| 4.3  | Parameters for iteration 2 of non-seeded starting topology training run     | 112 |

| 4.4  | Parameters for iteration 3 of non-seeded starting topology training run     | 113 |

| 4.5  | Parameters for iteration 4 of non-seeded starting topology training run     | 114 |

| 4.6  | Parameters for iteration 5 of non-seeded starting topology training run     | 115 |

| 4.7  | Parameters for iteration 6 of non-seeded starting topology training run     | 116 |

| 4.8  | Parameters for iteration 1 of seeded starting topology training run         | 122 |

| 4.9  | Parameters for iteration 2 of seeded starting topology training run         | 123 |

| 4.10 | Parameters for iteration 3 of seeded starting topology training run         | 124 |

| 4.11 | Parameters for iteration 4 of seeded starting topology training run         | 125 |

| 4.12 | Parameters for iteration 5 of seeded starting topology training run         | 126 |

| 4.13 | Parameters for iteration 6 of seeded starting topology training run         | 127 |

| 4.14 | Number of SA-DCT coefficients required to achieve specific energy targets   | 131 |

| 5.1  | Clock Cycles Required to Classify a Single $20 \times 20$ Pixel Block       | 140 |

| 5.2  | Benchmarking results for proposed algorithm against the BioID face database | 147 |

| 5.3  | Benchmarking results for proposed algorithm against the BioID face database | 152 |

| 6.1  | Maximum and average Sigmoid Approximation errors                            | 174 |

| 6.2 | Max and Mean Errors approximations for other functions   | 175 |

|-----|----------------------------------------------------------|-----|

| 6.3 | Benchmarking of Proposed Architecture against Prior Art  | 179 |

| 6.4 | Normalisation of power consumption from related research | 181 |

| 7.1 | RLC BME_4xPE versus Conventional Systolic Array BME      | 209 |

| 7.2 | BME Synthesis Results and Benchmarking                   | 209 |

## **ABSTRACT**

Semantic object-based processing will play an increasingly important role in future multimedia systems due to the ubiquity of digital multimedia capture/playback technologies and increasing storage capacity. Although the object based paradigm has many undeniable benefits, numerous technical challenges remain before the applications becomes pervasive, particularly on computational constrained mobile devices. A fundamental issue is the ill-posed problem of semantic object segmentation. Furthermore, on battery powered mobile computing devices, the additional algorithmic complexity of semantic object based processing compared to conventional video processing is highly undesirable both from a real-time operation and battery life perspective. This thesis attempts to tackle these issues by firstly constraining the solution space and focusing on the human face as a primary semantic concept of use to users of mobile devices. A novel face detection algorithm is proposed, which from the outset was designed to be amenable to be offloaded from the host microprocessor to dedicated hardware, thereby providing real-time performance and reducing power consumption. The algorithm uses an Artificial Neural Network (ANN), whose topology and weights are evolved via a genetic algorithm (GA). The computational burden of the ANN evaluation is offloaded to a dedicated hardware accelerator, which is capable of processing any evolved network topology. Efficient arithmetic circuitry, which leverages modified Booth recoding, column compressors and carry save adders, is adopted throughout the design. To tackle the increased computational costs associated with object tracking or object based shape encoding, a novel energy efficient binary motion estimation architecture is proposed. Energy is reduced in the proposed motion estimation architecture by minimising the redundant operations inherent in the binary data. Both architectures are shown to compare favourable with the relevant prior art.

# List of Acronyms

| 1 |     | Trimat. | Generation |   |

|---|-----|---------|------------|---|

| ı | ( T | FIRST   | Cienerano  | n |

**2G** Second Generation

**3G** Third Generation

**4G** Fourth Generation

AI Artificial Intelligence

ANN Artificial Neural Network

**BAB** Binary Alpha Block

**BAP** Binary Alpha Plane

BME Binary Motion Estimation

**CGM** Constrained Generative Model

CIF Common Intermediate Format

**CISC** Complex Instruction Set Computer

CRT Cathode Ray Tube

**DCT** Discrete Cosine Transform

**DPCM** Differential Pulse Code Modulation

**DWT** Discrete Wavelet Transform

EA Evolutionary Algorithm

**EANN** Evolutionary Artificial Neural Network

FPGA Field Programmable Gate Array

FPS Frames Per Second

FSM Finite State Machine

GA Genetic Algorithm

**GPU** Graphics Processing Unit

**GSM** Global System for Mobile

**HDTV** High Definition Television

**HMM** Hidden Markov Model

**HSI** Hue Satursation Intensity

**IDCT** Inverse Discrete Cosine Transform

Kbps Kilobits per second

**KLT** Karhunen-Loeve Transform

LCD Liquid Crystal Display

LUT Look Up Table

Mbps Megabits per second

**ME** Motion Estimation

MLP Multi-Layered Perceptron

MVPS Motion Vector Predictor for Shape

MVS Motion Vector for Shape

**NEAT** Neuro Evolution of Augmenting Topologies

**PCA** Prinicipal Component Analysis

PDA Personal Digital Assistant

PE Processing Element

**QCIF** Quarter Common Intermediate Format

RGB Red, Green and Blue

RISC Reduced Instruction Set Computer

**ROC** Receiver Operator Characteristics

**ROM** Read Only Memory

**RSST** Recursive Shortest Spanning Tree

**SAD** Sum of Absolute Differences

**SA-DCT** Shape Adaptive Discrete Cosine Transform

**SA-IDCT** Shape Adaptive Inverse Discrete Cosine Transform

**SDTV** Standard Definition Television

**SMS** Short Messaging Service

**SNoW** Sparse Network of Winnows

SoC System on a Chip

**SOM** Self Organising Maps

**SVD** Singular Value Decomposition

**SVM** Support Vector Machine

TWEANN Topology and Weight Evolving Artificial Neural Networks

VLC Variable length Code

**VoIP** Voice over Internet Protocol

**VOP** Video Object Plane

WAP Wireless Application Protocol

## List of Peer-Reviewed Publications

#### Patents

"Early Exit Techniques for Digital Video Motion Estimation", filed 2<sup>nd</sup> May 2005, Application number PCT/IE2005/000023.

#### Journals

Andrew Kinane, Daniel Larkin and Noel O'Connor, "Energy-Efficient Acceleration of an MPEG-4 Codec", EURASIP Journal on Embedded Systems, January 2007.

## Conferences

- Daniel Larkin, Andrew Kinane and Noel O'Connor, "Towards Hardware Acceleration of Neuroevolution for Multimedia Processing Applications on Mobile Devices", in the proceedings of the International Conference on Neural Information Processing, Hong Kong, China. October 3rd–6th 2006.

- Daniel Larkin, Andrew Kinane and Noel O'Connor, "An Efficient Hardware Architecture for a Neural Network Activation Function Generator", in the proceedings of the International Symposium on Neural Networks, Chengdu, P.R. China, May 29th–31st, 2006.

- Daniel Larkin, Valentin Muresan and Noel O'Connor, "A Low Complexity Hardware

Architecture for Motion Estimation", in the proceedings of the IEEE International

Symposium on Circuits and Systems, Kos, Greece, 21st–24th May 2006.

- 4. Daniel Larkin, Valentin Muresan and Noel O'Connor, "An Efficient Motion Estimation Hardware Architecture for MPEG-4 Binary Shape Coding", in the proceedings of the Irish Signals and Systems Conference, Dublin, Ireland, 1st–2nd September 2005.

- Daniel Larkin, Andrew Kinane, Valentin Muresan and Noel O'Connor, "Efficient Hardware Architectures for MPEG-4 Core Profile", in the proceedings of the Irish Machine Vision and Image Processing Conference, Belfast, Northern Ireland, August 30th–31st 2005.

- 6. Noel O'Connor, Valentin Muresan, Andrew Kinane, Daniel Larkin, Sean Marlow and Noel Murphy, "Hardware Acceleration Architectures for MPEG-Based Mobile Video Platforms: A Brief Overview", in the proceedings of the 4th Workshop on Image Analysis for Multimedia Interactive Services (WIAMIS), London, England, 9th–11th April 2003.

- Contributions to MPEG-4 (Non peer reviewed)

- Daniel Larkin, Andrew Kinane and Noel O'Connor, "Conformance testing of Binary Motion Estimation for MPEG-4 Binary Shape Coding", Contribution 13182 to AHG on MPEG-4 Part-9: Reference Hardware ISO/IEC JTC1/SC29/WG11, Montreux, Switzerland, April 2006.

- Daniel Larkin, Valentine Muresan and Noel O'Connor, "Updated Status and documentation of the Shape Coding Binary Motion Estimation Hardware Acceleration Module", Contribution N6759 to AHG on MPEG-4 Part-9: Reference Hardware ISO/IEC JTC1/SC29/WG11, Palma de Mallorca, Spain, October 2004.

- Daniel Larkin, Valentine Muresan and Noel O'Connor, "Hardware Acceleration Module for MPEG-4 binary shape coding motion estimation", Contribution M11092 to AHG on MPEG-4 Part-9: Reference Hardware ISO/IEC JTC1/SC29/WG11, Redmond, USA, July 2004.

## **ACKNOWLEDGEMENTS**

It is a pleasure to thank the many people who have contributed in making this thesis possible. Firstly, I would like to thank my supervisor, Prof. Noel O'Connor, for his guidance and support during this research. In particular, I'm very grateful for his advice and invaluable suggestions throughout the thesis writing period. I'd also like to thank all the past and present members of the hardware group, particularly Andrew Kinane, Kealan McCusker and Val Muresan, for all their technical assistance. I owe a great debt of gratitude to my mother and sisters for their support and encouragement over the years. I am also tempted to individually thank all of my friends. However, there are too many to mention, so I will simply say thank you very much to you all. Lastly, and most importantly, I wish to thank Fiona for putting up with the late hours and shortened weekends. Without her constant encouragement and love, this research would never have been completed.

# CHAPTER 1

## Introduction

Relentless progress in semiconductor technology is a key enabling factor in the continuous evolution of modern connected computing solutions [1][2]. Both now and historically, this evolution is driven by the diverse needs of users in academic, military, business and home environments. For example the emergence of key computing platforms (mainframe, PC, etc.) and different application families (databases, spreadsheets, data networking, computer gaming, etc) can be directly attributed to these diverse needs. Moreover, whereas once computer technology was only considered as a tool to assist in scientific and business calculations, it is now also deeply ingrained in many fundamental facets of our daily lives, such as entertainment (digital films, digital TV, etc.) and communications (Voice over Internet Protocol (VoIP), email, instant messaging, etc). With such ubiquity, the choice of which platform (server, PC, laptop, mobile device etc.) a user employs is typically a trade off between cost and/or requirements (computational resources, networking resources, interface, mobility etc). Increasingly, mobile devices such as mobile phones, smartphones, Personal Digital Assistants (PDA) etc are becoming a viable and popular platform for a range of applications. In 2005 alone there were over 800 million mobile phones sold [3][4]. This compares to approximately 200 million desktops, notebooks and x86 servers which were shipped in the same year [5]. In 2006 there were over 1 billion mobile phones sold [6].

There are many contributing factors to the popularity and success of such mobile devices. A fundamental desire for untethered voice communications fuelled the success of the initial First Generation (1G) and Second Generation (2G) mobile phones. Emerging Third Generation (3G)

mobile devices have a much broader appeal due to improved computational and telecommunications capabilities. These mobile devices allow multiple forms of effective and immediate communication. In addition, the improving general purpose computing performance of the device is enabling application convergence (e.g. telephone, video conferencing, Short Messaging Service (SMS), email, internet browsing, gaming, digital camera, digital audio/video player, mobile TV, etc) on the devices [7][8][9]. These additional applications are beneficial in both personal and corporate use scenarios, and allow "dead time" (e.g. commuting, queueing, etc) to be used more productively. This is a particularly valuable feature for todays society, which places such a high value on the commodity of time. By augmenting the technical capabilities and improving mass market appeal, mobile devices are now frequently designed and marketed as highly desirable, premium priced style icons [10][11]. It is not surprising then to find users who feel a strong sense of attachment to their mobile device. The growing market for device personalisation (ring tones, wallpapers, coloured fascias), which was worth over \$3 billion worldwide in 2005, is strong evidence of the desire of a subset of users to extend their personality and individualism to their mobile device [12]. This is a clear indication of how deeply ingrained mobile devices have become in todays social fabric. Coupled with the technical advances, this demonstrates how increasingly important the ubiquitous mobile device will become as a general purpose computing platform in the future.

## 1.1 The Emergence of Mobile Multimedia

The widespread availability of low cost digital capture and playback devices with ever increasing storage capacity, coupled with rapid advances in signal processing, have now made digital multimedia universal [13][14][11]. These technological advances alongside changing human behaviour have affected all aspects of how multimedia is now created, stored, distributed and consumed. For example, traditional sources of video content (TV, film etc.) are being complemented by user created content (e.g. mobile-video calls, video messaging, video blogs, etc.) [15]. In this new paradigm, users are frequently empowered by the ubiquitous battery powered mobile device and motivated by factors such as a desire for graphically enriched communications, or for filling "dead time" by consuming multimedia content. These devices have the potential to offer an engaging mobile multimedia experience for the user. Furthermore, reflecting a symbiotic relationship, increased multimedia processing capabilities is considered vital for future mobile devices [16].

Figure 1.1: Video scene decomposed into constituent semantic objects

However, numerous technical challenges remain to be solved before next generation mobile multimedia can become a reality.

## 1.2 Grand Challenges Facing Next Generation Mobile Multimedia

The phenomenal growth in digital multimedia in conjunction with the emergence of convergent mobile devices has highlighted a number of open research challenges facing next generation mobile multimedia. Amongst others these challenges include semantic multimedia processing, multimedia content delivery and the issues arising as a result of the constrained resources available on a mobile device. This section briefly outlines these challenges in order to give context for the research undertaken in this thesis. A more thorough discussion of these issues is presented in Chapter 2.

## 1.2.1 Semantic Multimedia Processing

Rapidly increasing volumes of digital multimedia content emphasises a need for improved content structure awareness in multimedia processing algorithms. For example, this requirement becomes apparent by witnessing the difficulties encountered whilst searching large personal digital image or video libraries devoid of meta-data. Moreover, bridging the gap between a correlated collection of pixels and the overall semantics of these pixels, is of considerable benefit to the entire end to

Table 1.1: Novel semantic visual object based applications

| Phase        | Example Applications                        |

|--------------|---------------------------------------------|

| Creation     | Video object reuse, virtual scene creation, |

|              | intelligent capture technology              |

| Storage &    | Region of interest coding, spatial/temporal |

| Compression  | scalable visual object coding, very low bit |

|              | rate object model based coding              |

| Consumption  | Semantic transcoding, video summarisation,  |

| & Viewing    | content based interaction, intelligent      |

|              | searching & browsing                        |

| Transmission | Increased error protection for semantically |

|              | important objects, event triggering based   |

|              | on detection of semantic objects            |

end life cycle of digital visual data. The same conclusion can also be drawn about audio content, however this research focuses on visual data only.

By processing visual data in terms of the encapsulated semantic objects (see Fig. 1.1), improvements can be made to a plethora of applications within the realm of video/image processing and analysis. These include browsing, searching, video summarisation, transcoding, region of interest compression and scalable compression. This is already evident to users of on-line digital image and video libraries, where the growing use of manual annotation (popularised as "tagging") of the semantics of the content considerably aids searching and browsing [17][18]. However, such manual annotation is costly, tedious and inconsistent. Unfortunately, automatic semantic segmentation (the process of decomposing the scene into unique semantic visual objects) and annotation is an impossible task to solve in a generic fashion. These could be considered the principal reasons why semantic object based processing is not pervasive. Fundamentally, automatic segmentation and annotation is an ill-posed problem. Even from a human perspective, different observers will describe the same scene in different ways. In fact, even the same observer will view the same scene with different levels of granularity based upon their motives for viewing. As will be shown in Chapter 2, the problem can only be made tractable by focusing on specific application scenarios, e.g. sports games, head and shoulder sequences etc. Despite these restrictions, and the likelihood of non-ideal automatic segmentation and annotation, semantic processing still offers the potential to assist and/or make possible novel applications throughout all phases of visual data processing, albeit in constrained domains. Examples of such applications are listed in Table 1.1. The proposed research aims to contribute enabling technologies in this area.

Detecting objects at the point of creation on a mobile device rather than offline on a less computationally constrained computing resource is an attractive proposition as it allows semantics to be introduced earlier in the digital visual data "life cycle". This has the potential to permit a greater range of novel applications (see Table 1.1). For example, during a mobile video call, the detection of the most important semantic visual objects (e.g. human faces), would allow higher quality encoding or increased error robustness for these objects. This is not possible if the object detection does not take place on the mobile device. Unfortunately, even when the solution space is constrained, semantic object segmentation algorithms are inherently computationally complex. On a mobile device this computational complexity increase diminishes real time performance and increases power consumption. This is highly undesirable as mobile devices suffer from a variety of limitations as will be described in Section 1.2.3. There is a clear conflict between the mobile device hardware limitations and the requirement for robust segmentation algorithms for semantic video processing. This provides strong motivation for innovative research in this domain.

## 1.2.2 Multimedia Content Delivery to Mobile Devices

The evolution from the analog wireless infrastructure to 2G systems, was principally driven by a need for improved mobile personal communications. Widespread advances in areas including voice quality, hand-off speed, spectrum usage efficiency, error robustness, etc. allowed 2G mobile communications to be very successful in handling voice and low end data. Furthermore, the move to 2G systems also enabled new services such as SMS, fax, Wireless Application Protocol (WAP), etc [19]. These additional services provided extra non-voice based revenue streams for network operators and useful services for end users. However, with bandwidth limited to 9.6 Kilobits per second (Kbps), bandwidth intense services such as video conferencing or video on demand were not feasible. The emerging 3G standard, which uses digital packet switched technology and can achieve data transfer rates up to 2 Megabits per second (Mbps) is an attempt to address this issue. Whilst high data rates are important, it is only one issue when carrying multimedia content on very lossy wireless communication channels. Multimedia content can tolerate some loss, however the time sensitivity of delivery presents unique challenges. Fast hand-off, low latency and minimal packet loss are fundamental to the success of streaming multimedia [20], and as such underpins current research in the area. Active research topics include quality of service, mobility support, signalling protocols, network survivability etc and the impact these have on power consumption on the mobile device [21][22][20][23][24]. In the longer term outlook, research has begun on Fourth Generation (4G) systems, a principal feature of which is the seamless integration of multiple communication technologies including Global System for Mobile (GSM), wireless LAN, bluetooth

etc. Another important feature of 4G systems is the provision of services based upon contextual awareness (location, environmental, health, activity). Clearly, progress in wireless infrastructure is vital for the successful delivery of next generation high resolution multimedia content, however, this is outside the scope of this research and will not be considered further in this thesis.

## 1.2.3 Multimedia Processing on Resource Constrained Mobile Devices

Multimedia processing is generally considered one of the most computationally demanding tasks, due to elaborate resource intense algorithms coupled with a requirement for high throughput performance, frequently with a real time constraint. Yet a mobile device suffers from a variety of limitations, including low computational capabilities, low memory capacity, short battery life and strict miniaturisation requirements (size, weight, screen size etc). Therefore, the computational demands associated with multimedia processing on a mobile device have the highly undesirable effects of reducing real time performance and increasing power consumption on the device. This issue is further exacerbated by the trend for the mobile device to act as a point of convergence for multiple microprocessor intensive applications. Furthermore, as was demonstrated by the failure of initial WAP services, users are unwilling to tolerate degradation in the overall application experience just for mobile convenience [25][26].

The system designer of a mobile device is now presented with the unenviable challenge of implementing high resource usage algorithms on low throughput and resource limited hardware with short battery life. In particular, as further elaborated in Chapter 2, the short battery life places a major constraint on mobility, since the rate of battery discharge in a mobile device governs the operating time of the device between recharges. In addition, the battery also has a direct impact on the overall size and weight of the device. Unfortunately, the intuitive approach to tackling short battery life by improving battery technology is providing limited results, with battery capacity only improving by 5% each year [7]. Therefore, a more fundamental approach is required, which tackles power consumption as the cause of the short battery life. These factors, coupled with the overarching impact of power consumption on circuit timing performance, silicon resource usage and electronic component reliability have brought energy efficiency to the forefront of design in recent times. Energy efficient design is discussed in detail in Chapter 2.

## 1.3 Research Motivation and Work Programme

Considering that there is huge consumer demand for novel multimedia applications on mobile devices, the issues outlined in Section 1.2 are unfortunate, particularly as semantic object based processing could be considered an enabling technology toward that goal. This provides the motivation for this research to explore viable implementation options for semantic object processing on mobile devices. The proposed segmentation solution avoids attempting deep automatic interpretation of digital visual data, and focuses instead on mid-level semantic objects. This approach is taken as there is an emerging belief that mapping low level pixels to (frequently well defined) semantic objects is a considerably easier task than a direct mapping from pixels to diverse user semantics [27][28][29].

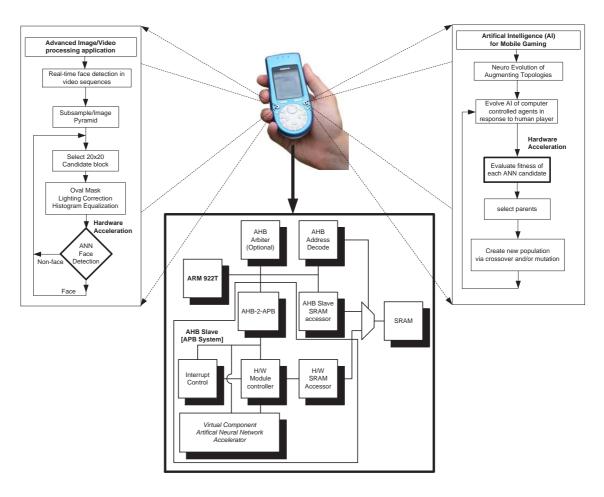

#### 1.3.1 Novel Face Detection and associated hardware acceleration

In order to demonstrate a robust semantic video object segmentation solution, the problem is constrained and focused on the segmentation of the human face as a fundamental semantic object of benefit to users of mobile devices. As Chapter 2 will demonstrate, there are many approaches to face detection. A fundamental goal of this research is to find solutions which are suitable for deployment on a resource constrained mobile device and this has a major influence of the choice of algorithm. The proposed novel solution (see Chapter 5), employs an Evolutionary Artificial Neural Network (EANN). During regular face detection, the computational complexity associated with the Artificial Neural Network (ANN) phenotype evaluation is offloaded from the host processor to a dedicated hardware accelerator. As will be demonstrated in Chapter 8, this improves energy efficiency and real-time performance. This approach also offers the scope to be retargeted to classify extracted features for other semantic processing tasks. In addition, owing to the widespread deployment of ANNs in a broad spectrum of classification, perception, association and control applications [30], the core could be re-deployed for a number of applications on a mobile device. For example, by modifying the software, the same core that accelerates face detection could be reused as an accelerator for advanced Artificial Intelligence (AI) for computer gaming [31]. This scenario along with a ARM microprocessor based hardware integration framework is depicted in Fig. 1.2. However, applications other than EANN-based face detection are outside the scope of this research.

Figure 1.2: Example of multiple applications leveraging a hardware ANN accelerator

## 1.3.2 Hardware Acceleration of Motion Estimation

Motion Estimation (ME) is a fundamental enabling technology widely used in video compression and video processing tasks. One such video processing task is tracking semantic video objects (such as faces) in video sequences. In the case of face detection, such tracking can be used to improve detection rates and/or reduce computational expense in multi-resolution face detection algorithms. Furthermore, it is generally accepted that ME consumes 40%–80% (depending on the configuration) of the total computational resources required in modern video encoders [32][33]. The re-usability potential, coupled with the high computational expense, makes ME a very suitable candidate for low power hardware acceleration on a semantic video processing enabled mobile device. Chapter 7 describes the proposed ME architecture, which in this research is principally employed to reduce the computational expense of the face detection algorithm described in Chapter 5. With the target deployment of a mobile platform, the architecture is designed with low power operation as the principal design constraint. This goal is achieved by exploiting inherent algorithmic and data redundancies.

## 1.4 Research Objectives

The research goals of this thesis can be summarised as follows:

- 1. To design a face detection algorithm suitable for hardware acceleration

- 2. Evaluate the proposed face detection algorithm against prior art proposed in the literature.

- 3. To design and implement an energy efficient hardware accelerator for EANN.

- 4. To design and implement a flexible motion estimation core which can be used in the encoding of binary shape associated with the segmented face.

- To evaluate both hardware architectures against prior art within a fair benchmarking and normalisation framework.

## 1.5 Thesis Structure

The thesis is structured as follows:

#### • Chapter 1 – Introduction

The introduction (this chapter) outlines the context and motivation for the research conducted in this thesis.

## • Chapter 2 - Theoretical Background

The theoretical background chapter elaborates in more detail the technical context for the research. The general topics covered are digital video processing (digital video compression & semantic video object segmentation) and low power design.

## • Chapter 3 – Face Detection: A Review of Popular Approaches

This chapter firstly presents a thorough review of the prior art in face detection algorithms. Conclusions are drawn from this review and a novel algorithm proposed.

## • Chapter 4 – A Novel Face Detection Training Algorithm

The proposed novel face detection training algorithm is described in detail. Comprehensive details are presented for various training runs.

## • Chapter 5 – Software Implementation of Trained Face Detection Algorithm

This chapter describes the implementation of the trained EANN face detection algorithm in

software. Software profiling and optimisations are discussed. Face detection performance benchmarking comparisons against prior art are then presented.

#### • Chapter 6 - Hardware Acceleration of EANN

A review of ANNs and EANN is firstly provided. The proposed hardware architecture for the EANN accelerator is subsequently described in detail. This is followed by evaluation against the prior art.

## • Chapter 7 – Hardware Acceleration of Motion Tracking

This chapter initially reviews related research in the field of motion tracking. A detailed description of the proposed motion estimation/tracking hardware architecture is presented. This is followed by evaluation against the prior art.

#### • Chapter 8 – Conclusions & Future Work

This chapter provides a summary of Chapters 3,4,5,6 & 7, outlining the key contributions. This is followed by a discussion which suggests avenues for future expansion of the research.

## 1.6 Summary

The growing market for mobile phones is a reflection of how ubiquitous battery powered mobile devices have become in today's society. Multimedia functionality is seen as a vital component in the current and future success of these devices. However, inherently resource intensive multimedia processing algorithms present numerous implementation challenges due to the limited computational resources available. In the future these challenges will be exacerbated by a consumer demand for semantic content aware multimedia processing algorithms. This research aims to help in this regard with contributions to the fields of semantic video object segmentation and dedicated video processing hardware. Specifically a novel face detection algorithm and energy efficient hardware architectures for ANN and ME acceleration are proposed in this research.

# CHAPTER 2

# **Technical Background**

This chapter reviews issues in digital video compression, semantic video object segmentation, implementation options and energy efficient design principles in order to provide context for the research carried out. Previously in Chapter 1 it was highlighted that the rapid progress in digital video compression algorithms is a fundamental underpinning technology partly responsible for the ubiquity of high quality digital video on both mobile and tethered computing platforms. An overview of these video compression algorithms/tools along with their associated deployment in industry standards is provided in Section 2.1. Section 2.1.2 discusses how these video compression algorithm and tools can be extended to process content in terms of encapsulated semantic objects, which as was shown in Chapter 1, can facilitate applications allowing a plethora of benefits for the end user. A review of algorithms for the extremely challenging problem of object segmentation is given in Section 2.2. The contributions of this thesis within a semantic video processing context are outlined in Section 2.3. A selection of implementation options for advanced video processing on computationally constrained mobile devices is presented in Section 2.4. A vital consideration for implementation of advanced algorithms on a mobile device is energy efficiency. As such, a detailed review of energy efficient design principles is given in Section 2.5. This includes an overview of the sources of power consumption, as well as common techniques used to reduce power consumption.

## 2.1 Digital Video Compression

Before considering digital video<sup>1</sup> compression techniques or semantic video object processing algorithms, the fundamental properties and characteristics of raw unencoded digital video require explanation. A raw unencoded digital still image can be considered to be a "snap shot" of a natural real world scene, which results in a two dimensional rectangular or square matrix of discrete digital samples capturing the colours present. It is assumed that the real world scene contains smooth continuous colour tones with bandwidth limited edges (these are characteristics which can be exploited in compression algorithms). Each resultant digital sample is a representation of the colour in the scene at a particular location. The colour can be represented in a variety of different schemes (i.e. different colour spaces). In the most direct scheme each sample consists of Red, Green and Blue (RGB) components. Typically, 24 bits per RGB triplet is considered to give adequate dynamic range, although it is not uncommon for a greater number of bits to be used. For example, in some High Definition Television (HDTV) encoder/decoder datapaths and medical imaging storage applications ten or twelve bits are used. As with all analogue to digital sampling, Nyquist sampling theory must be considered, although the human psychovisual system is quite tolerant to many aliasing effects<sup>2</sup> [34]. The size of the rectangular sampling matrix or frame is application and transmission bandwidth dependent. For example, on mobile devices with limited screen size and limited transmission bandwidth, standardised resolutions such as  $352 \times 288$ (referred to as Common Intermediate Format (CIF)) or  $176 \times 144$  (referred to as Quarter Common Intermediate Format (QCIF)) samples or pixels are popular, whilst at the other end of the consumer market, European PAL based Standard Definition Television (SDTV) and HDTV have typical active resolutions of  $720 \times 576$  and  $1920 \times 1080$  respectively.

Digital video temporally extends digital still image sampling. There is continuous sampling of a scene at discrete time intervals in conjunction with spatial sampling in two dimensions (see Fig. 2.1). The temporal sampling resolution is typically quoted as the number of frames per second. It should be noted that the visual quality of the captured video is heavily influenced by the spatial and temporal resolution. A high horizontal and vertical sampling allows a natural scene to be captured with more fine detail and thus creates a greater sense of realism. A high

<sup>&</sup>lt;sup>1</sup>In this thesis, unless explicitly stated otherwise, digital video is frequently used to refer to both digital video and digital still images. This generalisation is made as digital video could be considered to be a superset of digital still images. That is, digital video is an extension of digital still images in the temporal domain.

<sup>&</sup>lt;sup>2</sup>This is not always the case. For example, a familiar aliasing phenomena (present particularly in older films) that is noticeable and quite objectionable, occurs when the spokes of a fast moving waggon wheel appear to move backward. This is caused by temporal aliasing [34].

Figure 2.1: An example of a digital still image and video sequence

Figure 2.2: Examples of  $YC_bC_r$  sampling modes

frame rate (i.e. temporal sampling rate) allows objects within a scene that have high levels of motion to be perceived as having smooth continuous trajectories, whereas if the sampling rate were lower the object could appear as having a disconcerting jerky movement. Increasing the frame rate obviously has a proportional increase in the unencoded bit-rate of the video and this is not desirable in many applications. For example, low bit-rate communications (e.g. webcams, mobile video calls) sometimes use a frame rate as low 5-15 frames per second. However, this can result in jerky motion. The use of 25 to 30 frames per second is generally sufficient to capture moving sequences for viewing on a mobile device, whilst a higher frame of 50 to 60 frames per second is generally required for larger display sizes (e.g. SDTV) to allow fast moving objects have smooth motion. When the trade-off between sampling resolution (both spatial and temporal) and data transmission rates was encountered during the design of early TV transmission standards, a solution termed interlacing was proposed<sup>3</sup>. In this scheme, only half of the frame data (even or odd lines) is transmitted every frame. The reduced data frame is termed an even or odd field depending on the line type that was sent. The scheme doubles the perceived frame rate without doubling the bandwidth. Although, this is not without disadvantages, as distortions are introduced. For the remainder of this thesis it can be assumed that non-interlaced video (also known as progressive video) is being used.

As previously mentioned, the RGB colour space is typically used during the sampling of a natural scene into the digital domain. In addition, it is also used for outputting digital images on Cathode Ray Tube (CRT) or Liquid Crystal Display (LCD) units. In the RGB colour space each component has an equal weighting. However, the human psychovisual system is more sensitive to brightness (luminance) than colour (chrominance). As a result a common processing step is to convert from the RGB colour space into the  $YC_bC_r$  colour space. The Y component represents luminance, and  $C_bC_r$  are the chrominance components. The benefit of this colour space conversion, is that the chrominance components can be subsampled, thus saving storage and/or transmission bandwidth. Video compression algorithms usually support 4:4:4, 4:2:2 and 4:2:0 luminance/chrominance sampling (see Fig. 2.2 for more details). The 4:2:0 sampling scheme is the most popular for video compression algorithms and results in little or no discernible loss in visual quality and has the benefit of reducing the data by a factor of two.

Regardless of the format (resolution, sampling scheme etc.) chosen, raw unencoded digital video requires enormous storage capacity and/or transmission bandwidth. For example, using

<sup>&</sup>lt;sup>3</sup>Another motivating factor for interlacing was due to the limited refresh speed of cathode ray tube based TVs of the era

the CIF format with 4:2:0 colour sampling and 25 frames per seconds requires:  $352 \times 288 \times 1.5$  bytes  $\times 25 = 3.6255$  MBps. Putting this into context, this low resolution format, which is only suitable for a mobile device, requires in excess of 13 gigabytes of storage for one hour of video. This bandwidth requirement is at odds with the characteristics of the target application i.e. extremely limited storage space available on mobile devices, limited bandwidth mobile communications and the relatively high cost of mobile communication data transmission services. As a further example, SDTV has a bandwidth requirement of 216Mbps, so without further processing, a DVD could hold little more than a few minutes of SDTV video. This clearly illustrates the need for efficient compression of video data. Fortunately, this can be achieved by exploiting the many inherent redundancies in the video data representation. The tools used in a video compression system are explained in the following subsections.

## 2.1.1 A Generic Video Compression System

There are a number of broad categories of inherent redundancies within a raw unencoded video data representation which can be exploited to achieve compression. These inherent data redundancies can be summarised as the following:

#### • Spatial Redundancies:

There is considerable redundancy between adjacent pixels, such as in large homogeneous coloured regions like a blue sky. In addition, colour transitions are typically gentle, reflecting the way they occur in the natural world.

## • Temporal Redundancies:

There is frequently little difference between consecutive frames of video unless considerable motion and/or a scene change has occurred. This can be exploited by only coding and transmitting those regions within the frame which have changed.

#### • Statistical Data Redundancies:

Some symbols used within the video compression system have a higher probability of occurring than others. Rather than employ an equal word length for all the symbols, if a shorter word length is used for more frequently occurring symbols, an overall reduction in data can be achieved. Morse code is a classical non-video example of where statistical redundancies in a data distribution is used to reduce the bandwidth.

## • Properties of human visual system:

As previously mentioned, the human visual system is more sensitive to luminance than colour. This is typically exploited by subsampling the chrominance component. In addition, the human visual system is less sensitive to areas of high frequency e.g. sharp colour transitions.

Ideally the compression algorithm applied to the inherent video data redundancies at the encoder would be perfectly reversible at the decoder. This type of compression is known as *Loss-less*. Lossless compression is vital for example in computer file compression algorithms, where any loss/corruption would destroy the overall message. Whilst lossless video compression algorithms<sup>4</sup> exist, the compression achievable is small, typically in the order of 2-4x [35]. With the exception of a small number of applications in niche areas<sup>5</sup>, this rate of compression is insufficient due to the sheer quantity of video data. Fortunately, from a compression perspective, a perfect reconstruction at the decoder is not always necessary. In many applications, the eye can tolerate a loss. This form of compression is termed *Lossy*, since information is lost during the compression process. The challenge then becomes one of balancing compression efficiency (i.e. size of the resultant bitstream) versus acceptable visual quality for a given application. In the case of mobile applications, it may also be tolerable to accept reduced visual quality for reduced computational complexity in order to improve the real-time performance and/or power efficiency reasons.

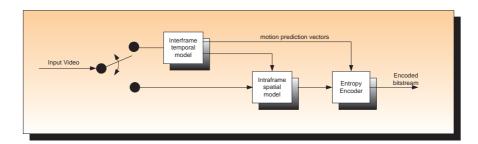

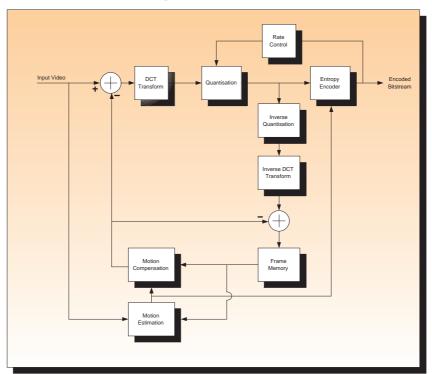

Mainstream video compression algorithms use a combination of interframe and intraframe coding for both lossless and lossy compression (see Fig. 2.3(a)). Intraframe coding exploits spatial and perceptual redundancies and is coded without reference to other frames. Interframe coding exploits temporal redundancies by using previous (and sometimes future) frames. In both cases, further processing, known as entropy coding, is used to exploit the statistical data redundancies. This general video compression framework is typically known as a *hybrid video codec* and is the basis of all modern video compression systems. Fig. 2.3(b) and Fig. 2.3(c) show the principal constituent elements of a generic hybrid encoder and decoder in greater detail. These elements are explained in the subsequent subsections.

<sup>&</sup>lt;sup>4</sup>Zero mathematical loss of visual quality at the decoder

<sup>&</sup>lt;sup>5</sup>Such niche area applications include compression of video data bus transfers and intermediate storage of video in production studios where quality is imperative

(a) A Simplified Model of a Video Encoder

(b) A Generic Hybrid Video Encoder

(c) A Generic Hybrid Video Decoder

Figure 2.3: A Generic Video Encoder and Decoder

#### 2.1.1.1 Motion Estimation & Compensation

There is typically only a very slight change between successive frames in video. For example, Fig. 2.4(a) and Fig. 2.4(b) show temporally adjacent frames from a test sequences. A temporal prediction model at the encoder & decoder can exploit this redundancy and will provide compression provided the model parameters and any correction terms are less than the raw pixel information. As can be seen in Fig. 2.4, if frame one is subtracted from frame two, the residual energy (shown scaled in Fig.2.4(d) for ease of viewing) contains considerably less detail. It is reasonably intuitive that the residual frame will require less data bandwidth than the original frame 2. In fact, the entropy<sup>6</sup> of the original frame two is 7.15 bits/pixels, whereas that of the temporal prediction residual is 4.38 bits/pixels. In the previous example the temporal prediction model was the most basic available, that is simple frame differencing. More complex temporal models can reduce the entropy further by more accurately capturing the interframe temporal behaviour, which can be attributed to a combination of camera motion & object motion. However, for practical implementation purposes the choice of temporal prediction model is also a trade off between complexity, memory requirements and prediction performance.

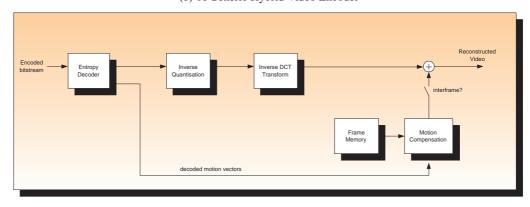

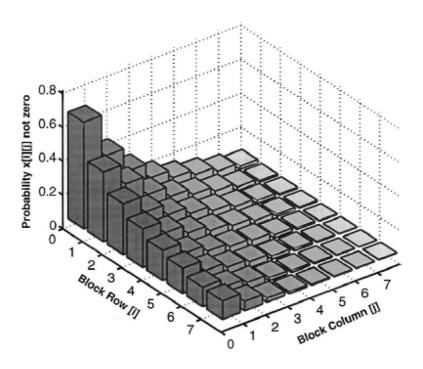

A generic temporal prediction model can be considered to consist of *Motion Estimation* and *Motion Compensation*. Motion estimation attempts to establish the motion that has occurred between frames, whilst motion compensation uses the motion vectors generated from the motion estimation process to retrieve the predicted block. There are two main approaches used commonly for motion estimation, gradient descent based algorithms and block-matching algorithms (see Fig. 2.5). Of these, the block matching approach gives acceptable prediction performance whilst using less computational resources when implemented in either software or hardware. The block based algorithm examines each  $M \times N$  block in the current frame and finds the associated best matching block within a predetermined or adaptive  $\pm S$  pel search range in a reference frame(s). Motion compensation uses the motion vector associated with the best match to retrieve the appropriate block, which is then subtracted from the current block to generate a prediction residual. The prediction residual is then used in subsequent processing. A subtle point that should be noted is that since differences will likely exist (i.e. due to the lossy process) between the "real" previous frame and the decoded previous frame in the decoder, the motion estimation/compensation process does not use the real previous frame but rather uses the decoded frame in the encoder (see Fig. 2.3(b)).

It is also worth emphasising the fact that block based algorithms estimate the motion of a group

<sup>&</sup>lt;sup>6</sup>Entropy is a measure of the amount of information content in an information source

(a) Frame 1

(b) Frame 2

(c) Frame Difference

(d) Scaled Frame Difference

Figure 2.4: Temporal Redundancy in Video Sequences

Figure 2.5: Motion estimation taxonomy

of pixels. This generally works quite well, as semantic objects are generally much larger than the typical range of block sizes, thus frequently the block based motion estimation algorithm generates a motion field that is relatively consistent with the trajectory of an object. The block size leads to certain characteristics of the resultant motion vectors and prediction residual. A small block size can give very good prediction results, but is also likely to get caught in local minima which are not consistent with the true motion of the object. Although in video compression, establishing the true motion is a secondary concern compared to energy minimisation of the prediction residual. In contrast, in other video processing applications<sup>7</sup> the true motion is of principal importance. A further issue with a smaller block size is that there is also an increased computational complexity cost in the motion estimation algorithm. However, it could be argued that the greatest issue with smaller block sizes for video compression is that they require a greater number of motion vectors to be added to the bitstream. So although the prediction residual may have less energy, this is counter balanced by the increased bits required to store the motion vectors. The alternative option of using a large block matching size is also not without disadvantages. For example, on occasions it lacks the resolution necessary for complex motion fields in highly detailed blocks (e.g. a block containing the edges of two or more objects moving in differing directions). This issue of block

<sup>&</sup>lt;sup>7</sup>For example, in frame rate conversion for HDTV decoders (i.e. 50/60 Frames Per Second (FPS) to 100/120 FPS) inaccurate motion vectors lead to poor interpolation results with highly objectionable artifacts.

Figure 2.6: Block sizes used in H.264 motion estimation)

size is addressed in newer video compressions standards (MPEG-4 and to a greater extent MPEG-4 part 10 / H.264) through the use of variable block size. H.264 uses a Lagrange optimisation to establish the optimum trade off between a range of block sizes (see Fig. 2.6), the quality of the prediction residual and the cost of the motion vectors.

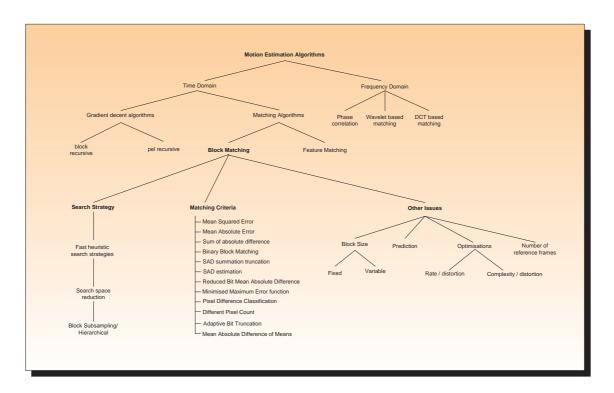

There are principally two constituent elements in a block matching algorithm; the block matching routine and the search strategy. The search strategy finds appropriate candidate blocks within a search window, whilst the block matching evaluates a distortion metric (level of similarity) between each candidate block in the search window and the current block in the current frame. The search strategy and block matching typically operate on just the luminance component, with resultant motion vectors scaled for the chrominance blocks according to the chrominance subsampling strategy employed. A wide variety of matching criteria can be used, these include Mean Squared Error (Eqn. 2.1), Mean Absolute Differences (Eqn. 2.2), Sum of Absolute Differences (SAD) (Eqn. 2.3), Binary Block Match (Eqn. 2.4), SAD summation truncation, SAD estimation, Reduced Bit Mean Absolute Difference, Minimised Maximum Error function [32]. The matching criteria is a complexity/prediction performance trade off and represents a vital computational complexity decision as the distortion metric is typically inside deep inner loops of search strategies. For example, in the case of binary valued pixels (single bit representation as opposed to 8 bits) the SAD calculation is simplified. This allows the subtraction operation in Equation 2.3 to be replaced by a single bit XOR, since the difference between two pixels will be either 0 or 1. The absolute

function is also implicit in the XOR function, because the XOR cannot give a negative result. The operation reduction coupled with less data (1 bit instead of 8 bits per pixel, generated through a binarisation/quantisation process) is beneficial from the point of view of computational complexity. However, the lack of pixel value granularity typically leads to degradation in the quality of the motion vectors, which causes the prediction residual to have more energy. Many distortion metrics were evaluated by Kuhn in terms of image quality (PSNR) and implementation results (area, throughput, power) [32]. He found that the SAD metric gave the optimum trade off between complexity and efficiency/quality.

$$MSE(B_{curr}, B_{ref}) = \frac{1}{M \times N} \sum_{i=1}^{i=M} \sum_{j=1}^{j=N} (B_{curr}(i, j) - B_{ref}(i, j))^{2}$$

(2.1)

$$MAD(B_{curr}, B_{ref}) = \frac{1}{M \times N} \sum_{i=1}^{i=M} \sum_{j=1}^{j=N} |B_{curr}(i, j) - B_{ref}(i, j)|$$

(2.2)

$$SAD(B_{curr}, B_{ref}) = \sum_{i=1}^{i=M} \sum_{j=1}^{j=N} |B_{curr}(i, j) - B_{ref}(i, j)|$$

(2.3)

Binary SAD

$$(B_{curr}, B_{ref}) = \sum_{i=1}^{i=M} \sum_{j=1}^{j=N} (B_{curr}(i, j) \otimes B_{ref}(i, j))$$

(2.4)

In Eqn. 2.1 to Eqn. 2.4,  $B_{curr}$  is the block under consideration in the current frame and  $B_{ref}$  is the block at the current search location in the search frame. The block size is  $M \times N$ .

Once the distortion metric is calculated between the current block and reference block, the process repeats until all of the search positions defined by the search strategy within the search window are examined. The block match which gave the minimum distortion metric is deemed to be the most suitable match and used for subsequent processing. There are a wide variety of search strategies that can be used. The choice is typically a complexity/performance trade off, with the following being the broad options available [32]:

# • Exhaustive full search algorithm

This searches every position within the search window and as such always gives the best results, but it is also very computationally expensive. However, the regularity of the search positions is suitable for hardware.

# • Fast exhaustive search

This search strategy eliminates non-optimal search positions while maintaining optimal mo-

tion vectors through early termination of distortion metric calculations. Sometimes this process is called a SAD step cancellation search strategy.

## • Fast heuristic / logarithmic search strategies

This approach uses the assumption that the distortion metric monotonically increases moving away from the minimum point to reduce the number of search positions. However, there is the distinct possibility of this search strategy getting stuck in a local minimum, which in turn yields a higher energy prediction residual. The three step search is an example of this approach.

#### • Hierarchical or multi-resolution search strategies

An initial search takes place in a low resolution version of image, progressively higher resolution searches take place in the parts which exhibit the best promise. Again this approach reduces the number of search positions relative to the full search and compared to the logarithmic search strategies, the hierarchical nature can help to avoid local minima due to a low pass filtering effect. However, local minima issues are still possible for small regions which disappear during the sub-sampling process.

## • Zone based search strategies

These search strategies employ numerous stopping thresholds, which can be advantageous in a rate/distortion sense. For example, a spiral search coupled with multiple thresholds defined for different search radii could terminate calculations early if one of the predetermined thresholds was reached.

## • Motion vector prediction and dynamic search window size

These two techniques can be applied to most search strategies. A prediction of the motion vector can be used to seed the search strategy. In the ideal case, if the prediction is accurate enough (i.e. below a specified threshold), no further processing is required. Otherwise a conventional search is carried out around the motion vector predictor. If for example, a logarithmic or zone based search strategy is then used, the motion vector prediction is still likely to reduce the overall number of operations necessary to give a satisfactory result and/or improve the quality of the prediction residual. In a similar fashion, a dynamic search window can be used to reduce the number of operations by constraining the search window in areas of predicted low motion. Typically spatial and/or temporal correlation methods are used to estimate the motion vector predictor and search window size.

#### 2.1.1.2 Transform Coding

Most mainstream video compression systems use transform-based algorithms, which literally transform the spatial information (i.e. the pixels or a motion compensated prediction residual) into an alternative representation which is more amenable to compression. This alternative representation is almost always in the frequency domain. Whilst both the spatial and transform domain are equivalent, spatial redundancies and the sensitivities of the human visual system can be more easily exploited in the frequency domain. This is because energy in a natural scene is concentrated in low frequencies and in addition the eye also has greater sensitivity to lower frequency content. Therefore, once the spatial data is transformed into the frequency domain, subsequent processing can direct greater coding resources to those frequencies which are the more perceptually important.